Automating C Test Generation for Comprehensive Embedded SoC Verification

SoC designs are becoming increasingly complex, yet many system‑level verification test suites still consist of thousands of hand‑written lines of C code—an antiquated approach that contradicts the principle of automation. In particular, C tests executed on embedded processors to validate the entire device before fabrication remain largely manual.

Automating test creation boosts productivity across SoC development stages. Constrained‑random methods in a UVM testbench generate scenario‑specific random vectors, improving coverage at the block level. However, the design remains a black box, with stimulus, checks, and coverage code written separately—a cumbersome and error‑prone process for large blocks.

Extending these methods to the system level is challenging because they must integrate processor test code with I/O transactions, typically executed on emulators or prototypes. Full SoC verification requires exercising the processors themselves, but UVM and other constrained‑random techniques generally omit processor code. In practice, UVM is applied to the SoC by replacing processors with virtual I/O, leaving the subsystem minus the processor under test.

Acknowledging the shortcomings of constrained‑random testbenches, engineers resort to hand‑writing C tests that run on processors in both simulation and hardware emulation. However, these platforms cannot support a full OS; tests run in bare‑metal mode, increasing composition effort. Coordinated multi‑core, multi‑thread execution is rare, so critical behaviors—concurrency and coherency—receive limited verification.

Automatically generating C testsAutomated C test generation frees engineering time and expands coverage. Generated test cases cover more of the SoC’s functionality than hand‑written ones, uncovering difficult corner cases. Multi‑threaded, multi‑processor tests exercise all parallel paths, validate concurrency, stress memory coherency, and synchronize with I/O transactions. As a result, system‑level functional coverage routinely exceeds 90%, far surpassing traditional approaches.

The test generation tool—Test Suite Synthesis—leverages a clear, graph‑based scenario model that encapsulates the intended design behavior. Engineers can author these models in native C++ using the Accellera Portable Stimulus Standard or visually, mirroring conventional chip data‑flow diagrams typically sketched on a whiteboard during design discussions.

Each model encapsulates stimulus, checks, coverage metrics, and debug data, giving the generator all information required to produce high‑quality, self‑checking C tests that exercise every design aspect. Hierarchical, modular models enable block‑level tests to be reused wholesale in full‑SoC models and shared across teams and projects. The synthesis tool decomposes a single intent model into concurrent tests spanning threads and I/O ports, ensuring tight synchronization.

Advantages test suite synthesisA key benefit of test suite synthesis is the ability to set coverage goals at the intent‑model level. After specifying intent, the tool analyzes it to estimate the number of test cases required and the expected functional coverage.

In a typical SoC, thousands of tests can be generated. By constraining the intent, engineers can target specific coverage goals and concentrate the tool on critical areas. This eliminates the tedious iterative cycle of setting tests, running verification, assessing coverage, and reconfiguring.

A case study on a large SoC from a leading semiconductor firm demonstrated a 80% reduction in test composition time compared with handwritten tests. Automation generated more rigorous cases, boosting coverage from 84% to 97%. The models proved portable across environments.

A single intent model can produce test cases for virtual platforms, RTL simulation, emulation, FPGA prototypes, or even the manufactured chip during post‑silicon validation.

Debugging remains a major time sink at the SoC level. When a test uncovers a defect, engineers need to trace the failure back to the originating test and the underlying scenario model. By correlating each test case to its graph representation, modular, self‑contained tests enable rapid isolation and analysis of bugs.

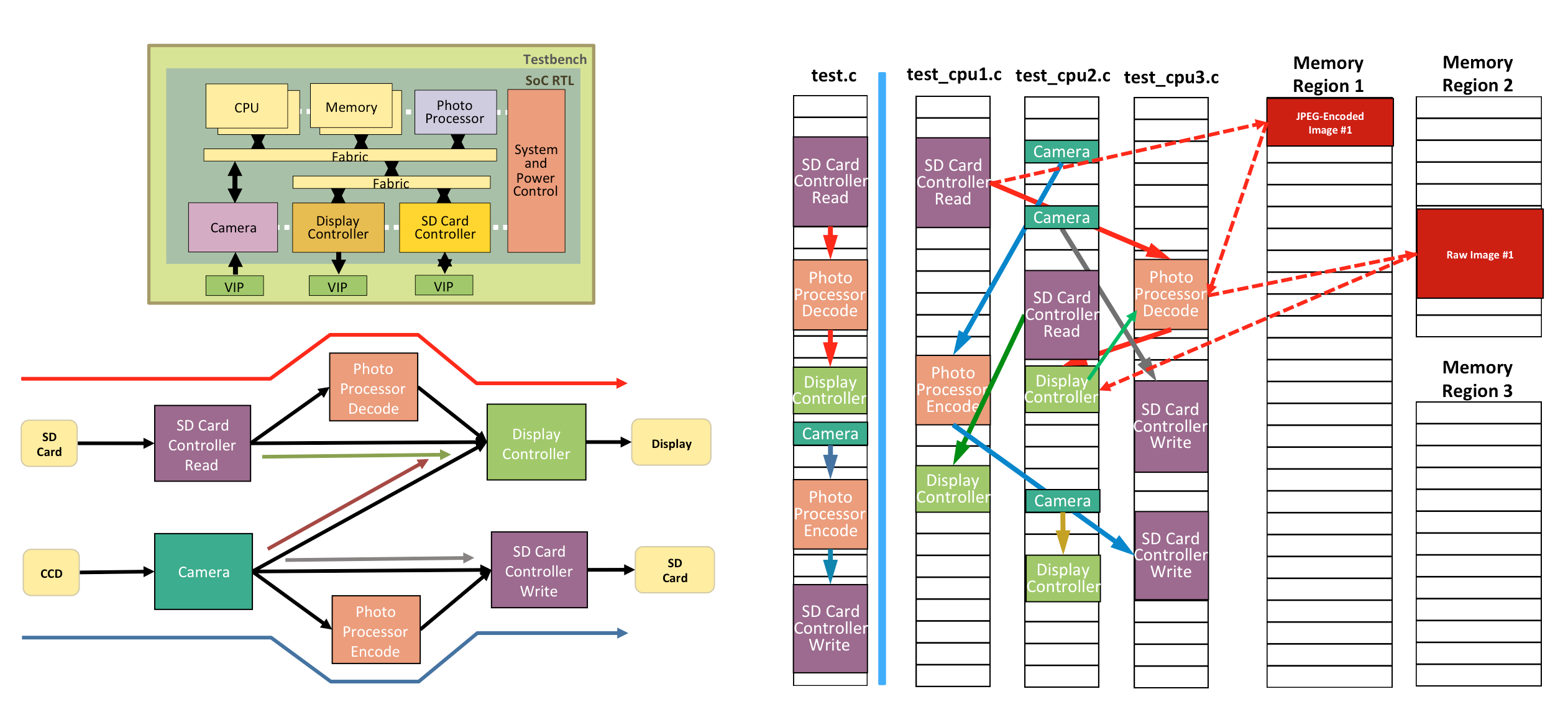

Application scenariosSynthesized test cases can drive realistic use‑case scenarios. For instance, consider the digital camera SoC illustrated in Figure 1.

click for larger image

Figure 1: Image Processing SoC Example. (Source: Breker Verification Systems)

The SoC’s block‑level components comprise two processors, peripheral devices, and memory. A simplified graph beneath the block diagram illustrates the high‑level paths for verification. One scenario—depicted in the top path—reads a JPEG from an SD card, routes it to the photo processor via a memory region, transforms the image for display, loads it into a second memory block, and finally sends it to the display controller. Each high‑level block is hierarchical, containing numerous actions and decisions.

The synthesis tool schedules randomized tests accordingly. In its simplest form, tests execute sequentially in a single thread, as illustrated. The true power emerges when the tool interleaves applications across multiple threads and processors, running as many concurrent instances as the design allows and allocating memory in complex patterns. An alternative view in the figure shows tests distributed across three threads, leveraging diverse memory regions.

While the illustration is high‑level, the synthesis tool actually flattens the hierarchical graph into thousands of actions and connections, incorporating randomized decisions that pass through a solver algorithm. As the graph traverses, AI planning algorithms analyze desired outputs and refine input tests for optimal alignment. The tool also provides OS‑like services—memory allocation, address map access, interrupt handling—to support complete test structures, then schedules tests randomly while allocating storage and resources accordingly.

ConclusionJust as constrained‑random testbenches removed manual effort from block verification, synthesized test content for embedded‑processor SoCs has proven to cut system‑level verification effort. The approach now extends to block‑level verification and post‑silicon validation. Automated C tests embody the principle of “automate whenever possible,” delivering dramatic coverage gains and compressed verification schedules.

Embedded

- Embedded Systems Fundamentals & Real-World Applications

- Great Wall Motors Integrates Ambarella CV25AQ AI Vision SoC in New WEY Mocha SUV

- Analog Devices Showcases AI, Industrial Networking, and Power Solutions at Embedded World 2019

- Optimizing AI Models for Efficient Embedded Deployment

- IBASE CMI300‑988: Ultra‑Compact Mini‑ITX PC with AMD Ryzen Embedded V1807B

- Axiomtek Launches Fanless eBOX100-51R-FL: Ultra‑Compact, Intel‑Powered Edge Computing Solution

- TRITON‑TX8M: A Cost‑Effective Quad‑Core SoM for 64‑bit Embedded Systems

- Metal Identification Explained: Essential Tests & Tips for Accurate Recognition

- Embedded Systems 101: A Beginner's Quick Reference

- Should You Automate Your Laser Cutting System? A Strategic Guide for Success