Minterm vs Maxterm: A Comprehensive Guide to Karnaugh‑Map Simplification

In digital logic design, we often simplify Boolean expressions to reduce gate count and improve performance. While most textbooks focus on Sum‑of‑Products (SOP) solutions, every SOP has a complementary Product‑of‑Sums (POS) form that can be more advantageous for certain logic families.

Understanding Minterms

A minterm is a Boolean product that yields 1 for a single input combination and 0 for all others. In a Karnaugh map (K‑Map) or truth table, the minterm appears as a single “1” surrounded by zeros. For example, the minterm ABC corresponds to the K‑Map cell 111, while A'BC' corresponds to cell 010.

When mapping minterms, follow these steps:

- Identify the product term to be mapped.

- Convert the term to its binary equivalent.

- Place a 1 in the K‑Map at the address indicated by that binary value.

- Repeat for each product term in the SOP expression.

Once all minterms are plotted, group the 1s into the largest possible blocks of 1, 2, 4, 8, … cells (powers of two). Each block corresponds to a product term in the simplified SOP expression. The binary value of the block is converted back to a product term by replacing 1s with the true variable and 0s with the complemented variable.

From Minterms to SOP

The SOP reduction follows a straightforward procedure:

- Form the largest groups of 1s covering all minterms.

- Write the binary value for each group.

- Convert the binary value to a product term.

- Sum all product terms to obtain the simplified SOP expression.

Understanding Maxterms

A maxterm is the dual of a minterm. It yields 0 for a single input combination and 1 for all others. In a K‑Map, a maxterm appears as a single “0” surrounded by ones. For instance, the maxterm (A+B+C) is represented by the K‑Map cell 000 because only the combination (0,0,0) makes the OR expression false.

To place a maxterm on a K‑Map, use the following steps:

- Identify the sum term to be mapped.

- Convert it to its binary representation.

- Take the complement of that binary value.

- Place a 0 in the K‑Map at the address indicated by the complemented value.

- Repeat for each sum term in the POS expression.

From Maxterms to POS

POS reduction mirrors the SOP process but operates on the 0s:

- Form the largest groups of 0s covering all maxterms.

- Write the binary value for each group.

- Complement the binary value.

- Convert the complemented value to a sum term.

- Multiply all sum terms to obtain the simplified POS expression.

Practical Example: POS Simplification

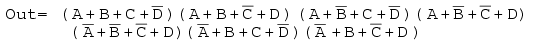

Consider the Boolean expression to be simplified into POS form:

Procedure:

- Map the seven maxterms as 0s on the K‑Map, complementing the input variables to locate each cell.

- Group the 0s into the largest possible blocks (powers of two).

- For each group, write the binary address, complement it, and convert to a sum term.

- Multiply all sum terms to form the final POS expression.

Following this method yields the POS expression with the minimal number of gates.

Practical Example: SOP from a POS Expression

Given a POS expression, the SOP can be derived by:

- Mapping the maxterm 0s onto the K‑Map.

- Filling the remaining cells with 1s.

- Grouping the 1s and converting each group to a product term.

- Summing all product terms to produce the SOP form.

The SOP and POS versions can be compared in terms of gate count and input complexity to determine the most cost‑effective implementation for a specific logic family (TTL vs CMOS).

Implementing with TTL Gates

When using TTL devices, NAND gates are the most readily available building blocks. By applying De Morgan’s theorem, an SOP expression can be converted to a NAND‑NAND structure:

- Replace every AND gate with a NAND gate.

- Replace the final OR gate with a NAND gate and shift the inverters to the inputs of the preceding NANDs.

- Tie unused inputs of NANDs to logic high.

- Label each gate (U1‑a, U1‑b, etc.) and assign pin numbers according to the data sheet.

This approach yields a hardware design that is efficient for TTL families while preserving logical equivalence.

Designing the Physical Circuit

Once the logical design is finalized, a schematic can be drafted using standard TTL packages:

- 7404 – Hex inverter (U1)

- 7432 – Quad OR gate (U2)

- 7408 – Quad AND gate (U3)

- 7420 – 4‑input NAND gate used as a 4‑input OR by inverting inputs.

Label each gate with a unique identifier and pin assignment, then use a printed circuit board (PCB) for mass production. Ground unused inputs and ensure proper decoupling to maintain signal integrity.

Conclusion

By mastering the mapping of minterms and maxterms onto Karnaugh maps and understanding the dual nature of SOP and POS forms, designers can choose the most efficient implementation for their target technology. Whether working with TTL or CMOS, the principles outlined above provide a reliable foundation for logic synthesis and hardware realization.

Industrial Technology

- Differential Equations: Solving for Functions, Not Numbers

- pH Measurement: Fundamentals, Electrodes, and Best Practices

- Industry 4.0 Insights: Q&A with Bosch.IO’s Verena Majuntke on IoT, Automation, and the Future Factory

- Choosing the Right Conference Calling Solution for Your Office

- AC-DC Converters: Your Reliable Source for Consistent DC Power

- UGIPURE® 4472 – Premium Solution‑Annealed Nitrogen‑Alloyed Stainless Steel for Surgical Implants

- UGIMA®-X 4305: Premium Solution-Annealed Stainless Steel with Superior Machinability

- UGI® 316Ti Stainless Steel – High‑Temperature, Non‑Magnetic, Solution Annealed

- UGIPERM® 12FM Solution-Annealed Stainless Steel – High Permeability, Low Coercivity

- UGIMA® 4598 – Solution‑Annealed 316L Stainless Steel with Enhanced Machinability