Pre‑Silicon Software Development: Accelerating Time‑to‑Market with SoC Emulation

In today’s fast‑moving technology era, the most common approach for meeting market demands is the system‑on‑chip (SoC). A SoC is a single integrated processor core surrounded by specialized accelerators and extensive I/O that support the peripherals it powers.

Since the mobile‑data boom of 2002, SoCs have become indispensable for enabling the core features that define smartphones. The same trend now drives their ubiquity in “smart” consumer devices—smart TVs, connected cars, and the rapidly expanding Internet‑of‑Things (IoT) ecosystem.

The soaring demand for SoCs has turned the market into a highly competitive arena. In response, designers are building more complex devices, continuously evolving peripheral families, and shrinking the window between design and launch. To keep pace, software must be available as early as possible and must be robust enough to avoid costly post‑tape‑out fixes.

Traditionally, SoC software teams waited for the first silicon sample before starting development. The arrival of a silicon prototype would trigger a short, intense bring‑up sprint where developers from around the world converged to validate drivers and interfaces. Even with this aggressive schedule, the software typically required months—sometimes years—to reach production readiness, leaving little confidence before mass‑production could commence.

With SoC designs growing in size and complexity, the gap between silicon availability and production‑ready software can stretch into several years. The rapid evolution of peripheral families—audio, video, USB, Ethernet, etc.—also creates expertise gaps that must be bridged by hiring specialists, further inflating costs and timelines.

To deliver reliable software earlier, the industry is adopting a “shift‑left” philosophy: start development concurrently with the hardware design. Pre‑silicon development not only accelerates the software pipeline but also exposes design‑level bugs, allowing costly mask tape‑outs to be avoided.

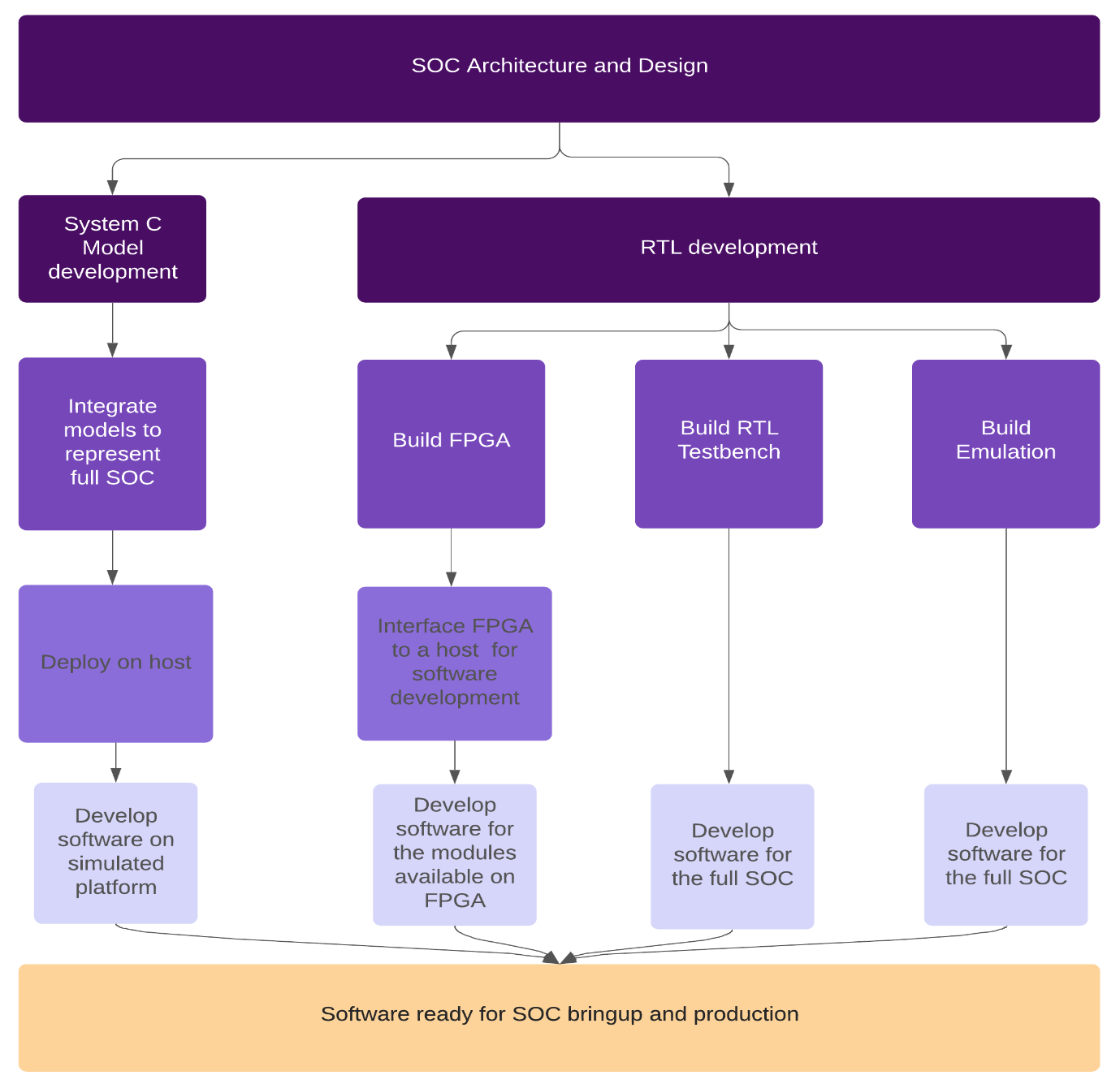

Pre‑silicon Development Strategies

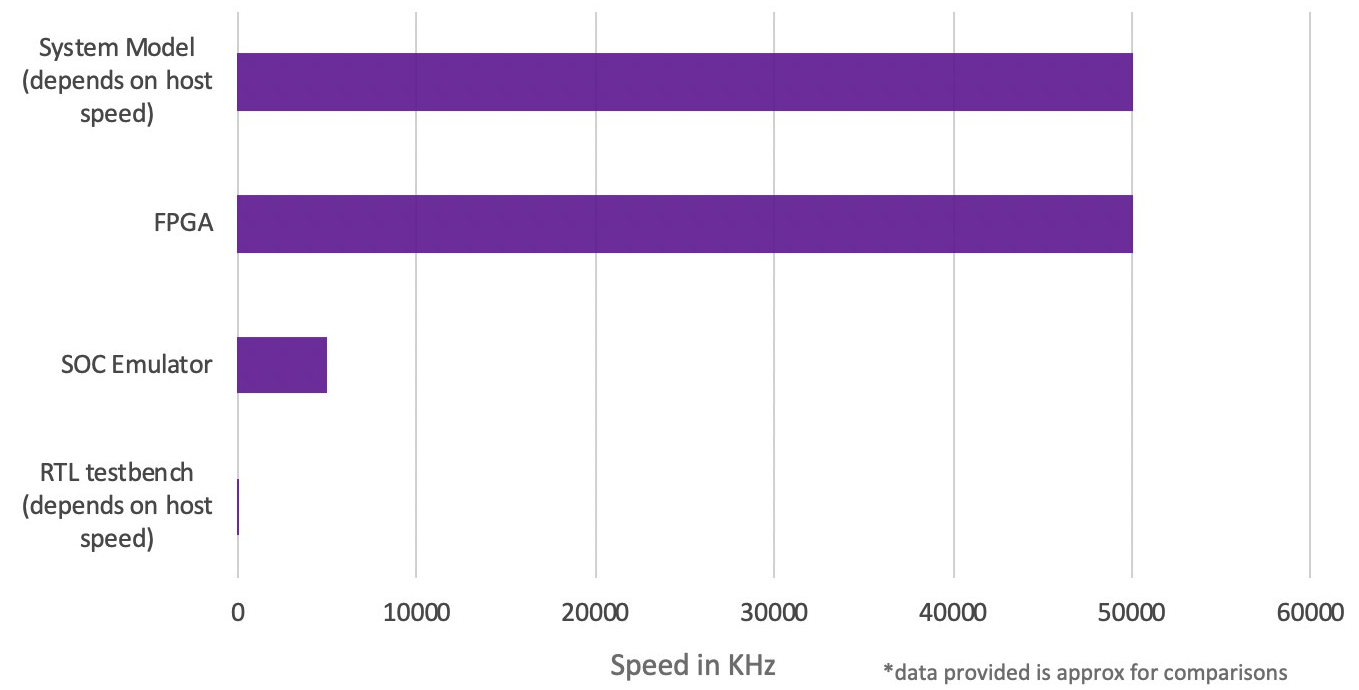

Software can begin before tape‑out using several techniques: software prototyping, RTL testbenches, FPGA prototypes, and, most effectively, full‑system emulation. Each method focuses on a specific abstraction level and comes with its own trade‑offs.

System‑C Behavioral Models

Creating a System‑C model for every IP block lets developers write and test drivers in isolation. However, the effort to model every peripheral accurately is substantial, requiring a dedicated team that can quickly outgrow project budgets. Moreover, behavioral models rely heavily on the modeler’s interpretation; any mismatch between the design intent and the model can lead to subtle bugs that are expensive to diagnose later.

RTL Testbench

RTL testbenches, built from the same Verilog or VHDL used for verification, provide cycle‑accurate simulation of the entire SoC. They stay in lockstep with the hardware design, ensuring the most up‑to‑date representation. The downside is speed: a cycle‑accurate simulator is orders of magnitude slower than real hardware, making driver development a slow, month‑long process that can negate the benefits of early starts.

FPGA Prototypes

Modern FPGAs are now capable of synthesizing entire IP blocks from RTL, delivering cycle‑accurate behavior at a fraction of the simulation time. By mapping each peripheral onto a separate FPGA, developers can write and debug drivers quickly. The trade‑off is that the full SoC integration—how blocks communicate and share resources—is missing, limiting the depth of validation and leaving integration‑level issues to surface only after silicon is available.

SoC Emulators

SoC emulators represent the most balanced approach. Built on the same RTL as the silicon, they offer cycle‑accurate performance while running 100× faster than Verilog testbenches. This speed enables full OS porting, driver development, and system‑level testing within weeks rather than months.

Emulators also support a wide array of peripherals—UART, I²C, display controllers, PCIe, Ethernet, Wi‑Fi, cameras, sensors—allowing developers to emulate an entire development board. Software can be debugged with standard JTAG tools, and real or virtual devices such as NAND flash can be attached, providing a realistic environment for ROM, OS, and firmware validation.

Beyond early development, emulators shine during post‑silicon debugging. Because they run the same OS and drivers as the final product, engineers can replicate silicon‑level issues on the emulator, analyze signal‑level traces, and verify fixes before the silicon reaches the field.

In comparative studies, emulators consistently outperform System‑C models, RTL testbenches, and FPGA prototypes in terms of speed, coverage, and cost‑effectiveness. While the upfront investment in an emulator platform may seem high, the savings in reduced time‑to‑market and risk mitigation often outweigh the cost.

According to Moore’s Law, transistor counts double roughly every two years, pushing 64‑bit ARM‑based SoCs today toward 100–300 million logic gates. In this environment, only a full‑system emulator can scale to meet the demands of modern SoC software teams.

References

- Trimberger, Stephen M. “Three Ages of FPGAs.” IEEE Xplore Full‑Text PDF: 2015, https://ieeexplore.ieee.org/stamp/stamp.jsp?arnumber=7086413.

- Brunet, Jean‑Marie. “Why Modern SoC Designs Embrace Emulation.” Embedded Computing Design, 5 Sept. 2018, https://embedded-computing.com/embedded-computing-design/why-modern-soc-designs-embrace-emulation.

- “Soc Emulation.” Soc Emulation, 2019, https://www.aldec.com/en/solutions/hardware_emulation_solutions/co-emulation-soc-emulation.

- “Cramming More Components onto Integrated Circuits.” https://www.cs.utexas.edu/, 2006, cs.utexas.edu/~fussell/courses/cs352h/papers/moore.pdf.

Embedded

- SOAFEE: A Cloud‑Native Architecture Empowering Software‑Defined Automotive Platforms

- MeasureWare: ADI’s All‑In‑One Precision Measurement Platform for Hardware Kits and Software Tools

- Microchip Unveils Affordable $500 RISC‑V FPGA Development Kit

- Master Lean Software Development: A Practical Guide for Raleigh CTOs in 2022

- Custom Healthcare Software Development 2024: The Definitive Guide to Launching Your Project

- Custom Software Development 2022: A Strategic Guide for Raleigh C‑Suite Leaders

- Why Software Products Outperform Custom Development

- Accelerating Innovation: Automating Software Development for Competitive Edge

- Accelerate In‑House App Development with Low‑Code & No‑Code Platforms

- ABB Laser Cutting Software: Space‑Saving, Time‑Efficient Solutions