Synchronizing Asynchronous Resets in ASICs and FPGAs: Challenges, Best Practices, and Advanced Solutions

In modern VLSI designs, a reliable reset mechanism is essential for establishing a known start‑up state. This article examines the coordination challenges between asynchronous resets and synchronous clocks, and presents proven strategies for both ASIC and FPGA environments.

Asynchronous resets are widely used to bring synchronous logic to a defined state immediately after power‑on, without waiting for a clock edge. However, their release must be carefully timed with the system clock to avoid metastability and intermittent failures—issues that become acute in large, multi‑clock‑domain designs.

We review the core requirements for asynchronous resets, critique traditional synchronization and distribution methods, and introduce advanced techniques that offer faster, simpler, and more reliable convergence. Separate sections detail ASIC‑specific and FPGA‑specific best practices, along with illustrative special cases.

Part 1 (this article) outlines the key issues; Part 2 expands on ASIC and FPGA solutions, and Part 3 presents additional use‑case insights.

1. Asynchronous Reset Challenges

Digital VLSI systems typically include a reset to ensure predictable behavior. Reset can be implemented either synchronously—requiring an active clock—or asynchronously—requiring none. Synchronous reset introduces deterministic latency and avoids metastability, but can affect data‑path timing. Asynchronous reset offers lower latency and can use dedicated flip‑flop inputs, yet it presents several drawbacks:

- Potential metastability in flip‑flops during reset release.

- Need for direct accessibility to support DFT.

- Susceptibility to Single‑Event Transients in rad‑hard applications.[1]

While the debate over synchronous versus asynchronous resets continues,[2] this discussion focuses on resolving asynchronous‑reset issues. Many of the techniques described apply to both reset types.

Typical asynchronous‑reset drivers include external ports, power‑supply RC networks, watchdog timers, manual reset buttons, and external masters such as microprocessors. In some scenarios—e.g., designs without an active clock at power‑up or low‑power power‑on sequences—an asynchronous reset is mandatory.

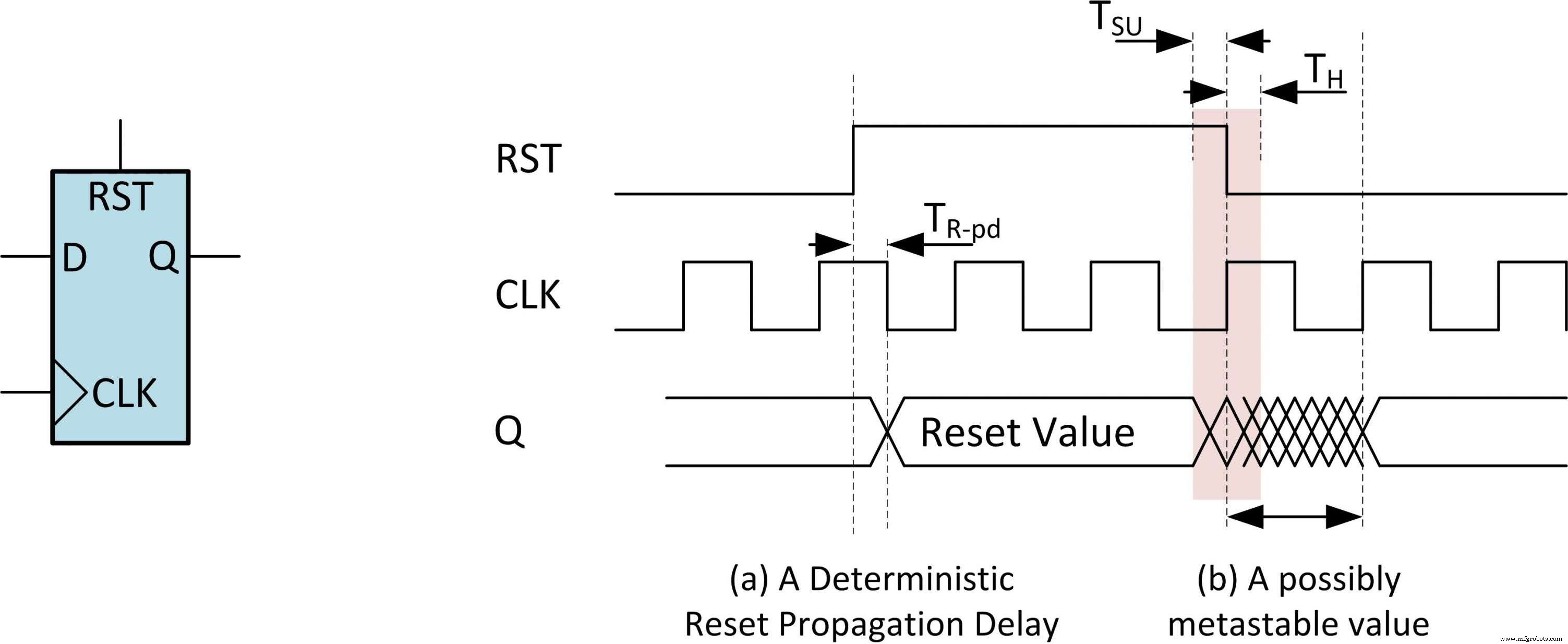

Although reset assertion can ignore clock timing, the release must be synchronized to the clock to satisfy setup and hold requirements. A violation can cause metastability and design failure. Figure 1 illustrates an active‑high asynchronous reset: (a) assertion clears the flip‑flop output Q regardless of CLK; (b) improper release timing can trigger metastability similar to data‑path violations.

click for larger image

Figure 1: Active high asynchronous reset assertion and release. (a) Reset assertion (b) Release with timing violation. (Source: vSync Circuits)

Embedded

- Mastering OTA Updates: 5 Common Challenges & Proven Solutions for Industrial IoT

- Mastering USB‑C: Design Challenges and Practical Solutions for High‑Speed Data and Power

- Mastering Asynchronous Reset Synchronization in ASICs and FPGAs

- Anvo‑Systems and Mouser Forge Global Distribution Partnership

- Reactive Maintenance: Common Challenges, Proven Solutions, and the Path to Proactive Asset Management

- Key Challenges & Proven Solutions for Furniture Manufacturers

- Enhancing Industrial Performance: Overcoming Monitoring Challenges with IoT & Analytics

- Metal 3D Printing: Overcoming Key Challenges & Harnessing Emerging Solutions

- Industrial IoT Security: Overcoming Challenges and Implementing Robust Solutions

- Revolutionizing Automotive Production: Overcoming Manufacturing Challenges with IoT Solutions