Ultra‑Low Specific On‑Resistance LDMOS with Enhanced Dual‑Gate and Partial P‑Buried Layer

Abstract

We present a lateral double‑diffused MOS (LDMOS) transistor that achieves an unprecedented specific on‑resistance (Ron,sp) of 8.5 mΩ·mm² while delivering a 43 V breakdown voltage (BV). The device incorporates an enhanced dual‑gate architecture, formed by a highly doped N‑buried layer beneath the P‑well, and a strategically designed partial P‑buried layer under the N‑drift region. These innovations reduce the channel resistance (Rc) and mitigate vertical electric‑field peaks, respectively, yielding a 37 % improvement in on‑resistance relative to our prior designs. The analytical on‑resistance model and detailed simulation data confirm the trade‑off between Ron,sp and BV, guiding the optimization of doping concentrations and layer geometries.

Background

Modern analog power ICs demand transistors with both low on‑resistance and high breakdown voltage. For LDMOS devices, the drift region traditionally dominates the resistance–voltage trade‑off [1–20]. In our previous work, an ultra‑shallow trench isolation (USTI) LDMOS was introduced [21], optimizing depth and corner angle for superior performance. However, in low‑voltage regimes the channel resistance becomes a significant contributor to Ron,sp, necessitating new design strategies that target both drift and channel regions.

Method

We developed an LDMOS featuring an enhanced dual‑gate and a partial P‑buried layer. Device physics were modeled using the IMPACT.I, BGN, CONMOB, FLDMOB, SRH, and SRFMOB simulation packages. An analytical on‑resistance framework was derived to dissect the contributions of the drift and channel resistances, guiding the systematic optimization of the N‑buried and partial P‑buried layers for minimal Ron,sp and maximal BV.

Results and Discussion

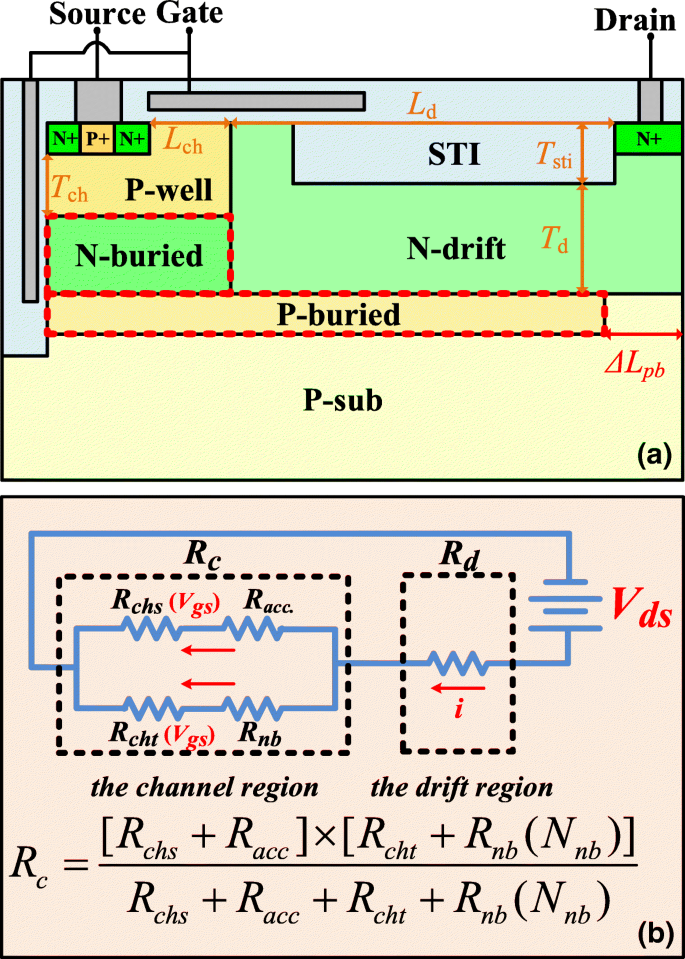

Figure 1a illustrates the cross‑section of the proposed device, highlighting the dual‑gate structure (trench gate + N‑buried layer) and the partial P‑buried layer under the drift region. The N‑buried layer supplies a low‑resistance path beneath the P‑well, substantially reducing Rc, while the partial P‑buried layer extends the depletion region and suppresses peak electric fields, thereby enhancing BV. The key dimensional parameters are summarized in Table 1.

a Schematic cross‑section view of the ultra‑low specific on‑resistance LDMOS with enhanced dual‑gate and partial P‑buried layer. b Equivalent on‑resistance model for the proposed device.

Figure 1b depicts the equivalent on‑resistance model, where the total on‑resistance is the series sum of the drift resistance (Rd) and the channel resistance (Rc). In the channel, the surface‑gate and trench‑gate paths are parallel, yielding Rc = (Rchs + Racc)‖(Rcht + Rnb). Reducing Rnb via a highly doped N‑buried layer directly lowers Rc without affecting other performance metrics. The drift resistance was minimized by incorporating the partial P‑buried layer, leveraging the RESURF effect as demonstrated in our earlier study.

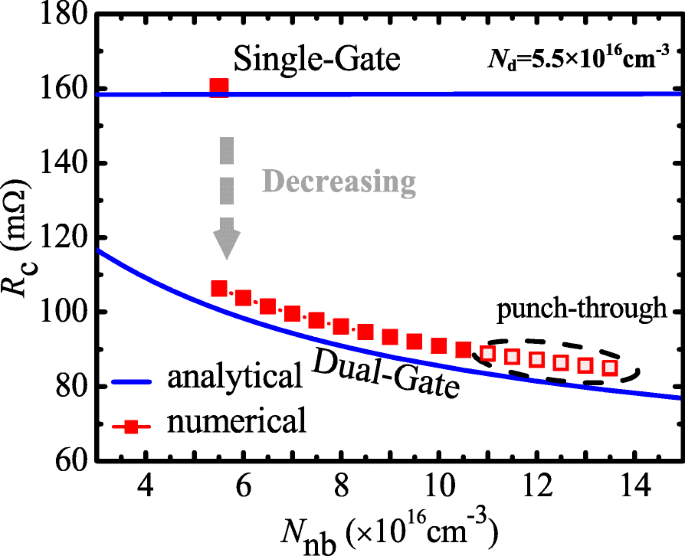

Figure 2 shows the dependence of Rc on the N‑buried layer doping concentration (Nnb) for single‑gate and dual‑gate configurations. The dual‑gate structure yields a 34 % reduction in Rc at Nnb = 5.5 × 1016 cm⁻³. Further doping increases Rc continuously until punch‑through occurs at ≈1.05 × 1017 cm⁻³. The analytical model aligns closely with simulation, validating its use for design optimization.

Numerical and analytical Rc as a function of Nnb with single‑gate and dual‑gate (Z = 1 cm). Nd denotes the N‑drift doping concentration.

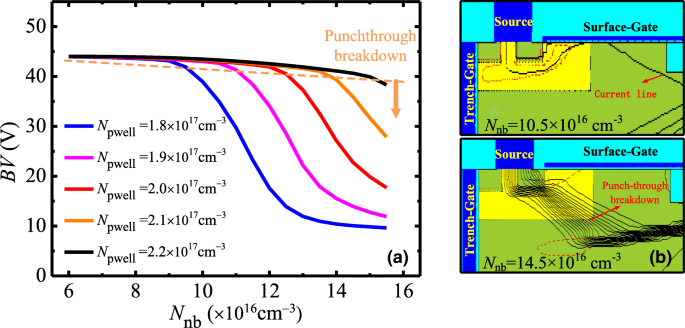

Figure 3a explores the impact of Nnb on BV for various P‑well doping levels (Npwell). BV remains stable at low Nnb but decreases when punch‑through initiates. A P‑well doping of 2 × 1017 cm⁻³ is selected to balance threshold voltage and breakdown performance. Figure 3b visualizes the current density profile at breakdown, confirming the absence of punch‑through for the chosen parameters.

a Numerical BV versus Nnb for different Npwell. b Current density profile at breakdown for Nnb = 10.5 × 1016 cm⁻³ and 14.5 × 1016 cm⁻³ with Npwell = 2 × 1017 cm⁻³.

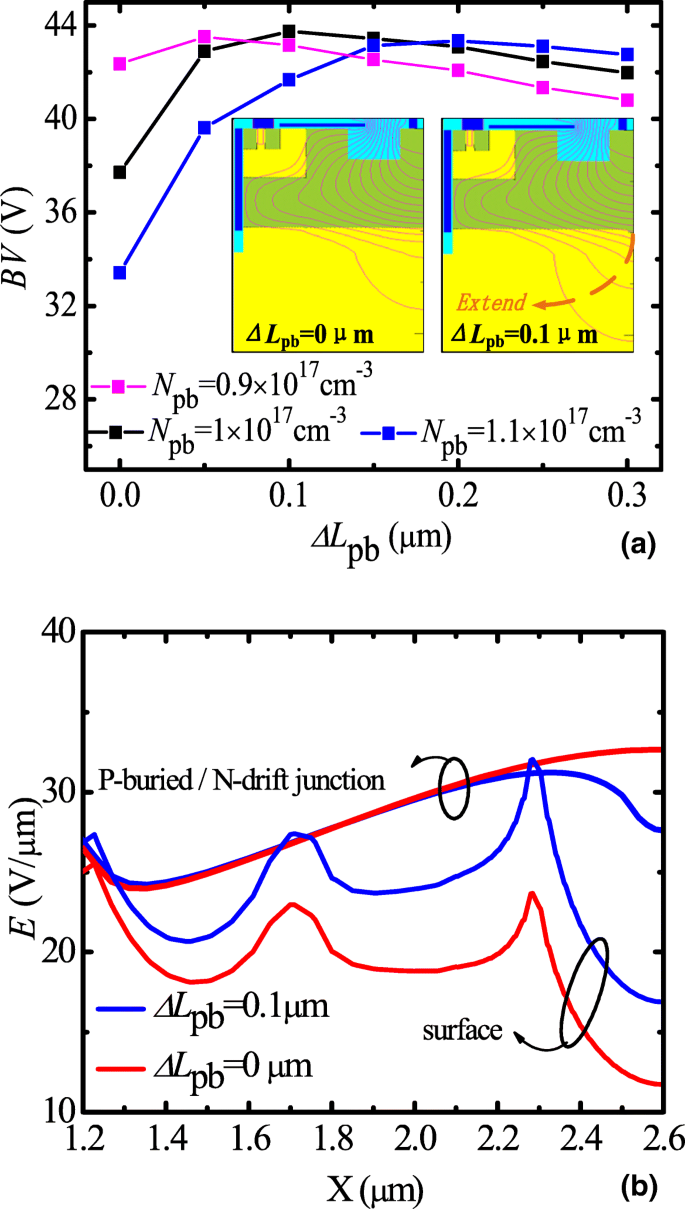

To further reduce drift resistance while preserving high BV, a partial P‑buried layer (ΔLpb) is introduced beneath the N‑drift region. Figure 4a demonstrates that a ΔLpb of 0.1 µm and a doping of 1 × 1017 cm⁻³ yield the peak BV of 43 V. The equipotential contour in the partial P‑buried configuration extends deeper into the substrate, reducing peak electric fields at the N‑drift/P‑buried interface (Figure 4b). This design shift alleviates vertical field stress and promotes charge balance.

a BV versus ΔLpb for different Npb; inset shows the equipotential contour for Npb = 1 × 1017 cm⁻³. b Electric field distribution at the surface and the P-buried/N-drift junction interface.

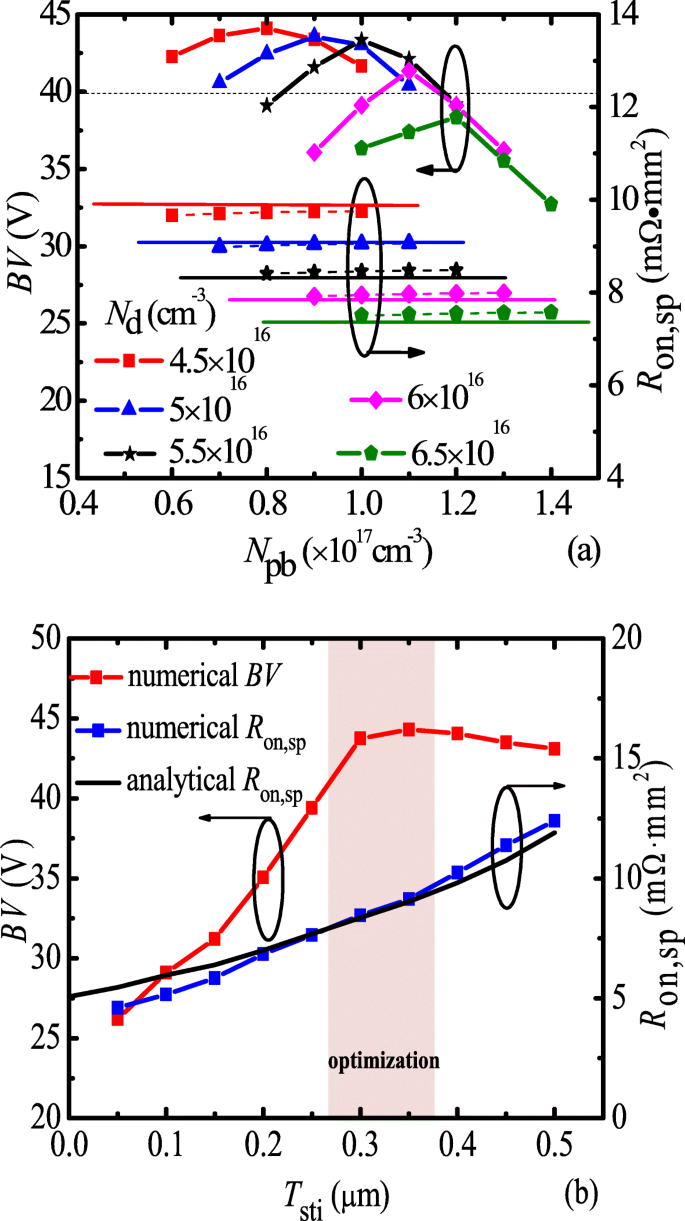

Charge‑balance analysis (Figure 5a) indicates that optimal Npb of 1 × 1017 cm⁻³ paired with an N‑drift doping of 5.5 × 1016 cm⁻³ achieves the target BV > 40 V while keeping Ron,sp low. Figure 5b highlights the influence of the STI thickness (Tsti); a thickness of 0.3 µm yields a BV of 43 V and mitigates field peaks under the poly field‑plate edge.

a Numerical (dotted) and analytical (solid) BV and Ron,sp versus Npb for various Nd. b Numerical (dotted) and analytical (solid) BV and Ron,sp versus Tsti.

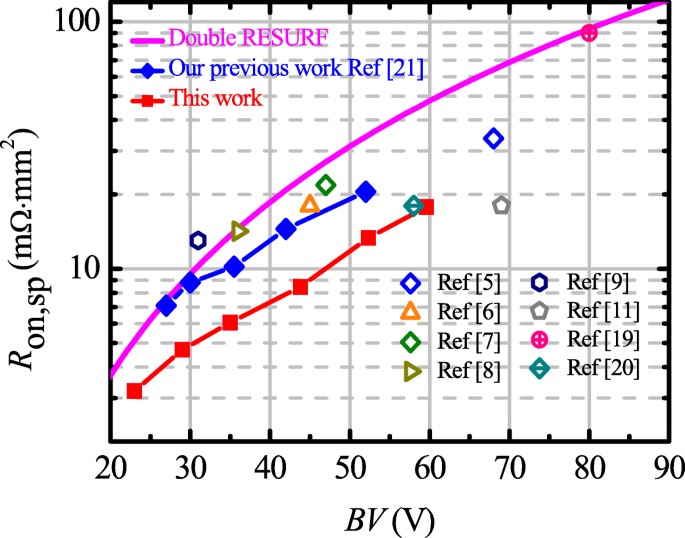

Figure 6 benchmarks the proposed LDMOS against existing Bipolar‑CMOS‑DMOS (BCD) technologies. The design leverages the same mask set for the N‑buried and P‑well layers, ensuring compatibility with our proven BCD process flow. Compared to our earlier LDMOS (8.5 mΩ·mm² vs 13.3 mΩ·mm²), the new structure achieves a 37 % reduction in specific on‑resistance while delivering 43 V BV.

The benchmark of existing BCD technologies and the proposed LDMOS.

Conclusion

We have introduced an LDMOS transistor that simultaneously reduces the channel resistance via a highly doped N‑buried layer and elevates breakdown voltage through a partial P‑buried layer. The resulting device attains 8.5 mΩ·mm² specific on‑resistance at 43 V BV, representing a 37 % improvement over prior work. The fabrication flow is fully compatible with existing BCD processes, enabling immediate integration into advanced analog power ICs. As semiconductor dimensions continue to shrink, further reductions in Ron,sp can be achieved by shortening the channel length while maintaining the demonstrated architectural benefits.

Abbreviations

- BCD

Bipolar‑CMOS‑DMOS

- BV

Breakdown voltage

- LDMOS

Lateral double‑diffused metal‑oxide‑semiconductor transistor

- RESURF

Reduce surface‑field

- Ron,sp

Specific on‑resistance

- USTI

Ultra‑shallow trench isolation

Nanomaterials

- High‑Efficiency, Wide‑Angle Nanohole Absorber Exploiting Void Plasmon Resonance with Ultra‑Strong Field Enhancement

- SnSe₂ Field‑Effect Transistor Achieves 10⁴ On/Off Ratio and Polarity‑Switchable Photoconductivity

- Ultra‑Thin TiO₂ Nanomembranes via Atomic Layer Deposition Deliver Record‑High Capacitance for Pseudocapacitor Electrodes

- Partially BiVO4-Modified ZnO Porous Nanosheets: Solar‑Driven Photocatalysis with Superior Charge Separation

- Boosting PERC Solar Cell Performance: ALD‑Deposited Al₂O₃ with Optimized Two‑Step Annealing for Superior Si Passivation

- AlGaN/GaN HEMTs with 803 V Breakdown: Fluorine‑Doped SiNx Passivation Yields Low Dynamic ON‑Resistance

- Enhanced Reliability of a-IGZO TFTs via Clean Etch‑Stopper Layer and Reduced Feature Size

- pH‑Triggered Ferritin Nanocarrier Enables Controlled Resveratrol Delivery for Targeted Tumor Chemotherapy

- Efficient Fabrication of Mesostructured NR/SiO₂ Nanocomposites with Superior Thermal Stability and Hydrophobicity

- Stable Carbon‑Dot Frameworks with Superior Antibacterial Efficacy