Enhanced Reliability of a-IGZO TFTs via Clean Etch‑Stopper Layer and Reduced Feature Size

Abstract

We investigated how diffuse Cu+ impacts the microstructure and performance of amorphous indium‑gallium‑zinc‑oxide (a‑IGZO) thin‑film transistors (TFTs) during a clean etch‑stopper (CL‑ES) process and a back‑channel etch (BCE) process. Time‑of‑flight secondary ion mass spectrometry (TOF‑SIMS) confirmed that the CL‑ES layer, composed of a clean SiOx etch‑stopper, protects the a‑IGZO channel from the source‑drain (S/D) etchant and blocks Cu+ diffusion. Consequently, the CL‑ES‑structured TFTs exhibit superior output stability (final Ids/initial Ids = 82.2 %) versus BCE‑structured TFTs (53.5 %). The CL‑ES devices also achieve a lower initial sub‑threshold swing (SS) of 0.09 V dec−1 versus 0.46 V dec−1 and a reduced SS degradation (0.16 V dec−1 versus 0.24 V dec−1) after high‑current stress (HCS). Notably, the threshold‑voltage shift is only 3.5 V for CL‑ES TFTs compared to 7.2 V for BCE TFTs, indicating markedly higher reliability. These results suggest that the CL‑ES process is a promising route for scalable, high‑performance a‑IGZO displays.

Background

Modern display products demand large, high‑resolution panels with slim bezels and elegant aesthetics. Gate‑drive IC on array (GOA) technology, where gate signals are serially sent to the panel, offers cost savings (eliminating G‑ICs and bonding steps) and enables narrow‑bezel designs. However, GOA TFTs must deliver higher output currents and longer on‑times, imposing stricter reliability requirements than individual pixel TFTs. Amorphous indium‑gallium‑zinc‑oxide (a‑IGZO) is a leading channel material because of its high saturation electron mobility (5–10 cm2 V−1 s−1) and ultra‑low off‑current (< 1 pA). The conventional BCE process, which exposes the a‑IGZO back channel to aggressive etchants (HNO3, H3PO4, CH3COOH), is widely used for individual pixel TFTs but suffers from etchant‑induced damage and Cu contamination of the channel, limiting its suitability for high‑current GOA TFTs. A clean etch‑stopping (CL‑ES) strategy, employing a robust SiOx layer, can shield the channel from etchants and Cu diffusion, improving uniformity and stability across large‑area displays. The present study evaluates the CL‑ES process on a‑IGZO GOA TFTs with reduced feature size, comparing microstructure and electrical performance against BCE‑structured counterparts.

Experimental Methods

Fabrication of a-IGZO GOA TFTs

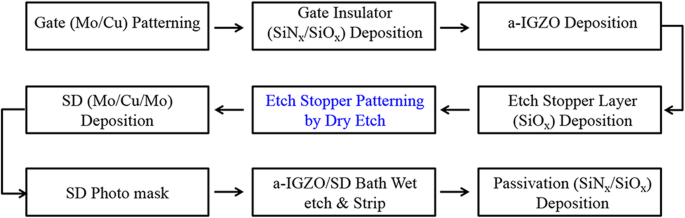

The CL‑ES TFTs were fabricated through a modified five‑step CL‑ES sequence (Fig. 1). First, a Mo/Cu gate electrode was patterned, followed by a SiNx/SiOx (3000 Å/1000 Å) dielectric stack deposited by PECVD at 340 °C. Next, a 300 Å a‑IGZO film was sputtered at room temperature with 15 % O2. A 1000 Å SiOx etch‑stopper (ESL) was then deposited at 240 °C and patterned using CF4 plasma, protecting the underlying a‑IGZO in the active regions. Subsequent S/D electrodes (Mo/Cu/Mo) were sputtered and etched with a 0.2 wt % fluoride‑additive H2O2 solution, using the ES pattern as the mask. Finally, a 3000 Å passivation layer was deposited. BCE devices were produced with the conventional BCE process and identical masks for direct comparison.

Fabrication process of the a‑IGZO GOA TFT

Characterization

SEM (Camscan Mx2600FE) and XPS (PHI Quantera II) examined morphology and composition, while TOF‑SIMS (IONTOF, TOF‑SIMS 5) probed Cu diffusion. Electrical testing used a Keysight 4082A analyzer in a dark environment at 60 °C. High‑current stress (HCS) reliability was assessed over 1000 s at Vgs = 25 V and Vds = 25 V, recording Ids every second and transfer characteristics every 100 s.

Results and Discussion

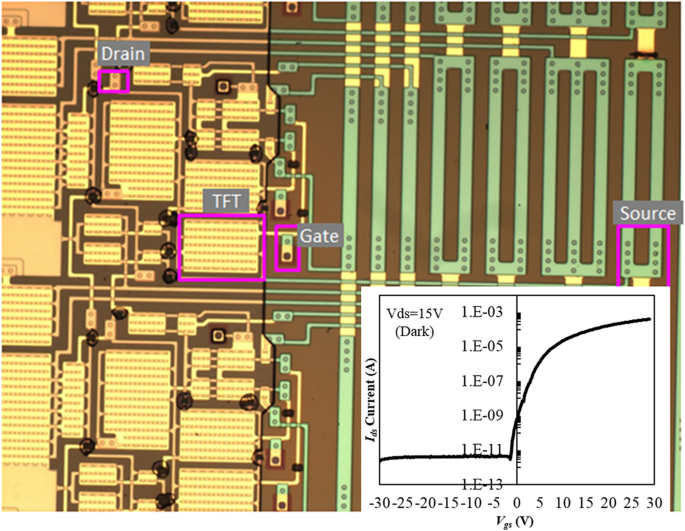

Figure 2 shows a GOA TFT fabricated via CL‑ES, with the channel width and length set to 120 µm and 10 µm, respectively. All devices were laser‑isolated to ensure independent measurement, yielding an Ioff noise of 3 pA and confirming negligible cross‑talk.

Photographs of the GOA TFTs electrically separated from the GOA circuits (insert: Ioff noise between the TFT of interest and the other peripheral TFTs)

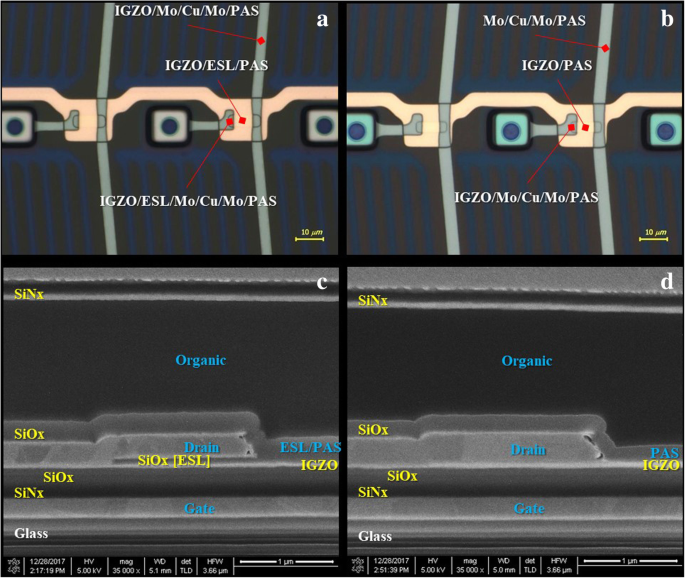

SEM analysis (Fig. 3) reveals that CL‑ES devices achieve channel dimensions of 4 µm × 6 µm—comparable to BCE devices—while retaining the ESL layer. The CL‑ES process eliminates the need for additional lithography steps beyond those used in BCE, reducing mask count and simplifying production.

SEM images of the a‑IGZO TFTs: a CL‑ES‑structured TFT top view, b BCE‑structured TFT top view, c CL‑ES‑structured TFT cross‑sectional view, and d BCE‑structured TFT cross‑sectional view

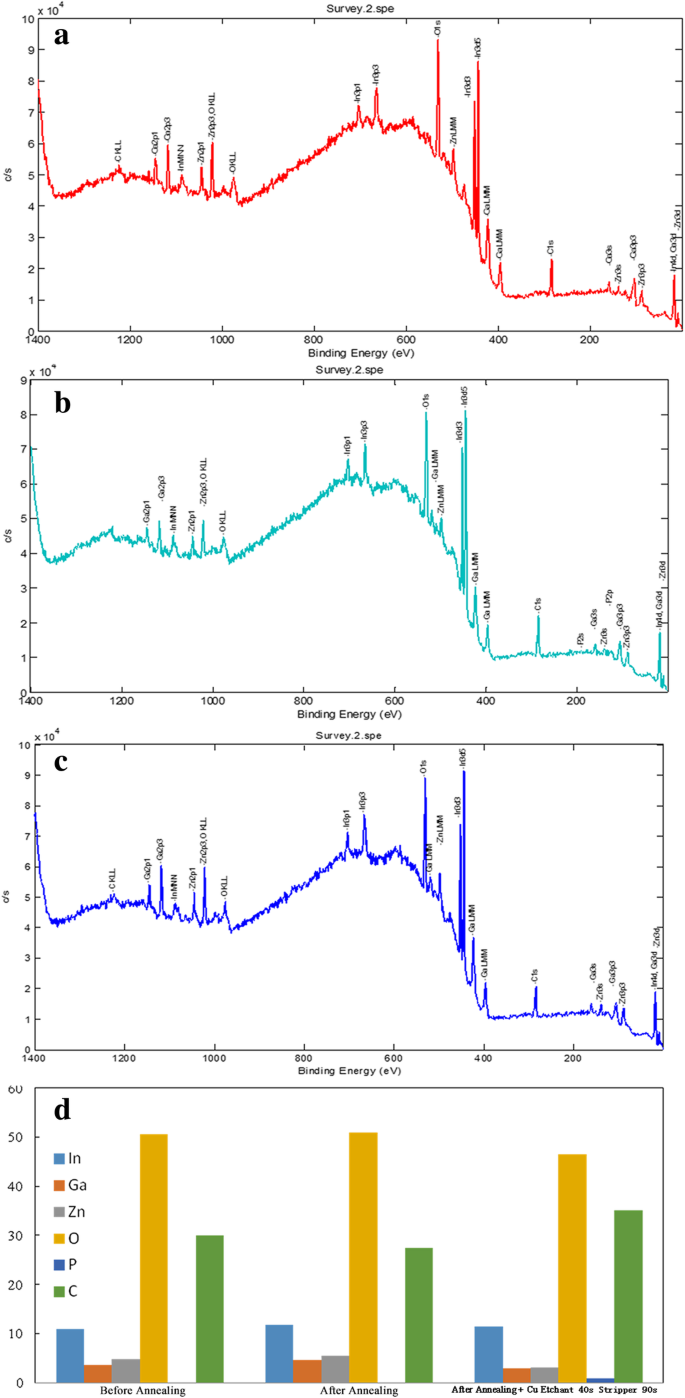

XPS spectra (Fig. 4) demonstrate that the BCE process does not significantly alter the a‑IGZO composition after annealing but causes substantial loss of Zn and Ga upon exposure to the H2O2 Cu etchant. Zn drops from 5.42 % to 3.16 % and Ga follows a similar trend, highlighting etchant‑induced defects and increased oxygen vacancies.

XPS analysis of the surface composition of the a‑IGZO thin films a before annealing, b after annealing, and c after exposure to the H2O2 Cu etchant during the BCE process. d Corresponding atomic percentages for the above process

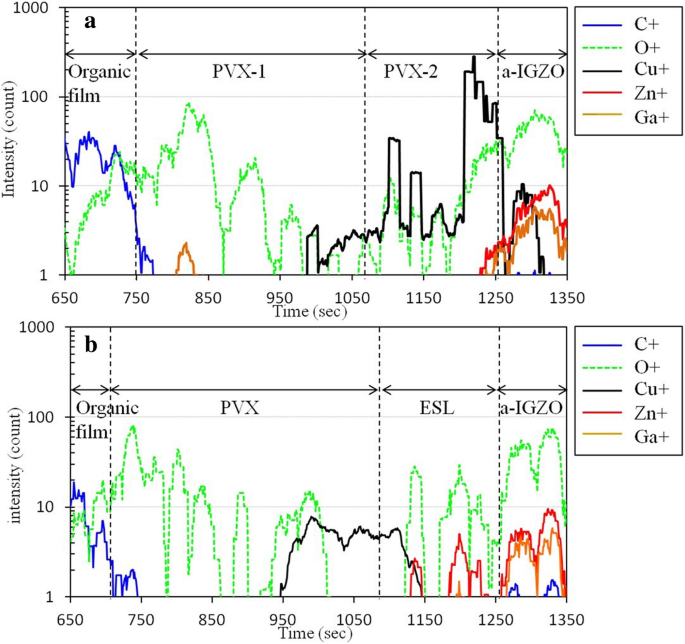

TOF‑SIMS mapping (Fig. 5) confirms that Cu+ penetrates the a‑IGZO channel in BCE devices, with a 20‑fold higher Cu peak compared to CL‑ES devices, where Cu is confined to the ESL. Zn diffusion into the ESL also indicates that high‑energy plasma during ESL deposition can introduce defects. The ESL in CL‑ES devices thus serves as both an etchant shield and a Cu diffusion barrier, preserving channel purity.

TOF‑SIMS analysis of the channel regions of a-IGZO TFTs fabricated via a the BCE and b the CL‑ES processes

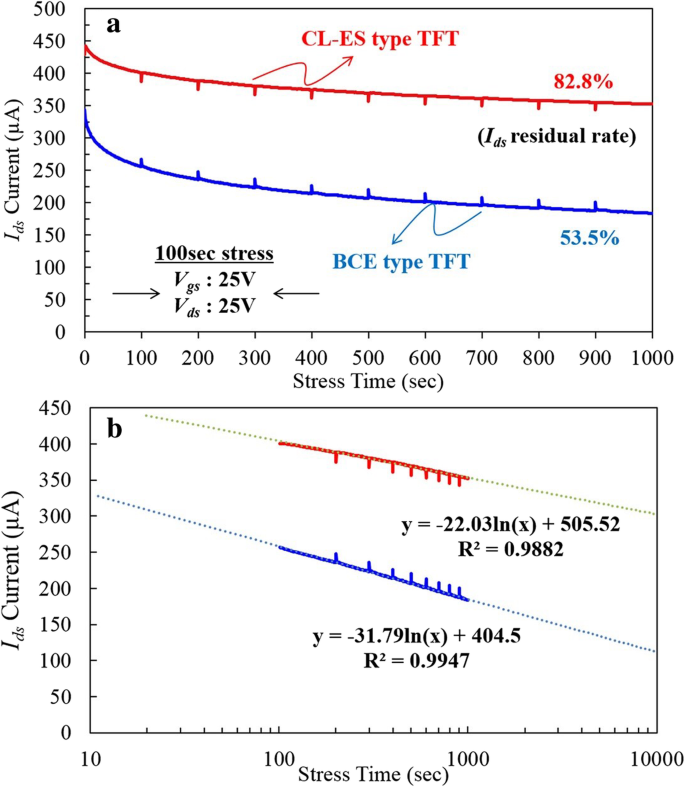

High‑current stress testing (Fig. 6) shows that CL‑ES TFTs retain 82.2 % of their initial Ids after 1000 s, whereas BCE TFTs drop to 53.5 %. Extrapolation predicts that CL‑ES devices maintain 70.5 % after 10,000 s versus 33.7 % for BCE, indicating a 271 % improvement in integration reliability.

a Experimental data for 1000 s and b extrapolation for long‑term HCS evaluation of the CL‑ES and BCE‑structured GOA TFTs

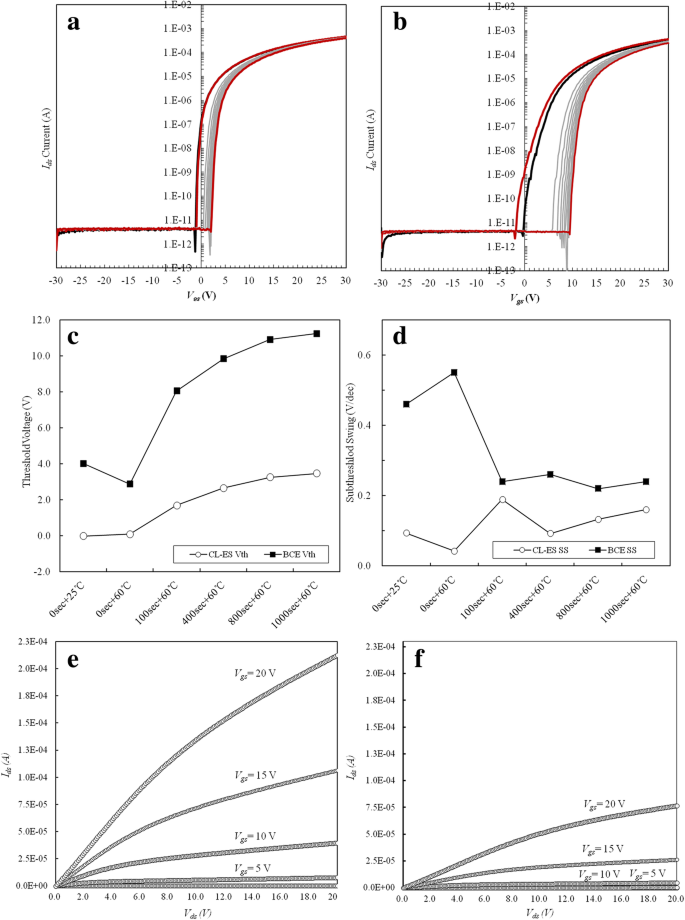

Transfer‑characteristic evolution (Fig. 7, Table 1) reveals that CL‑ES TFTs shift from 0.0 V to 3.5 V in Vth after 1000 s at 60 °C, with a modest SS increase from 0.09 to 0.16 V dec−1. In contrast, BCE TFTs exhibit a dramatic Vth rise from 4.0 to 11.2 V and a SS drop from 0.46 to 0.24 V dec−1, reflecting severe Cu‑induced trap formation and surface damage. The CL‑ES process therefore yields superior electrical stability and uniformity.

I‑V transfer characteristics measured during the HCS evaluation of a the CL‑ES and b the BCE‑structured GOA TFTs. Behavior of c the threshold voltage and d the sub‑threshold swing at intervals of 1000 s and Vds = 15 V. The initial measurements of the Id-Vd output characteristics for e the CL‑ES and f the BCE‑structured GOA TFTs with Vgs = 0, 5, 10, 15, and 20 V

The CL‑ES TFTs display consistent output curves across devices, while BCE devices show notable variations, underscoring the importance of ESL‑based protection for large‑area uniformity.

Conclusion

We demonstrated that a clean etch‑stopping (CL‑ES) layer, combined with reduced feature size, dramatically improves the performance and reliability of a‑IGZO GOA TFTs. The CL‑ES process eliminates etchant damage and Cu diffusion, leading to higher residual Ids (≈ 187 % of initial), lower initial SS (0.09 V dec−1), and smaller Vth shift (3.5 V). These benefits enable higher integration densities, cost‑effective manufacturing, and robust operation for next‑generation narrow‑bezel, high‑resolution displays.

Abbreviations

- TFT:

Thin‑film transistor

- GOA:

Gate‑drive IC on array

- a‑IGZO:

Amorphous indium‑gallium‑zinc‑oxide

- LCD:

Liquid crystal display

- PEVCD:

Plasma‑enhanced chemical vapor deposition

- ESL:

Etch‑stopper layer

- BCE:

Back‑channel etch

- HCS:

High current stress

- SiOx:

Silicon oxide

- SiNx:

Silicon nitride

- SS:

Sub‑threshold swing

Nanomaterials

- Enhancing THz Micro‑Bolometer Performance with Spiral‑Type Antenna‑Coupled Micro‑Bridge Designs

- GeSiSn Thin Films with Nanoislands: Strain‑Driven Morphology, Superstructure Control, and Mid‑IR Photoluminescence

- Optimizing a-IGZO TFTs for Large‑Area Displays with a Clean Etch‑Stopper Nano‑Layer Process

- Lowering Metal–Ge Contact Resistance with ZnO Interlayers and Argon Plasma: Achieving Ohmic Al Contacts on n‑Ge

- Ultra‑Low Specific On‑Resistance LDMOS with Enhanced Dual‑Gate and Partial P‑Buried Layer

- Hierarchically Structured Kaolinite Nanospheres: Superior Methylene Blue Adsorption Performance

- Boosting PERC Solar Cell Performance: ALD‑Deposited Al₂O₃ with Optimized Two‑Step Annealing for Superior Si Passivation

- Stable Carbon‑Dot Frameworks with Superior Antibacterial Efficacy

- SPA Vympel Elevates Gas System Reliability Using Swagelok Components

- Boosting Consistency & Reliability: The Power of Robotic Spot Welders