High‑Holding Voltage Silicon‑Controlled Rectifier with Embedded Carrier‑Recombination for Robust, Latch‑up‑Immune ESD Protection

Abstract

A novel CMOS‑process‑compatible high‑holding voltage silicon‑controlled rectifier (HHV‑SCR) is presented, designed to deliver superior electrostatic discharge (ESD) protection. By integrating a hole (or electron) recombination region (H‑RR or E‑RR), the device not only recombines minority carriers in the parasitic PNP (or NPN) transistor base via a lightly doped N+ (or P+) layer, but also introduces an additional recombination layer that suppresses surface avalanche carriers. This dual‑layer approach raises the holding voltage (Vh) to 8.1 V—more than four times the 1.8 V typical of low‑voltage triggered SCRs—while maintaining a high failure current (It2 > 2.6 A) and a figure of merit (FOM) increase exceeding 400 %.

Introduction

Semiconductor integration has driven continuous feature‑size reduction, amplifying the impact of electrostatic discharge (ESD) on device reliability. Conventional ESD‑protective elements such as diodes and gate‑grounded N‑channel MOSFETs (ggNMOS) offer robustness but occupy large silicon real estate. Low‑voltage triggered silicon‑controlled rectifiers (LVTSCRs) emerged as a compact alternative, delivering high current capability per unit area and fast response due to their embedded low‑trigger voltage (Vt1) ggNMOS. However, the strong positive feedback inherent in LVTSCRs yields a very low holding voltage (Vh) of 1–2 V, which can trigger latch‑up and transient mis‑trigger events. Existing strategies to raise Vh—such as adding N+ ESD regions, P+ LDD layers, or emitter‑voltage clamp techniques—typically require extra mask steps and can degrade ESD performance through added power dissipation or non‑adjustable Vh.

In this work, we propose a novel high‑holding voltage SCR (HHV‑SCR) that simultaneously achieves a high Vh, a high failure current (It2), and adjustable Vh without extra masks or process steps. Transmission‑line‑pulse (TLP) testing confirms that Vh can be increased to over 8 V while preserving a robust It2 and a large figure of merit (FOM).

Method

Device performance was evaluated using Synopsys Medici TCAD simulations. We employed the IMPACT.I, BGN, CONMOB, FLDMOB, SRH, and SRFMOB models to capture impact ionization, band‑gap narrowing, carrier mobility, and Shockley‑Read‑Hall recombination. The H‑RR and E‑RR structures were optimized to maximize Vh and the power density (PM). Fabricated HHV‑SCRs and reference LVTSCRs were characterized with a commercial TLP system.

Structure and Mechanism

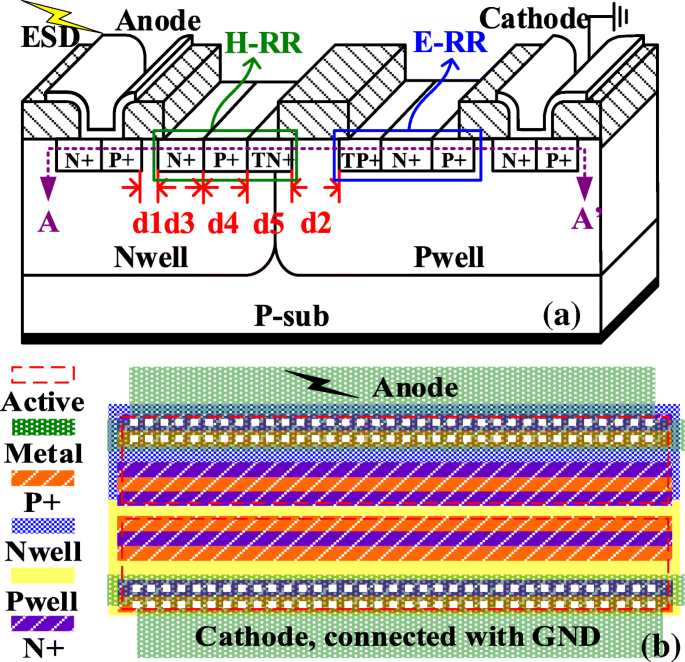

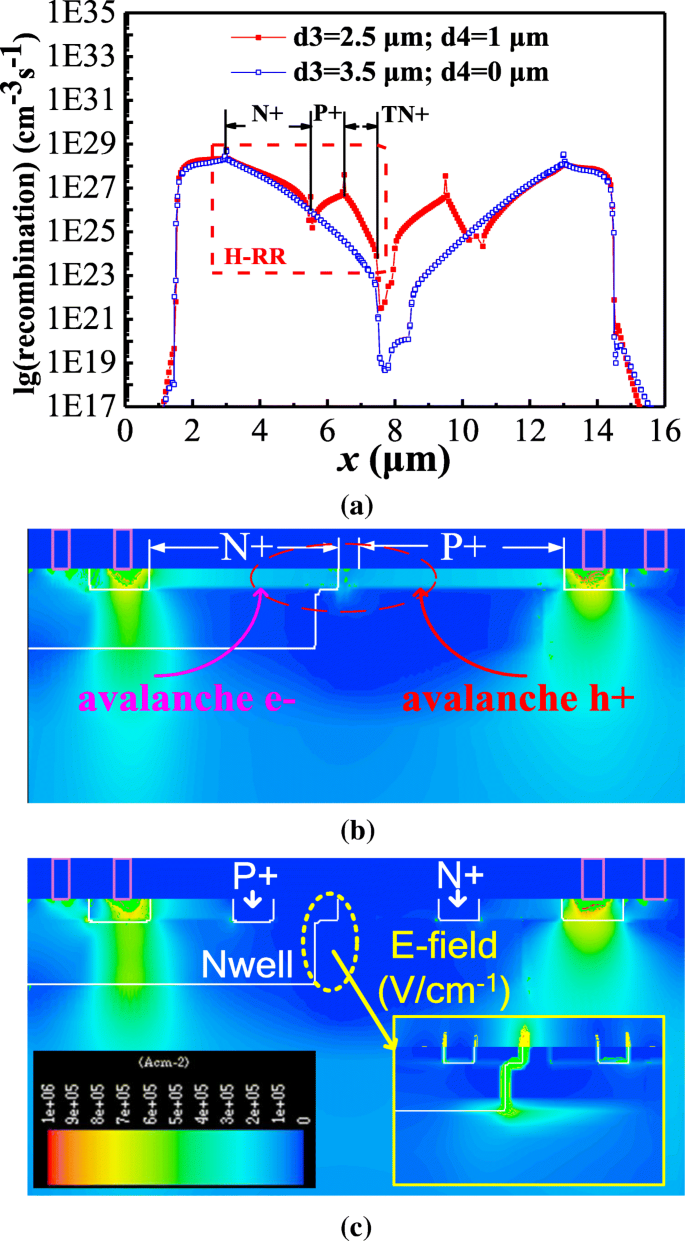

The schematic cross‑section (Fig. 1a) and layout diagram (Fig. 1b) illustrate the key innovation: floating N+ and P+ layers forming the H‑RR and E‑RR. In the H‑RR, a lightly doped N+ (TN+) sits adjacent to the anode P+ region, while an additional P+ (TP+) is placed next to the floating N+. The E‑RR mirrors this arrangement on the cathode side. During a high‑voltage ESD event, the low‑breakdown TN+/P‑well/TP+ junction triggers first, initiating avalanche current that activates the parasitic bipolar transistors. The floating N+ (or P+) in the H‑RR (or E‑RR) rapidly recombines minority carriers injected from the anode (or cathode) edge, reducing the current gain (β) of the parasitic transistor and eliminating surface bipolar effects. Simultaneously, the additional P+ (or N+) layer in the recombination region captures surface avalanche carriers, further suppressing the surface current path. This dual recombination mechanism elevates the holding voltage while preserving high current capability.

a The schematic cross‑section of the proposed HHV‑SCR. b The layout diagram of the proposed HHV‑SCR.

Results and Discussion

Simulated Results

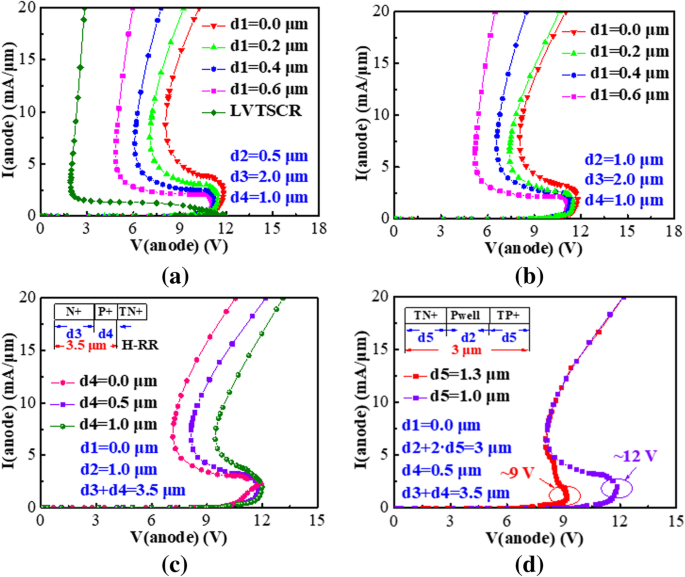

TCAD simulations of the LVTSCR and HHV‑SCR (Fig. 2) reveal that the HHV‑SCR’s Vh increases from 4.6 V to 8.1 V as the H‑RR spacing (d1) is reduced from 0.6 µm to 0 µm for a fixed device length (d2 = 0.5 µm). Shortening d1 enhances the recombination efficiency of the floating N+ in the H‑RR, yielding a lower parasitic β and higher Vh. Extending d2 to 1 µm further improves Vh by increasing the active device length. Adding a heavily doped P+ layer within the H‑RR (or N+ within the E‑RR) raises Vh from 7.1 V (without the extra layer) to approximately 9.5 V, as shown in Fig. 2c. Adjusting the widths of the floating layers (d5) allows the trigger voltage (Vt1) to be tuned from 12 V down to 9.0 V without affecting Vh (Fig. 2d), enabling compatibility with 5 V logic families.

Simulated snapback I‑V characteristics of conventional LVTSCR and proposed HHV‑SCR for varying d1 and d2 (a, b). (c) I‑V curves for different d3 and d4 with fixed d3 + d4 = 3.5 µm. (d) I‑V curves for various Vt1 settings.

a Recombination distribution curves. (b) Current distribution for d3 = 3.5 µm, d4 = 0 µm. (c) Current distribution for d3 = 2.5 µm, d4 = 1 µm.

Experimental Results

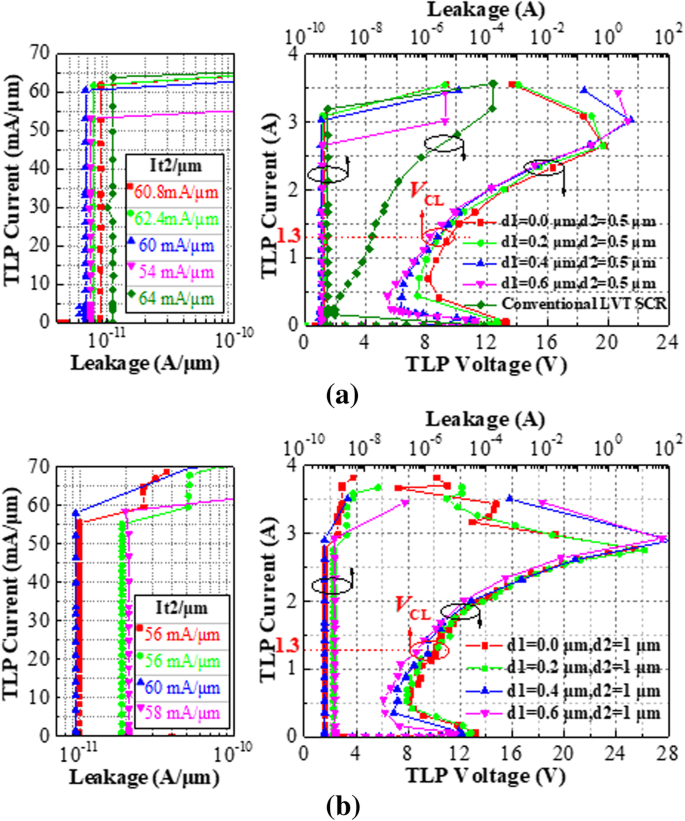

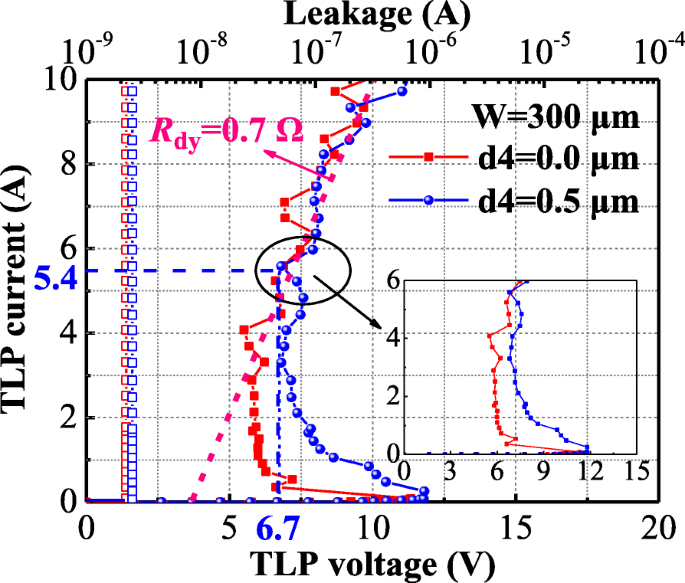

All devices were fabricated with a total width (W) of 50 µm and a single‑finger layout for direct parameter comparison (see Tables 1 and 2). TLP measurements (Fig. 4) demonstrate that the HHV‑SCR’s holding voltage rises from 5.5 V to 8.0 V as d1 is reduced from 0.6 µm to 0 µm, surpassing the 1.8 V of the LVTSCR. Increasing d2 to 1 µm further elevates Vh (Fig. 5). The clamping voltage (VCL) remains within acceptable limits (HBM = 2 kV, ITLP = 1.3 A) for the 50 µm devices, although stronger ESD stress can challenge the limited device width. Extending the finger width to 300 µm (for d1 = 0.6 µm, d4 = 0.5 µm or 0 µm) preserves VCL while delivering an exceptionally low dynamic resistance (Rdy ≈ 0.7 Ω), superior ESD robustness (It2 > 10 A), and a high Vh of 6.7 V. The influence of the additional P+ in the H‑RR is confirmed by the performance difference between devices with d4 = 0 µm and d4 = 0.5 µm.

Experimental failure current per unit width and TLP I‑V characteristics of conventional LVTSCR and proposed HHV‑SCRs with (a) d2 = 0.5 µm and (b) d2 = 1 µm at W = 50 µm.

Experimental TLP characteristic of HHV‑SCR with d4 = 0.0 µm and d4 = 1.0 µm at d1 = 0.6 µm, W = 300 µm.

Conclusion

The HHV‑SCR, compatible with standard CMOS processes, delivers a holding voltage that exceeds 8 V—over 450 % higher than the 1.8 V of conventional LVTSCRs—while sustaining a high failure current and a figure of merit that improves by more than 400 %. The device’s Vh can be tuned from 5.5 V to 8.1 V without sacrificing area or current capability, and its power density performance surpasses that of the baseline LVTSCR by over 200 %. These results establish the HHV‑SCR as a compact, latch‑up‑immune, and robust solution for modern ESD protection.

Availability of Data and Materials

All data generated or analyzed during this study are included in this published article.

Nanomaterials

- Maxim Unveils MAX22513: Dual‑IO-Link Transceiver with Integrated DC‑DC Regulator & Surge Protection for Smarter Digital Factories

- PEG‑Coated Gold Nanostars: A Safe, High‑Contrast Agent for CT Imaging with Rapid Renal Clearance

- Monodisperse Carbon Nanospheres with Hierarchical Porosity Deliver Superior Supercapacitor Performance

- Enhancing THz Micro‑Bolometer Performance with Spiral‑Type Antenna‑Coupled Micro‑Bridge Designs

- GeSiSn Thin Films with Nanoislands: Strain‑Driven Morphology, Superstructure Control, and Mid‑IR Photoluminescence

- Cost‑Effective PDMS Nanocone Cluster for Ultra‑Low Solar‑Cell Reflectance and Superhydrophobic Self‑Cleaning

- High‑Stability Voltage Regulator with Transient Enhancement & PSR Boost

- Latch‑Up‑Resistant LVTSCR with Integrated PMOSFET for Enhanced ESD Protection in 28‑nm CMOS

- Enhanced 4H‑SiC Power Rectifier Using Charge‑Field‑Modulated JTE: Improved Efficiency and Dose Tolerance

- ABB Enhances IRB 1300 Robot with IP67 Protection for Harsh & Cleanroom Environments