Enhanced Baliga’s Figure‑of‑Merits in a Novel GaN Nano‑Pillar Vertical FET with 2DEG Channel and Patterned Substrate

Abstract

A new enhancement‑mode vertical GaN field‑effect transistor (FET) incorporating a two‑dimensional electron gas (2DEG) channel and a substrate pattern (SP) is presented. By tailoring the SP width and height, the device achieves a lower on‑state resistance (RON) while maintaining a high breakdown voltage (BV). Experimental‑calibrated ATLAS simulations demonstrate that a 700‑nm‑long and 4.6‑µm‑wide SP yields a six‑fold increase in Baliga’s Figure‑of‑Merits (BFOM = BV²/RON) compared to an unpatterned counterpart, without sacrificing device area. The nanoscopic footprint of the pillar and SP permits high‑density integration, positioning this architecture as a strong candidate for future power electronics.

Background

Wide‑bandgap semiconductors such as ZnO, In2O3, SiC, and GaN have attracted significant attention due to their high breakdown voltages and superior thermal stability. In particular, the lateral AlGaN/GaN high‑electron‑mobility transistor (HEMT) is a leading candidate for replacing Si devices in power and RF applications. Numerous strategies—including p‑type caps, fluorine ion implantation, thin barriers, double‑channel designs, and field‑coupled gates—have been explored to realize enhancement‑mode HEMTs that simplify driver circuits. However, these approaches face challenges such as threshold voltage non‑uniformity, limited BFOM, and excessive chip area usage. The trade‑off between drift length and BV further hampers device scaling.

Vertical GaN FETs (VFETs) mitigate many of these issues by exploiting the full vertical channel and offering easier enhancement‑mode operation. Recent studies have focused on boosting BV while reducing RON through various structural innovations, yet the absence of a high‑mobility 2DEG often results in higher resistances, limiting BFOM optimization.

Our work introduces a vertical GaN FET that simultaneously incorporates a 2DEG channel and a patterned substrate. This combination balances low RON with high BV, while the nanoscale pillar and SP allow for dense device integration.

Method

The device is fabricated on a standard Al0.23GaN/GaN wafer, with a heavily doped n‑type substrate serving as the drain. Layer thicknesses are: SiN (105 nm), AlGaN (20 nm), and GaN (5 µm). A 2×1016 cm−3 n‑GaN buffer and a 2×1017 cm−3 p‑GaN cap form the buffer and composite channel, respectively. A thin AlGaN layer induces the 2DEG, and the SP—typically Al2O3—is grown on the substrate.

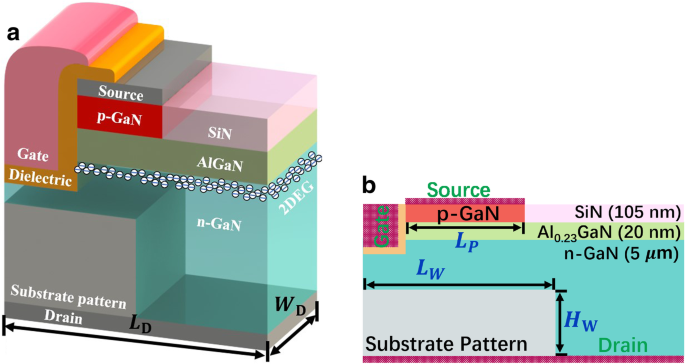

The schematic a shows the 3D pillar structure, and b presents the cross‑section with labeled dimensions of the proposed SP‑VFET.

The fabrication sequence is straightforward: (1) epitaxial growth of the conduction substrate and SP layer; (2) selective SP pattern etching; (3) deposition and polishing of the n‑GaN buffer; (4) AlGaN barrier and p‑GaN cap deposition; (5) electrode formation and passivation.

ATLAS simulations are calibrated against experimental data from an enhancement‑mode HEMT with a p‑GaN cap. Device parameters are listed in Table 1, and interface trap characteristics at the SP/GaN boundary are derived from capacitance measurements. Polarization charges are calculated via a quadratic fitting approach.

Physics Mechanism

In the on‑state, the SP‑VFET exhibits a highly conductive path due to the 2DEG, while the narrow vertical channel limits overall conductance. The 2DEG at the AlGaN/GaN interface sustains lateral current flow, partially compensating for the vertical resistance. Devices lacking the 2DEG channel experience markedly higher resistance.

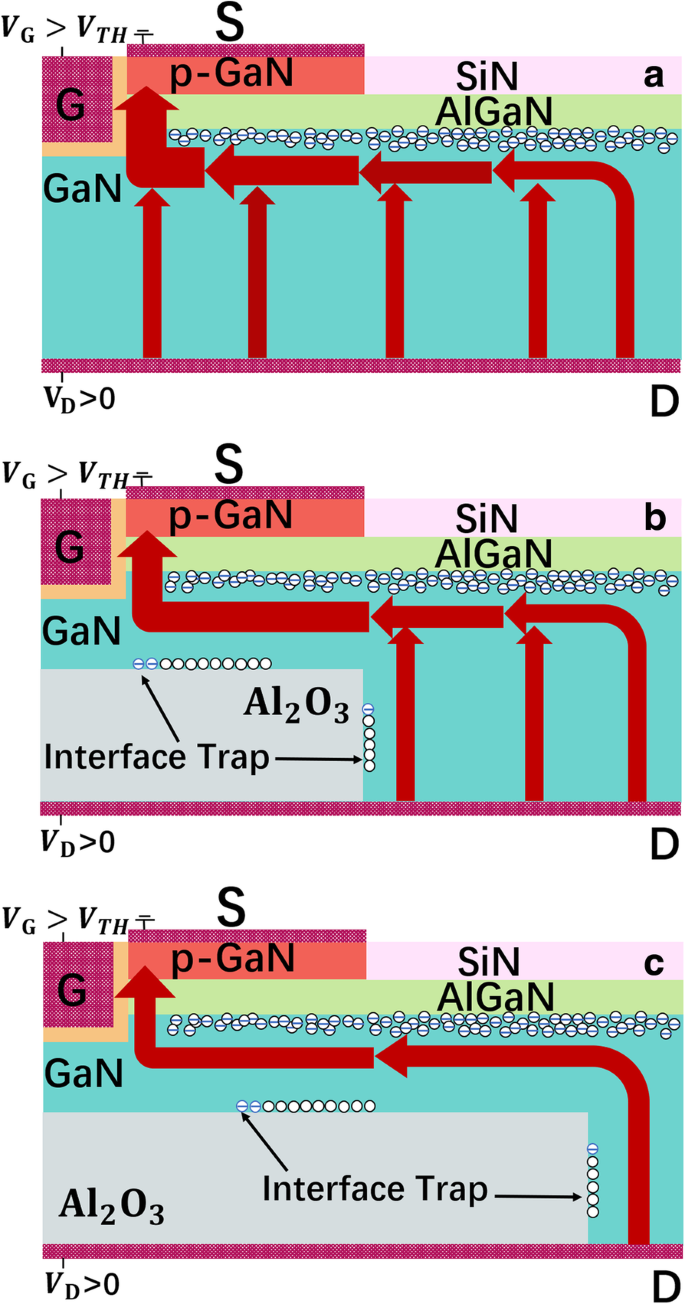

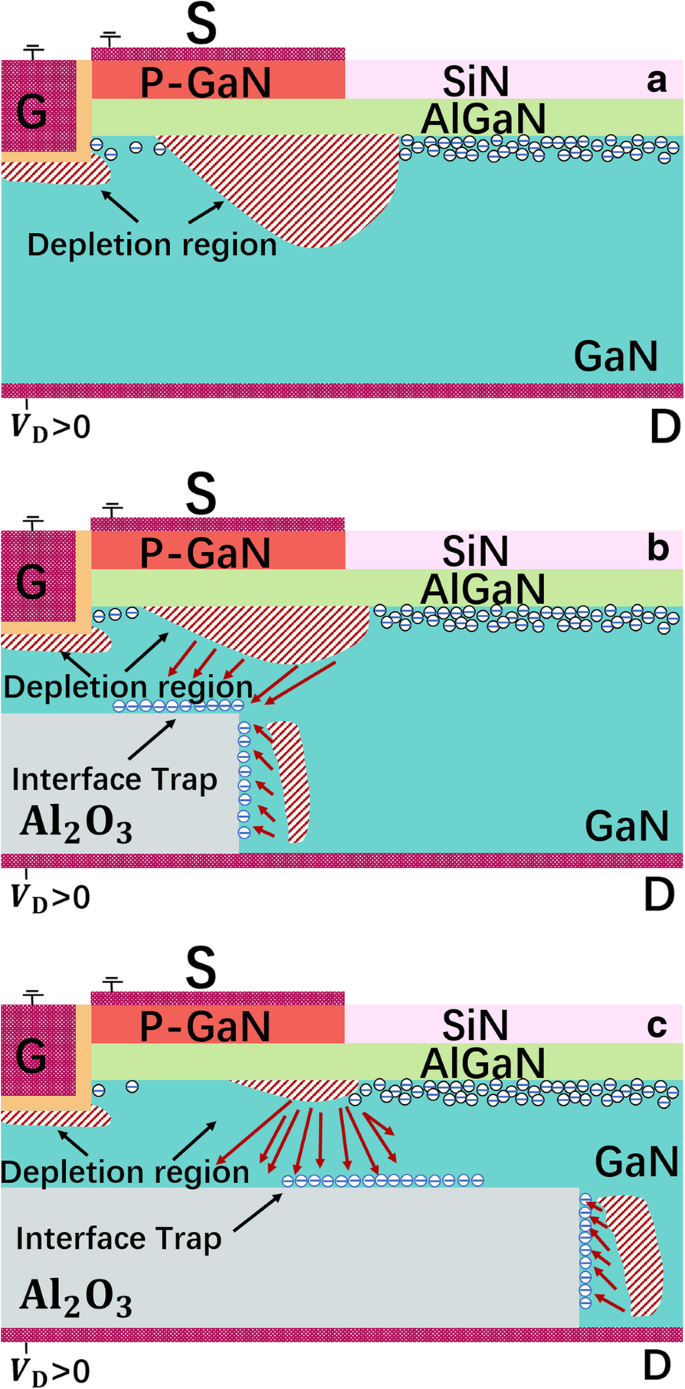

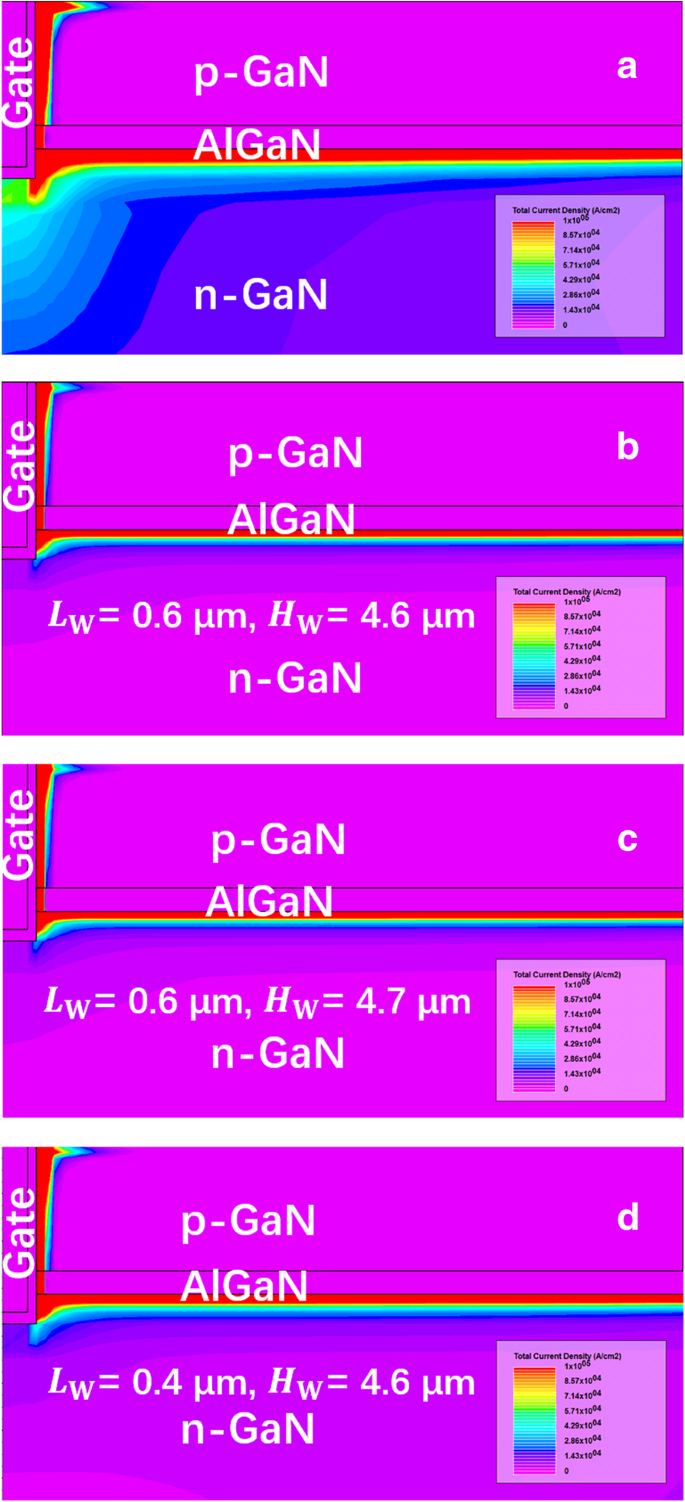

Forward current flow: a device without SP, b SP‑VFET with short SP, c SP‑VFET with long SP.

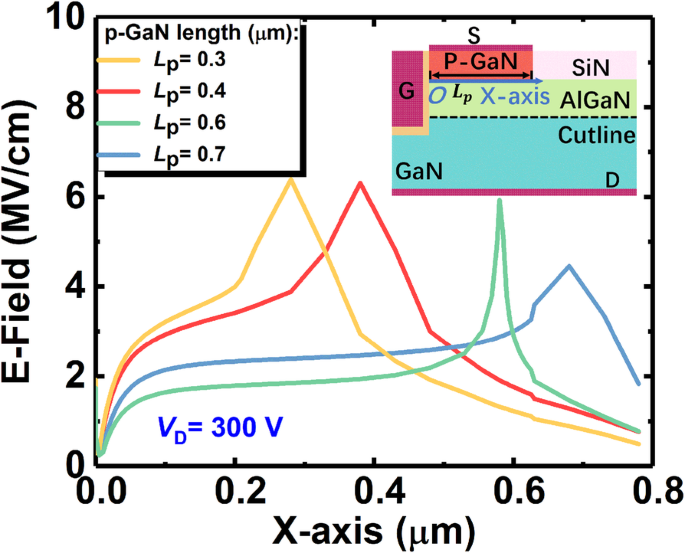

Simulations show that the p‑GaN cap length has minimal impact on the peak electric field until it exceeds 700 nm, at which point the cap covers the entire surface. The field peak remains at the p‑GaN corner regardless of length, but a longer cap flattens the field distribution, slightly increasing resistance due to 2DEG depletion.

Electric field along the AlGaN/GaN interface for different p‑GaN lengths.

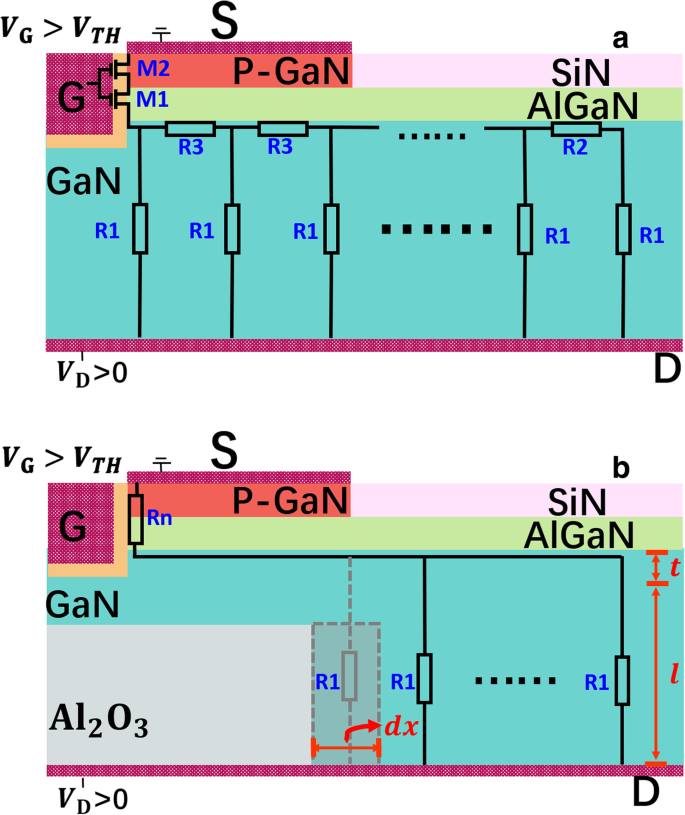

An analytical on‑state resistance model (Fig. 4) shows that the 2DEG channel dominates conductance; the vertical path resistance becomes significant only when the SP length grows. The on‑state resistance increases hyperbolically with SP length but remains largely unaffected by SP height below 4.7 µm, confirming the 2DEG’s resilience.

On‑state resistance networks: a without SP, b with SP.

In the off‑state, the SP’s negatively charged interface traps redistribute the electric field under the p‑GaN cap, reducing peak fields and expanding the depletion region. This redistribution improves breakdown voltage while only modestly increasing RON due to 2DEG compensation. Consequently, BFOM fluctuates with SP dimensions.

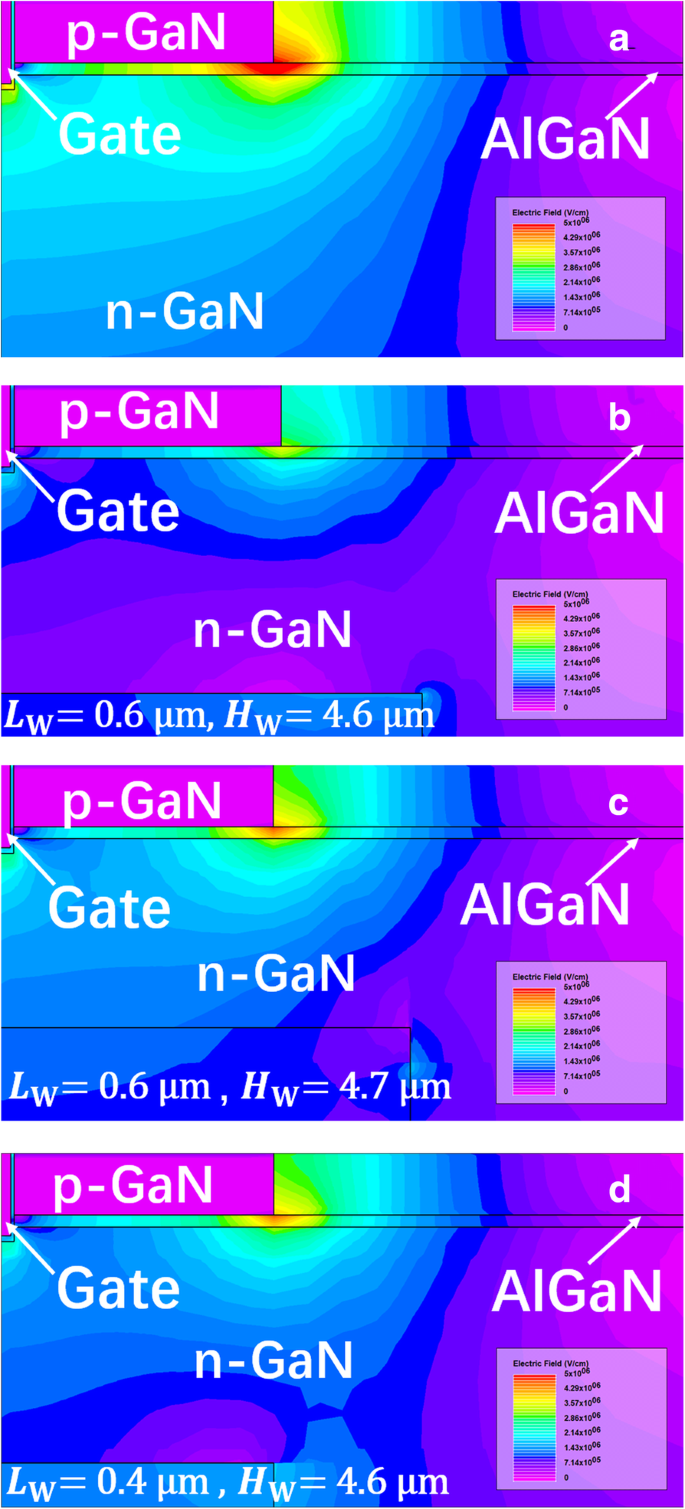

Electric field and depletion region distribution: a without SP, b SP‑VFET short SP, c SP‑VFET long SP.

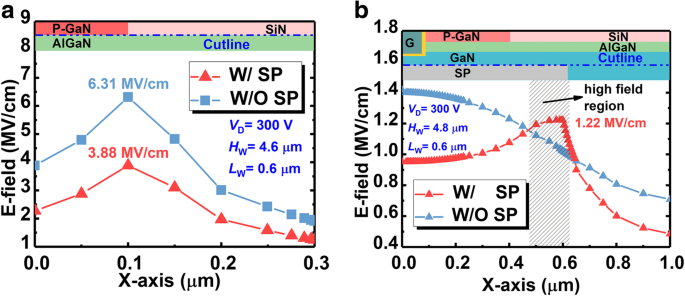

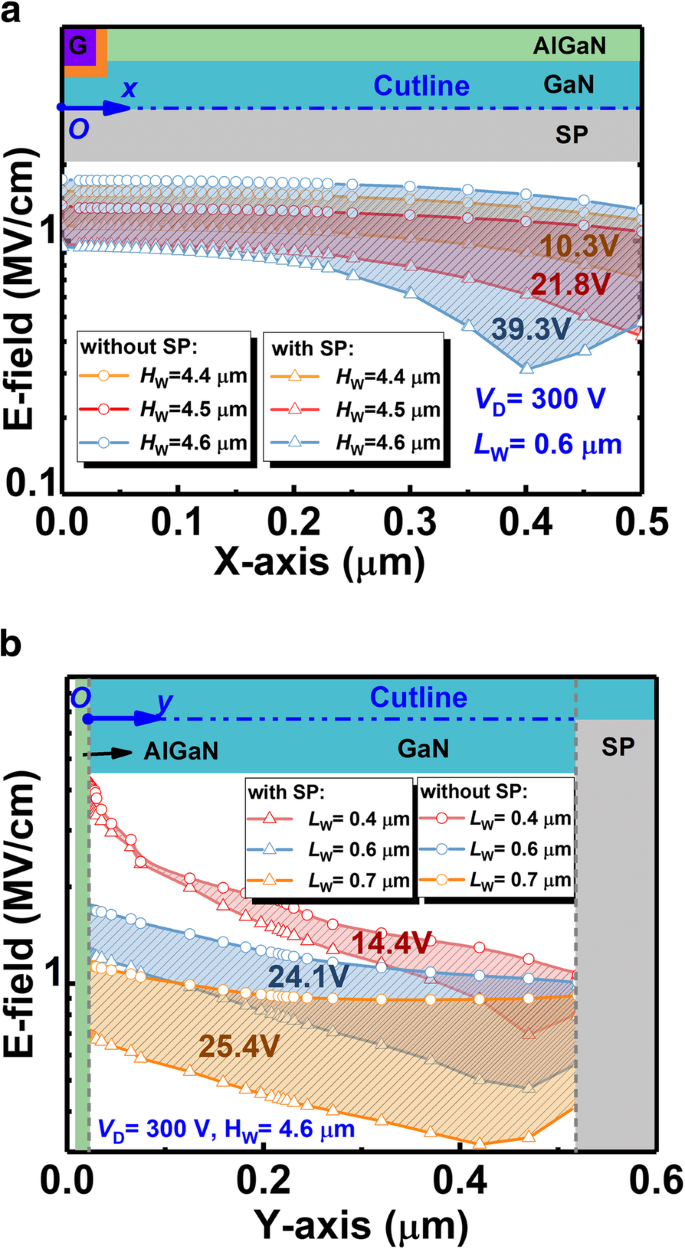

Field distribution along the p‑GaN/AlGaN (a) and GaN/SP (b) interfaces.

Result and Discussion

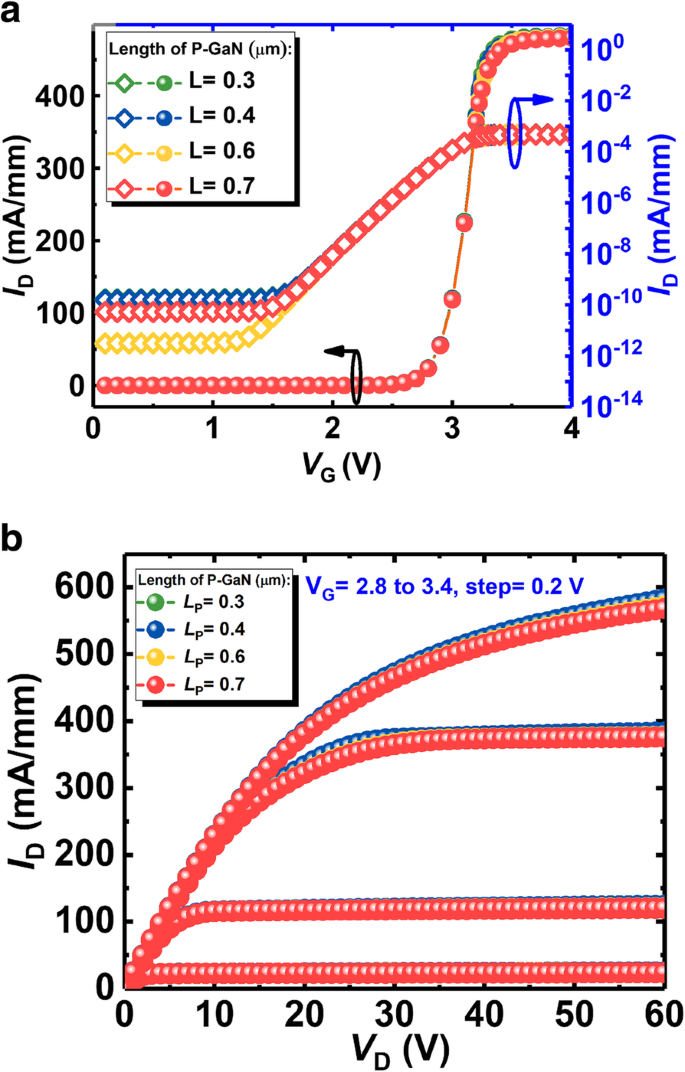

Transfer and output characteristics for devices without SP (Fig. 7) show negligible dependence on p‑GaN cap length, confirming the 2DEG’s role in maintaining consistent conductance. The minimum cap length is 400 nm to avoid excessive field crowding near the gate.

Transfer (a) and output (b) curves without SP for various p‑GaN lengths.

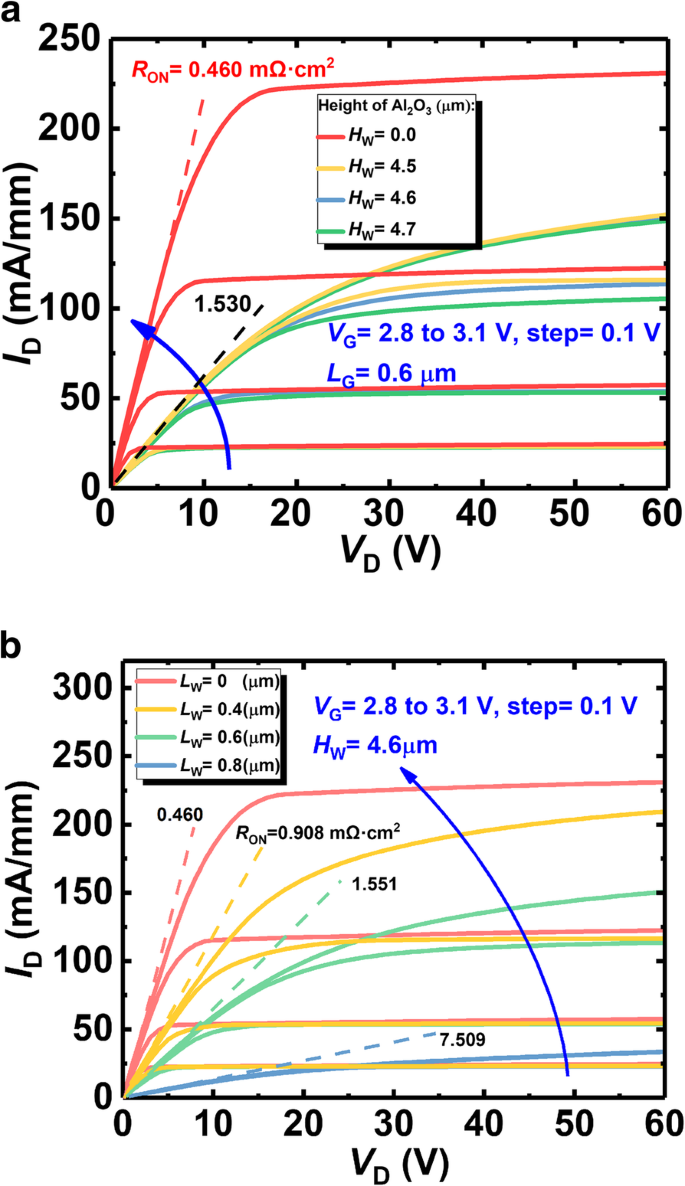

For SP‑VFETs (Fig. 8), the on‑state resistance remains constant for SP heights below 4.7 µm but increases with SP length, consistent with the narrowed vertical channel. The 2DEG channel remains largely unaffected by moderate SP heights; only when the SP is adjacent to the 2DEG does the negative charge significantly deplete it.

Output curves for varying SP width (a) and length (b) versus no‑SP device.

Current density maps (Fig. 9) confirm that the SP narrows the vertical channel, while lateral current remains primarily carried by the 2DEG. The overall current density changes only slightly with SP height.

Current density: (a) no‑SP device, (b)–(d) SP‑VFET with different SP dimensions.

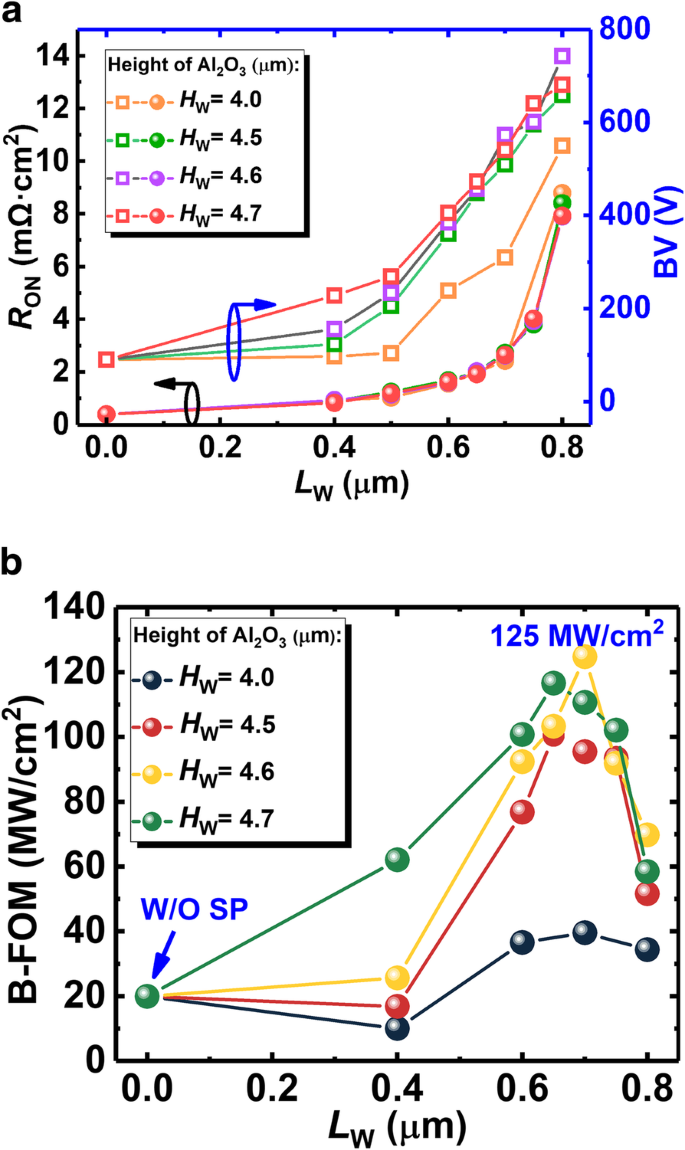

Extracted RON and BV (Fig. 10a) reveal a hyperbolic increase of resistance with SP length, while BV rises until the SP length reaches 700 nm. The BFOM peaks at 125 MW cm−2 for a 700 nm SP length and 4.6 µm height, representing a six‑fold improvement over the unpatterned device.

(a) Extracted RON and BV; (b) BFOM versus SP length and width.

Enhanced BV arises from the SP’s ability to redistribute electric field, mitigating peak concentrations under the p‑GaN cap. The negatively charged interface traps create an additional field that counteracts the depletion‑induced field, thereby expanding the depletion region and reducing leakage paths. Simulated electric field maps (Fig. 12) and cut‑line analyses (Fig. 13) illustrate how increasing SP length flattens the field and concentrates it across the SP edge, which possesses a higher critical field.

Electric field around the gate for 300 V drain: (a) no‑SP, (b)–(d) SP‑VFET.

Horizontal (a) and perpendicular (b) electric field profiles along the SP edge cut‑line.

Conclusion

This study demonstrates a novel GaN vertical FET that leverages a 2DEG channel and a nanoscale substrate pattern to markedly improve BFOM. By mitigating the electric‑field peak under the p‑GaN cap and creating a new high‑field region across the SP, the device achieves a six‑fold BFOM enhancement at a 700 nm SP length and 4.6 µm height. The compact pillar design and minimal SP footprint make the architecture highly suitable for dense power‑integrated applications.

Abbreviations

- nA

- Doping concentration of p‑type GaN

- nD

- Doping concentration of n‑type GaN

- 2DEG

- Two‑dimensional electron gas

- Al0.23GaN

- Aluminum gallium nitride (23 % Al)

- Al2O3

- Aluminum oxide

- BFOM

- Baliga’s Figure‑of‑Merits

- SP

- Substrate pattern

- E‑field

- Electric field

- FET

- Field‑effect transistor

- GaN

- Gallium nitride

- HEMT

- High‑electron‑mobility transistor

- HG

- Gate height

- HW

- Substrate pattern height

- LD

- Device length

- LG

- Gate length

- LP

- p‑GaN cap length

- LW

- Substrate pattern length

- SiN

- Silicon nitride

- SP‑VFET

- Vertical field‑effect transistor with substrate pattern

- WD

- Device depth

- σp

- Polarization charge

Nanomaterials

- Tuning Electronic and Optical Anisotropy in Monolayer GaS via Vertical Electric Fields

- Optimizing Si Nanowire FET Sensors: Photoconductivity, pH Sensitivity, Noise, and Channel Length Effects

- Impact of Morphology and Crystal Structure on Titania Nanotube Thermal Conductivity

- How Substrate Properties Influence LSP Coupling Wavelengths and Intensities in Nanoparticle Systems

- Optimized Mitoxantrone Delivery Using Cholesterol‑Modified Pullulan Nanoparticles: Size‑Dependent Antitumor Efficacy Against Bladder Cancer

- High‑Efficiency, Wide‑Angle Nanohole Absorber Exploiting Void Plasmon Resonance with Ultra‑Strong Field Enhancement

- Double‑Heterojunction AlGaN/GaN Schottky Barrier Diode on Si: A Combined Theoretical and Experimental Analysis

- Step-Thickness Design Boosts DG TFET Efficiency: A Simulation Study

- High-Performance Dopingless SiGe Fin‑Shaped TFET: Enhanced On‑Current and 12‑Order Switching Ratio

- Optimizing Bilateral Gate‑Controlled S/D Symmetric TFETs: Structural Parameters & Bidirectional Performance