Revolutionizing Chip & System Connectivity with MIPI I3C v1.1

Modern mobile devices—from smartphones and wearables to IoT gadgets—are becoming increasingly sophisticated. Designers now face a dense array of sensors and peripherals, all demanding faster, more reliable data pathways to central application processors.

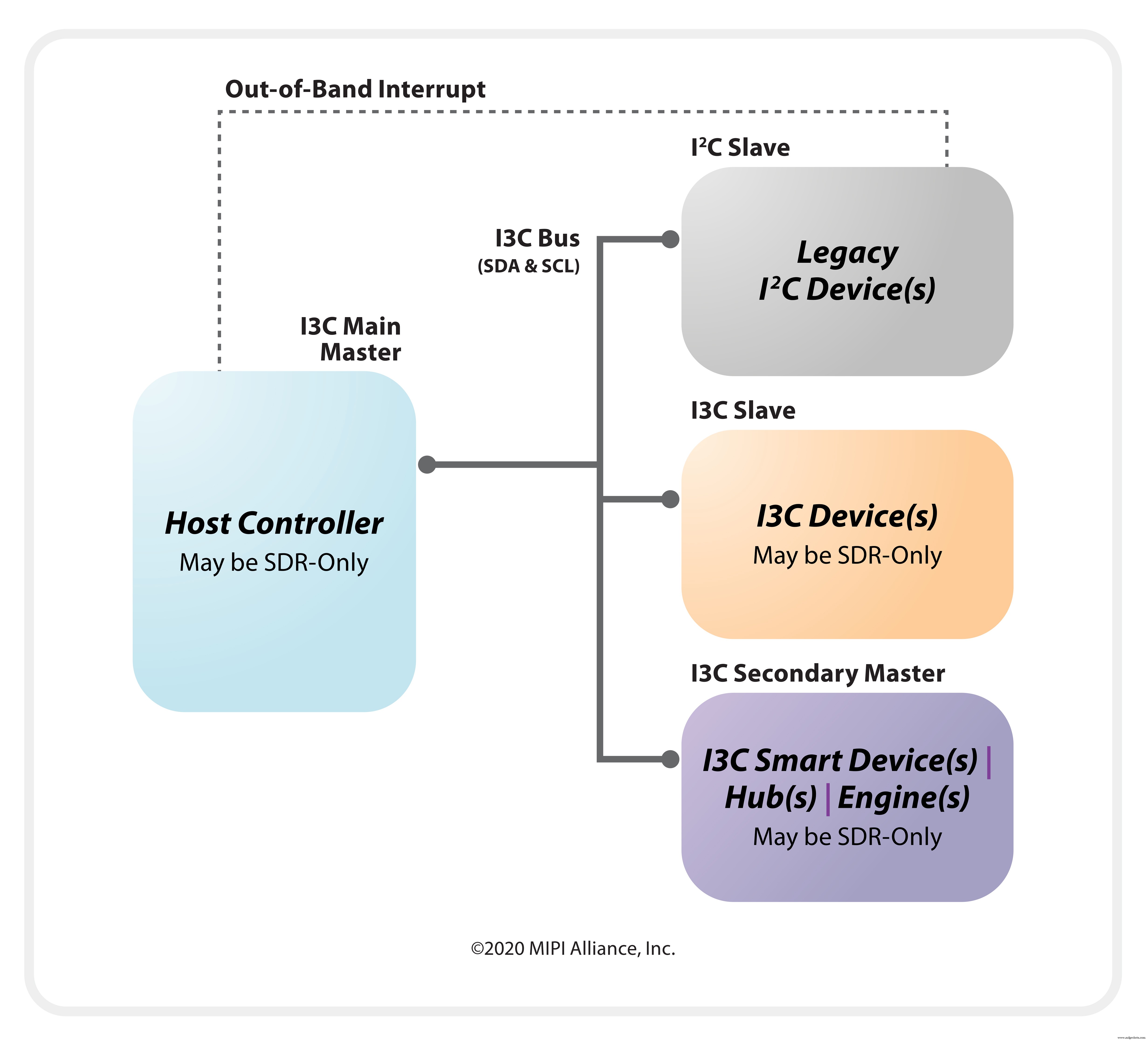

Enter the MIPI I3C v1.1 interface, unveiled on January 15, 2020. This specification unifies all peripherals back to a single application processor at unprecedented speeds while delivering enhanced controllability, manageability, and integrity (Figure 1). With optional single, dual, or quad bus lanes, I3C v1.1 can reach nearly 100 Mbps without added complexity, cost, or prolonged development cycles. A carefully curated set of new features further boosts system reliability and resilience.

Figure 1. MIPI I3C System Diagram (MIPI Alliance)

I3C v1.1 is the ideal choice for today’s system architects seeking a low‑cost, off‑the‑shelf bus solution with minimal silicon and PCB footprints. Its robust ecosystem—comprising a wide range of sensors, actuators, and applications—ensures a seamless transition to tomorrow’s IoT, mobile, and wearable platforms.

Evolving Integration Needs

Understanding the power of I3C v1.1 requires a look at the context in which it was developed. I²C, introduced in 1982, revolutionized short‑distance chip communication and became the de‑facto standard for low‑speed peripherals. However, its limitations are now evident in complex, high‑performance devices: performance can drop from a target 1 MHz to as low as 400 kHz in real‑world systems.

In 2017, MIPI introduced I3C to address these shortcomings. The working group designed a protocol that maintains backward compatibility with I²C while offering improved performance, power efficiency, and simplified integration—especially critical for compact, space‑constrained form factors. I3C’s early adoption in sensors, actuators, haptics, IR/UV sensing, NFC, ToF cameras, touchscreens, transducers, and ultrasonic sensors demonstrates its versatility.

Unlocking New Application Spaces

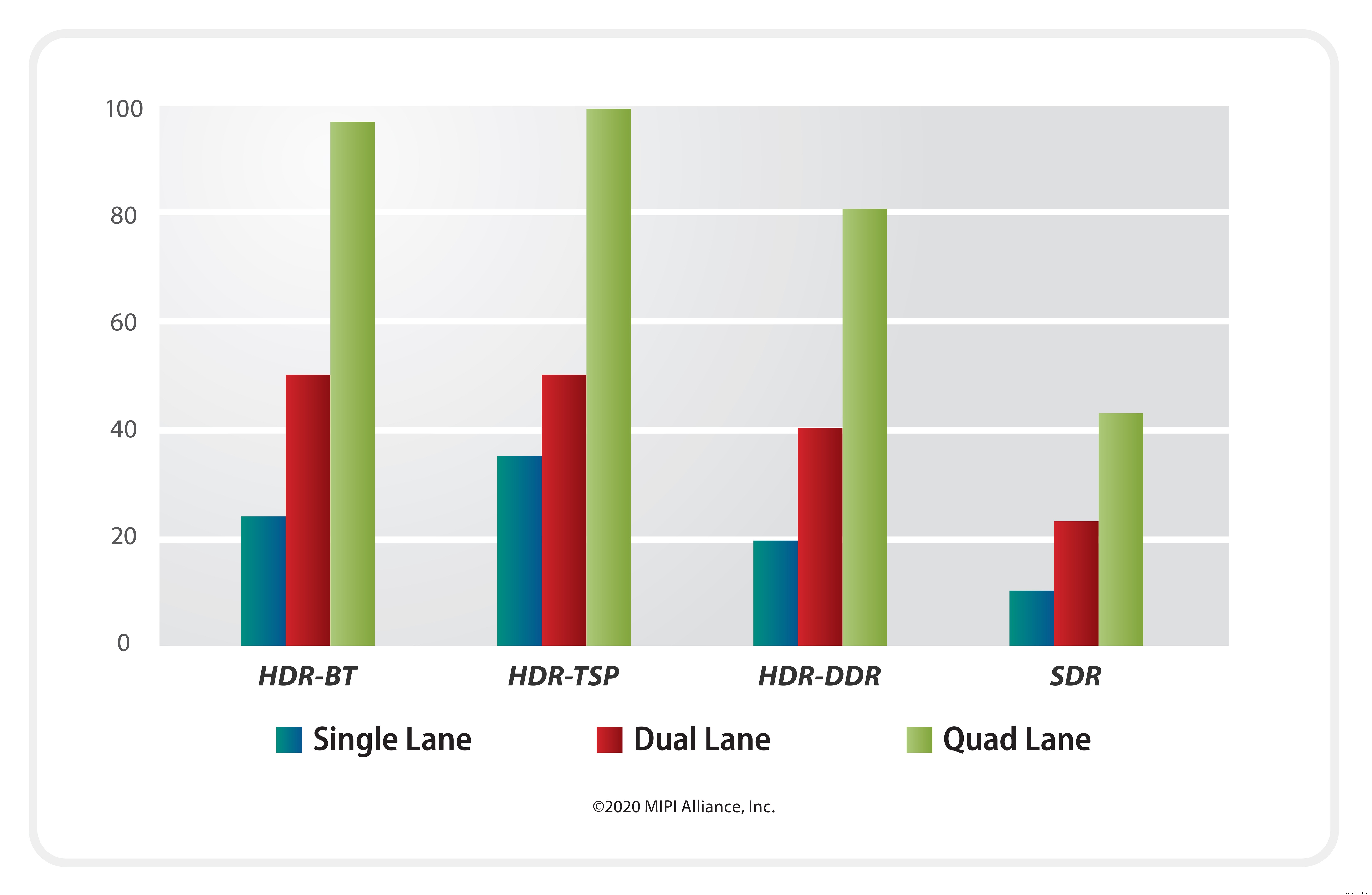

With I3C v1.1, data transfer can occur across multiple lanes in all modes, including the new bulk transport mode (HDR‑BT). Extending from two to three wires doubles throughput, reducing host wake‑time and cutting power consumption—an essential advantage for always‑on imaging and other battery‑driven use cases.

Figure 3. MIPI I3C Multi‑Lane Effective Bit Rates, in Mbps (MIPI Alliance)

Version 1.1 introduces comprehensive flow control, advanced error detection and recovery, grouped addressing, outsider end transfer, slave reset, and enhanced common command code (CCC) capabilities. These features enable host processors to monitor peripheral health—tracking heat, performance, integrity, and security—within a single, unified bus. Unlike legacy solutions that require multiple protocols and custom glue logic, I3C offers a cohesive, single‑bus architecture that simplifies design and reduces pin count.

Beyond traditional SoCs, I3C v1.1’s flexibility makes it suitable for system‑in‑package (SiP) integrations, memory sideband channels (e.g., DIMM5 SDRAM), server management, debug communication, touchscreen control, and more. Its high‑speed, low‑power transport is especially valuable for battery‑operated IoT edge devices, reducing both interface complexity and power draw.

Because many of the enhancements in v1.1 directly address the pain points of legacy I²C and SPI—such as standardized reset, robust error handling, and efficient flow control—the industry is well positioned to adopt I3C en masse. The upgrade path is clear: modernize from decades‑old interfaces to a future‑ready, scalable bus.

Already At Work Anticipating Tomorrow’s Demands

Across mobile, automotive, PCs, data centers, drones, industrial, and IoT sectors, developers can leverage a vibrant, interoperable ecosystem supported by MIPI Alliance. Collaborations with JEDEC, for example, have yielded the 1.0 V JEDEC Module SidebandBus—a superset of the MIPI I3C Basic bus—further expanding the technology’s reach.

Companies are encouraged to participate in MIPI Alliance workshops and specification development sessions to shape the next wave of chip and system communication innovations.

So what lies ahead for I3C?

The MIPI I3C Working Group is actively refining the specification to meet evolving needs—considering longer reach, automotive requirements, higher speeds, new multi‑lane configurations, standardized connectors, and more. The result will be a continuously relevant, cutting‑edge interface that empowers designers to push the boundaries of connectivity.

Embedded

- Operating System Fundamentals: Key Components and Functions

- Virtual Machines Explained: Types, Architecture, and Key Advantages

- Embedded Systems Fundamentals & Real-World Applications

- Intel Launches Loihi 2: Next‑Gen Neuromorphic Chip with Advanced Programmability and 3D Scaling

- Expert Guide to Planning & Designing Power Distribution Systems

- MIPI Alliance Unveils I3C v1.1: A Modern Data Communications Standard

- Embedded Systems & System Integration: Modern Architecture & Connectivity

- Build an Arduino Security & Alarm System – Step-by-Step Tutorial

- Cramer's Rule Calculator: Solve 2‑ and 3‑Equation Linear Systems Quickly

- Understanding IT vs. OT: Key System and Device Differences