Intel Launches Loihi 2: Next‑Gen Neuromorphic Chip with Advanced Programmability and 3D Scaling

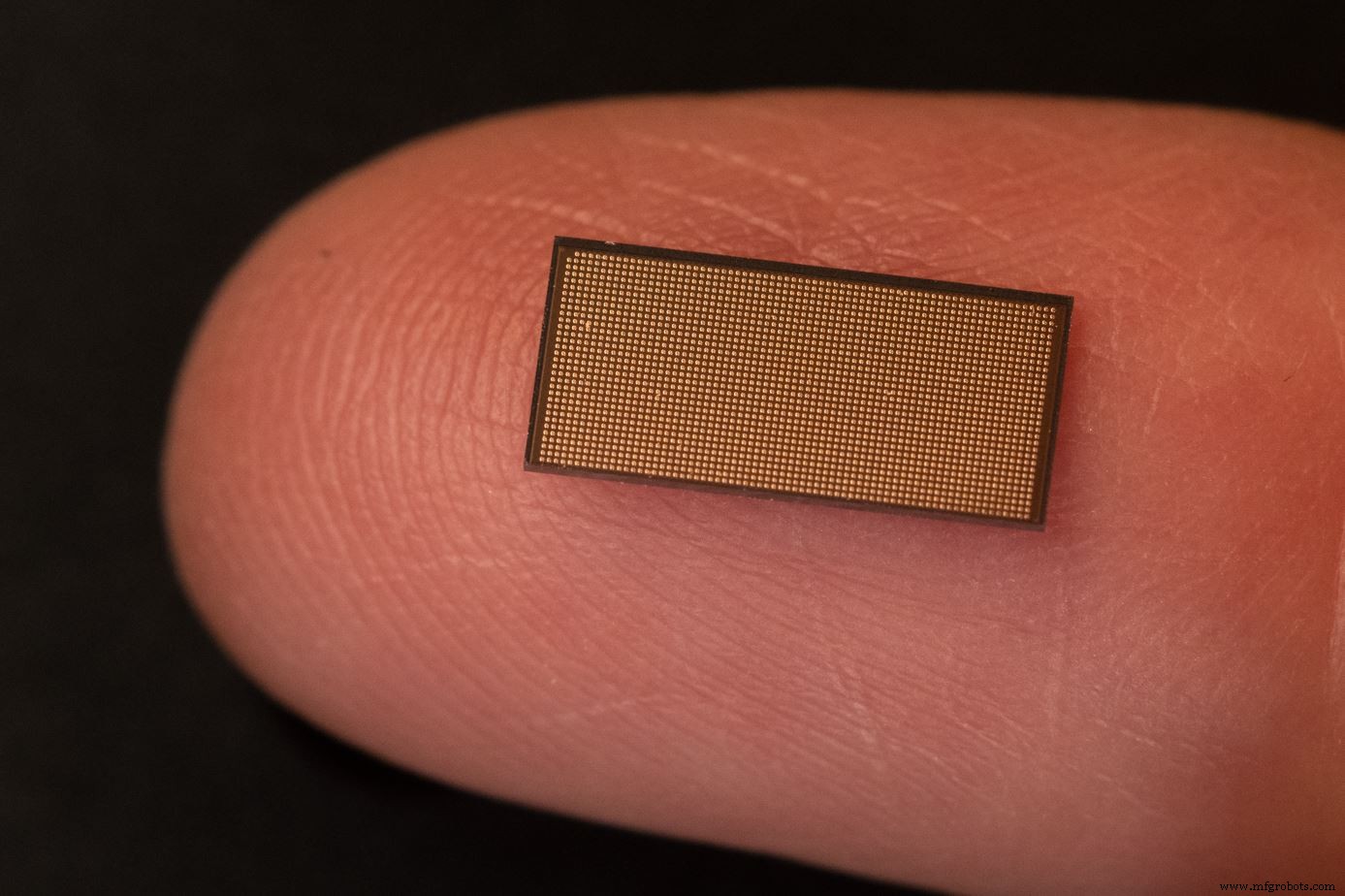

Intel has announced Loihi 2, its second‑generation neuromorphic processor built on the pre‑production Intel 4 process node. The new chip is tailored for researchers exploring next‑generation spiking neural networks (SNNs) and delivers substantial gains in programmability, density, and scalability.

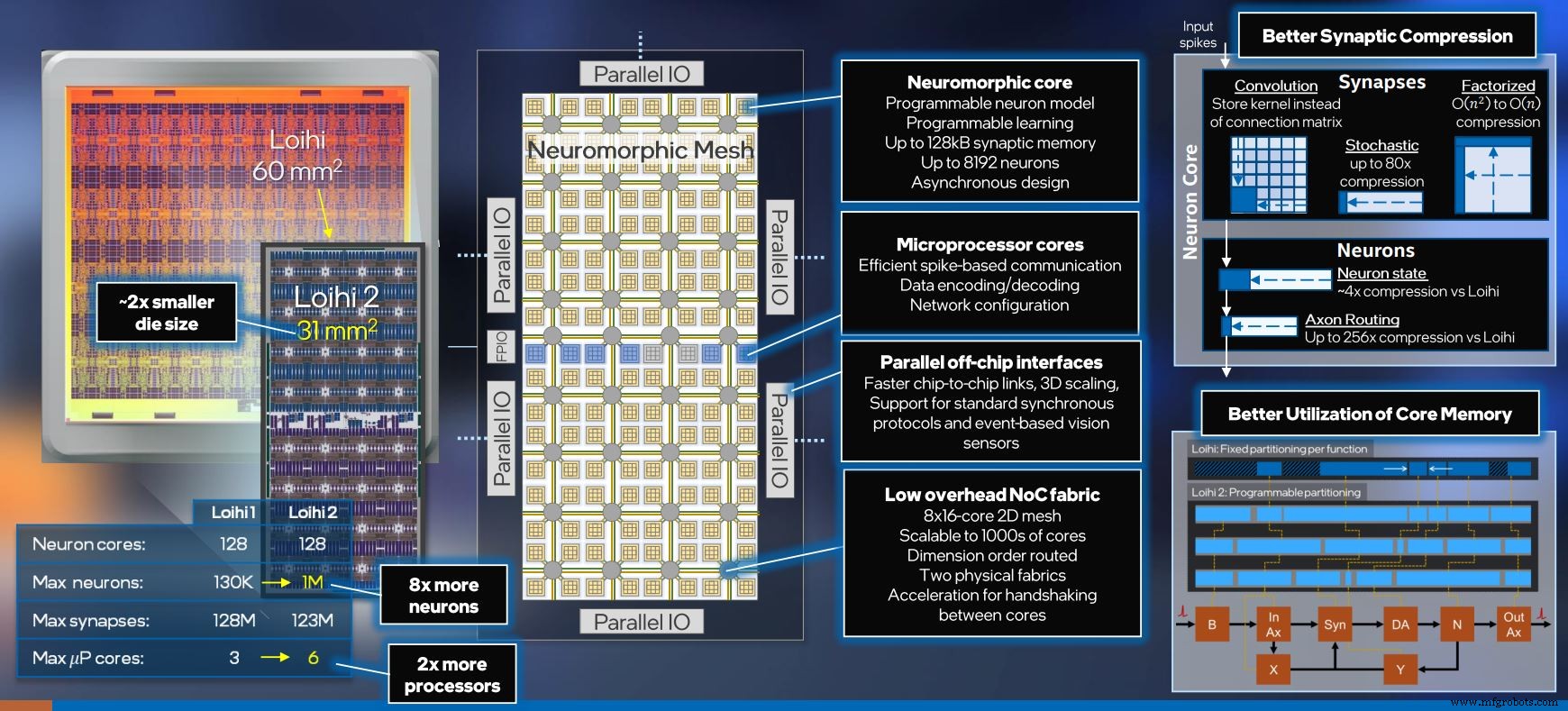

Loihi 2 introduces a fully programmable neuron instruction set that allows spikes to carry integer payloads instead of the binary 0/1 used in Loihi 1. This change increases model expressiveness and reduces the number of neurons required for a given task.

Alongside the hardware, Intel unveiled Lava – an open‑source software stack that unifies event‑driven programming, heterogeneous execution, and community‑driven code sharing. The framework is designed to accelerate development of neuromorphic applications and to bridge the gap between research and deployment.

While conventional CPUs use fine‑grained memory, Loihi stores data directly inside each core, enabling truly asynchronous operation that matches the timing‑based logic of biological brains. According to Mike Davies, director of Intel’s Neuromorphic Computing Lab, “The chip’s computation emerges from the dynamic interaction of its elements, reaching an equilibrium that encodes the answer.”

First‑generation Loihi prototypes have already been deployed in diverse scenarios: adaptive robot‑arm controllers that reduce wear, olfactory recognition systems that learn odors faster than deep‑learning baselines, and train‑scheduling engines that react to real‑time disruptions. These use cases underscore the platform’s potential for real‑world, low‑power intelligence.

Key Enhancements in Loihi 2

Loihi 2 features 128 cores like its predecessor, but the neuron count is multiplied eightfold. The overall die area is halved thanks to the Intel 4 process, delivering roughly a 15‑fold increase in network capacity per square millimeter. Memory is partitioned into flexible banks and compressed, freeing space for additional neurons and synapses.

With the new instruction set, developers can program custom neuron models that incorporate arithmetic, comparison, and control‑flow operations. This micro‑code capability unlocks richer SNN architectures and enables efficient mapping of complex algorithms.

Spikes on Loihi 2 carry a configurable integer payload, allowing event‑based messaging that supports sigma‑delta neural networks (SDNNs). SDNNs compute graded activations like traditional DNNs but transmit only significant changes, providing faster inference than the strictly timing‑based approach of Loihi 1.

Loihi 2 can achieve up to 10× speed‑up at the circuit level and processes networks 5,000× faster than biological neurons. The design introduces 3D scaling ports that enable planar chip meshes to become volumetric arrays, with inter‑chip bandwidth quadrupled and spike traffic compressed tenfold. Overall, the system delivers a 60‑fold capacity boost for most workloads.

Three‑factor learning, a cutting‑edge neuromorphic training paradigm, is now supported, allowing researchers to approximate back‑propagation on hardware. This opens new pathways for training deep architectures directly on Loihi 2.

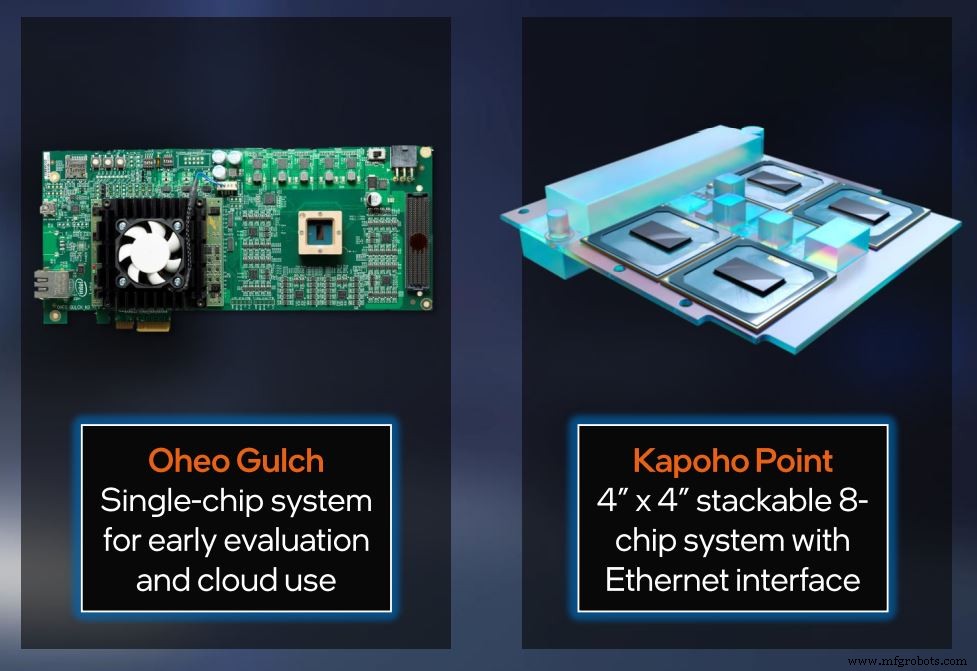

Loihi 2 Availability

Researchers can acquire the single‑chip Oheo Gulch board for rapid prototyping, followed by the eight‑chip Kapoho Point system that offers an Ethernet interface for stackable deployments. These boards provide a low‑latency, high‑throughput platform for edge applications such as robotics.

Lava – The Open‑Source Software Ecosystem

While hardware has progressed rapidly, software support has lagged. Lava aims to fill that gap by offering a unified API for event‑based, asynchronous programming and heterogeneous execution. It enables developers to prototype on CPUs and then offload compute‑intensive kernels to Loihi 2, lowering the barrier to entry and fostering collaboration across labs.

Lava is hosted on GitHub and welcomes contributions from the neuromorphic community. By providing shared building blocks and example models, the framework seeks to accelerate innovation and drive commercialization of neuromorphic technologies.

Originally published on EE Times.

Related Contents:

- Making the case for neuromorphic chips for AI computing

- Spiking neural network targets Arm chips

- Advanced AI chips to build on emerging memory technologies

- Neuromorphic AI chips for spiking neural networks debut

- The benchmarking conundrum of neuromorphic computing

For more Embedded, subscribe to Embedded’s weekly email newsletter.

Embedded

- Revolutionizing Chip & System Connectivity with MIPI I3C v1.1

- Satellite Navigation & Software‑Defined Radio: Enhancing GNSS Performance

- Würth Elektronik Expands Optoelectronics Portfolio with Matching Photodiodes and Phototransistors

- Comprehensive .NET and C# Version History Guide

- Siemens Industry Solutions: Integrated IoT Software & Hardware for CNC and Automation

- Maximize Efficiency: Inventory Management Software Features & Benefits

- Optimized 3D Design Software for CNC Tube Bending & Cutting

- How Modern ERP Systems Streamline Manufacturing Operations

- GE Leads Innovation in Industrial Robot Automation Software

- Revolutionizing Robotics: New Hardware and Software Breakthroughs