Designing High‑Performance Interconnects Across PCIe Generations

PCI Express and the Hunger for Bandwidth

PCI Express® (PCIe®) has become the industry standard for high‑performance interconnects, linking CPUs, GPUs, storage, and networking peripherals with efficient point‑to‑point serial links. By scaling channel count and signaling speed, PCIe delivers the bandwidth required for modern applications.

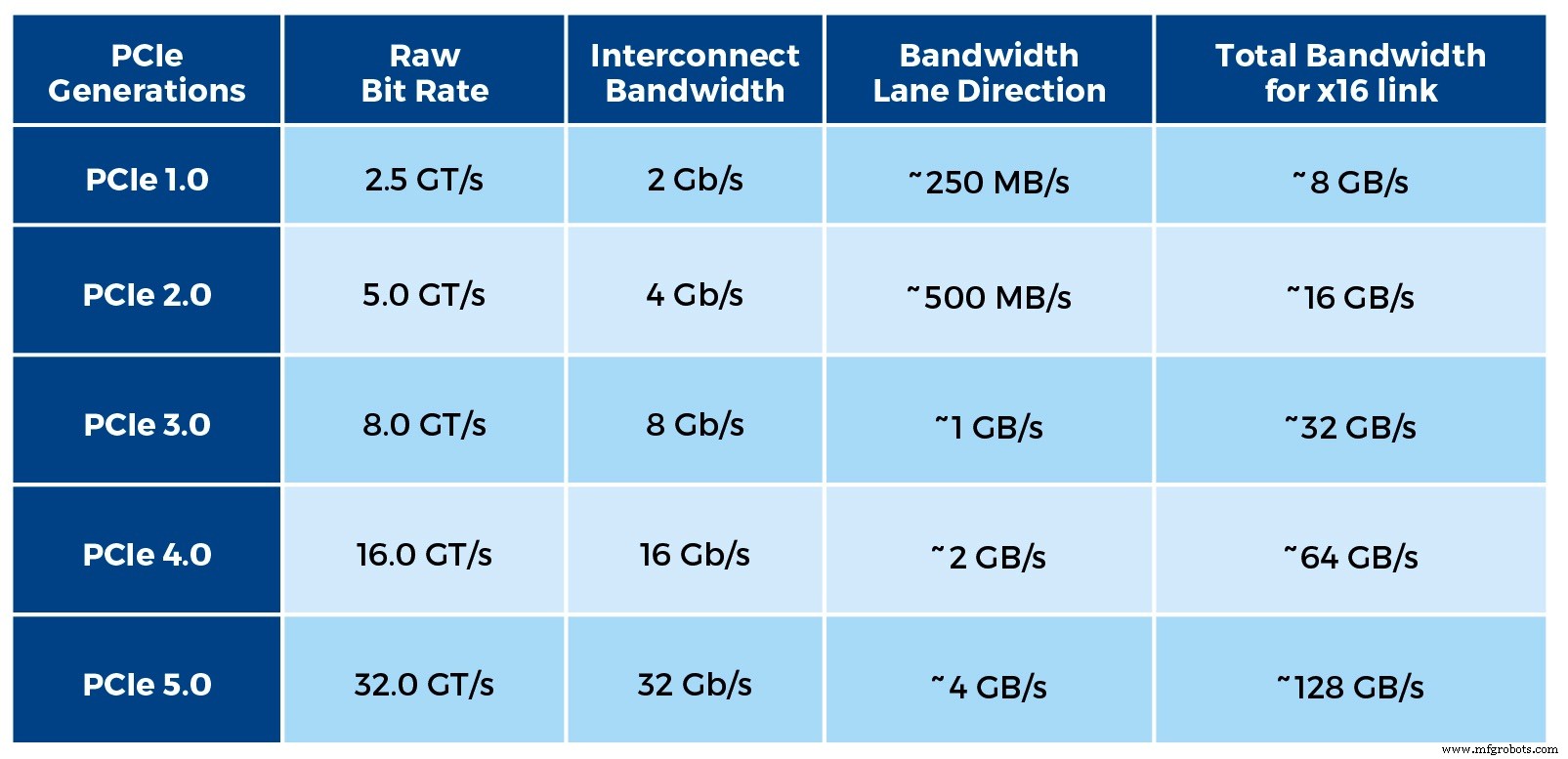

Since its 2002 debut at 2.5 GT/s (8 GB/s on a ×16 link), PCIe has doubled bandwidth with each new generation—PCIe 2.0 in 2006, PCIe 3.0 in 2010, and the recent jumps to PCIe 4.0 and 5.0, which together push aggregate throughput well beyond 50 GB/s per lane.

PCI Express has become the reference high‑performance interconnect for a wide range of system designs.

(Source: Diodes Inc.)

The surge of cloud services—social media, video streaming, and big‑data analytics—has amplified the demand for blazing‑fast links inside massive data centers. The proliferation of IoT, smart cities, industry 4.0, and wearables is flooding servers with terabytes of data that must be captured, stored, and analyzed in real time.

Connected vehicles will further compound traffic, driving the need for ultra‑low‑latency, high‑bandwidth pathways to support autonomous driving and AI inference workloads that dominate next‑generation data centers.

Responding to these pressures, PCIe 4.0 (2017) and PCIe 5.0 (2019) were introduced, as shown in Figure 1, offering aggregate speeds that keep pace with 400 GbE and beyond.

Figure 1: Aggregate speeds offered by PCIe versions (Source: Diodes Inc.)

PCIe 5.0 is poised to become the backbone of next‑generation data centers, bridging the transition from 100 GbE to 400 GbE. The protocol’s evolution mirrors Ethernet’s, maintaining a balanced, bottleneck‑free data path across the stack.

Legacy PCI Standards Remain Current

With PCIe 5.0 rolling out and PCI‑SIG already working on PCIe 6.0 (targeted for 2021), PCIe remains the go‑to solution for high‑throughput peripheral communication. Its key advantage is backward compatibility—multiple generations coexist in a single board or system, letting designers keep older modules while upgrading the rest of the platform.

Solving Implementation Challenges

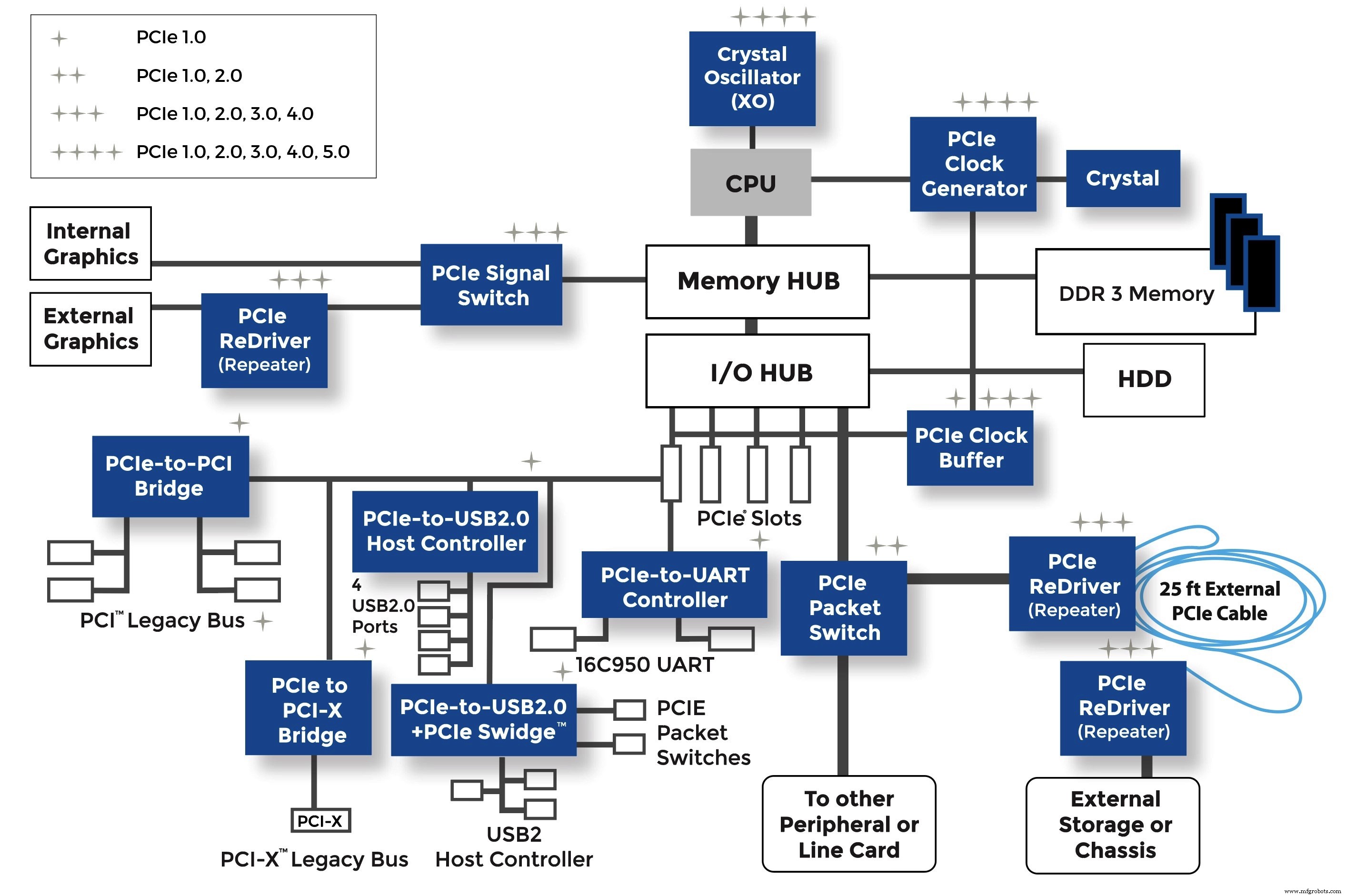

Although newer generations bring higher data rates, they also raise signal‑margin demands and design complexity. Bridging across generations—or to other interfaces such as USB, PCI‑X, or UART—requires careful component selection.

Diodes Inc. offers a comprehensive line of PCIe support ICs, including clock generators, buffers, controllers, packet switches/bridges, ReDriver™ chips, and high‑speed multiplexers, as illustrated in Figure 2.

click for larger image

Figure 2: An example of the PCIe solutions available from Diodes Inc. (Source: Diodes Inc.)

ReDriver chips provide a cost‑effective, low‑latency means to boost signal integrity on long traces or cables. By applying equalization and pre‑emphasis, they recover margin lost to transmission‑line attenuation, ensuring a low bit‑error rate without the added complexity of a full retimer.

Bridges and switches translate between host and endpoint devices, across protocol layers, or between PCIe and legacy PCI/PCI‑X, USB, or UART. Multi‑port packet switches expand a single root complex to multiple peers, while devices like the PI7C9X442SL “swidge” combine a PCIe‑to‑USB 2.0 bridge with internal switching, allowing a single PCIe ×1 upstream port to fan out to two PCIe ×1 downstream ports and four USB 2.0 ports.

Diodes’ passive bidirectional PCIe 1.0/2.0/3.0 multiplexers/demultiplexers enable single‑lane expansion to multi‑lane bandwidth, ideal for graphics or compute acceleration. Their clock buffers and PLL‑based generators—such as the 1.8 V PI6CG18xxx and 1.5 V PI6CG15xxx families—provide low‑jitter timing across 2‑, 4‑, and 8‑channel configurations, with on‑chip termination that trims up to 32 components from the BOM.

Conclusion

PCIe’s longevity, backward compatibility, and robust ecosystem of bridging, buffering, and driving solutions make it the preferred interconnect for embedded systems, high‑end desktops, and data‑center AI workloads alike. By selecting the right mix of PCIe devices, designers can build scalable, cost‑effective platforms that meet today’s bandwidth demands and tomorrow’s expansion needs.

Embedded

- Liquid Additive Manufacturing: Crafting 3D Objects with Liquid Materials

- Build Scalable Serverless Mobile Apps with React Native & AWS

- Getting Started with FPGA Development: Building a 4‑Bit Adder on Xilinx Artix‑7

- Build a Robot with Raspberry Pi and Python: A Complete Guide

- Build a Self‑Balancing Segway with Raspberry Pi

- Building a High‑Performance Reliability Team: A Practical Guide

- High‑Performance 3D‑Printed Fixtures: Solving Skilled Labor Shortages and Boosting Quality

- Build a SmartThings‑Enabled IR Bridge with Arduino UNO & ThingShield

- Designing a Cost‑Effective Work Cell with Refurbished Robots

- Centralized Control of Multiple Compressors for Energy Efficiency and System Stability