Low‑Temperature ALD Flexible Hf0.5Zr0.5O2 Memristor Exhibiting Short‑ and Long‑Term Synaptic Plasticity

Abstract

Artificial synapses are the cornerstone of neuromorphic circuits, offering a pathway to transcend the von Neumann bottleneck. Using a low‑temperature atomic layer deposition (ALD) process, we fabricated a flexible electrical synapse based on Hf0.5Zr0.5O2 (HZO). The device displays bipolar resistive switching governed by the gradual formation and rupture of Ag‑ion conductive filaments. Under sequences of pre‑synaptic spikes, the memristor reproduces key biological behaviors—short‑term plasticity (STP), long‑term potentiation/depression (LTP/LTD), paired‑pulse facilitation/depression (PPF/PPD), and forgetting dynamics—thus integrating memory and learning in a single, pliable platform poised for next‑generation neuromorphic hardware.

Background

The conventional von Neumann architecture struggles with data traffic between processors and memory, limiting performance in data‑intensive tasks [1]. Neuromorphic computing emulates cortical circuits, providing intrinsic learning and memory within a unified system [2,3]. Central to this approach are electronic synapses that mimic the adaptive conductance of biological junctions. Recent advances have demonstrated a variety of memristive synapses—including two‑terminal devices and three‑terminal ionic‑defect transistors—capable of reproducing phenomena such as long‑term depression/potentiation (LTD/LTP), paired‑pulse fluctuation (PPF), paired‑pulse depression (PPD), and spike‑timing‑dependent plasticity (STDP) [4–8]. LTD/LTP are essential for pattern recognition and AI tasks [9–11], while STP underlies temporal filtering and rapid signal transmission [12].

Hf0.5Zr0.5O2 (HZO) stands out as a high‑k dielectric compatible with CMOS processes, yet most reported HZO‑based synapses require high‑temperature fabrication that precludes flexible substrates [20–23]. Flexible synaptic devices are crucial for wearable AI, yet high‑temperature steps introduce defects during transfer, limiting scalability [26,27]. Low‑temperature ALD offers a substrate‑friendly route to large‑area, defect‑free flexible arrays.

Here we present a PET/ITO/HZO/Ag memristor fabricated at 130 °C via ALD. The device shows gradual resistance switching and faithfully reproduces a suite of synaptic plasticity behaviors, making it a promising candidate for hardware neuromorphic systems.

Methods

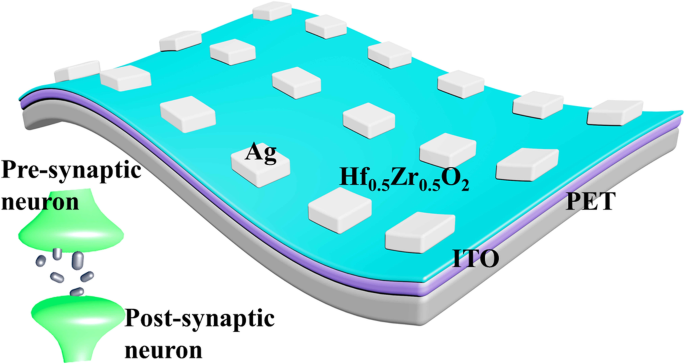

The flexible stack was built on ITO‑coated polyethylene terephthalate (PET). The substrate was sequentially cleaned with acetone, isopropanol, and deionized water, then dried under nitrogen. A 10‑nm HZO film was deposited by ALD (N2 carrier) using TEMAH, TEMAZ, and H2O precursors at 130 °C. Subsequently, a 50‑nm Ag top electrode (100 × 100 µm²) was defined by physical vapor deposition, photolithography, and lift‑off. The resulting PET/ITO/HZO/Ag structure (Fig. 1) maps Ag and ITO to pre‑ and post‑synaptic neurons, respectively.

Schematic of a biological synapse and its artificial counterpart, fabricated on PET via low‑temperature ALD.

Electrical measurements were conducted with an Agilent B1500A parameter analyzer in ambient air at room temperature. The bottom electrode was grounded while the top electrode received the bias.

Results and Discussion

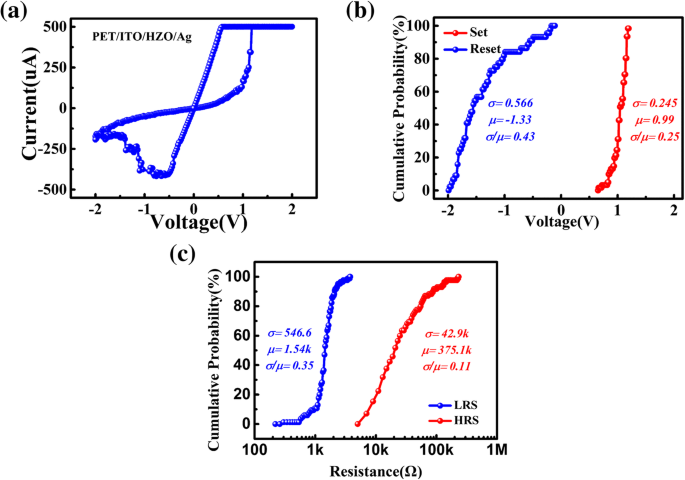

Figure 2a displays the typical bipolar resistive switching curve under a 500 µA compliance. A positive sweep from 0 → 2 V sets the device from high‑resistance state (HRS) to low‑resistance state (LRS), whereas a negative sweep from 0 → −2 V resets it. The gradual transition in both polarities confirms the device’s suitability for synaptic emulation.

Statistical analysis of 200 consecutive DC sweeps (Fig. 2b) yields mean set and reset voltages of 0.99 V and −1.33 V, with standard deviations of 0.245 V and 0.566 V, respectively. The coefficient of variation is lower for the set process, reflecting better uniformity. The ON/OFF ratio exceeds 300 (Fig. 2c), demonstrating a robust resistive window.

a DC sweep revealing bipolar resistive switching. b Distribution of set and reset voltages over 200 cycles. c ON/OFF ratio and resistance statistics at 0.1 V read.

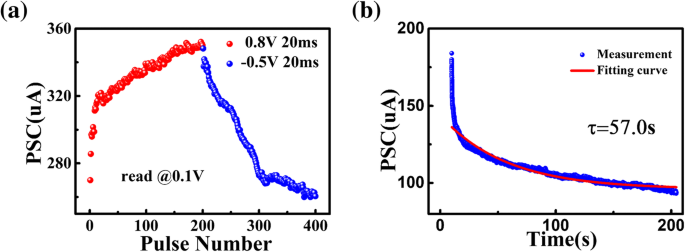

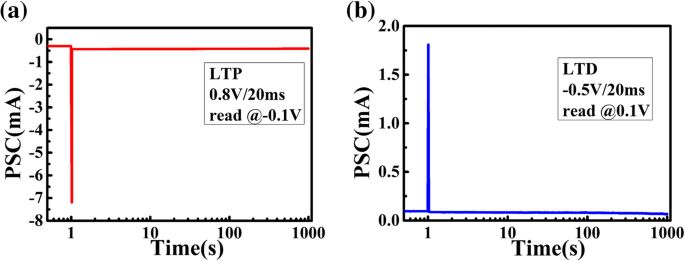

Applying consecutive voltage pulses modulates the device conductance in a controlled manner. With 200 positive pulses (0.8 V, 20 ms) followed by 200 negative pulses (−0.5 V, 20 ms), the conductance increases (LTP) and decreases (LTD) progressively (Fig. 3a), illustrating long‑term plasticity. After pulse sequences, the post‑synaptic current (PSC) relaxes toward an intermediate state, mimicking biological forgetting (Fig. 3b). The decay fits the Kohlrausch function: I(t)=I0+A exp(−t/τ) with τ = 57 s, quantifying the forgetting time constant.

a Gradual conductance changes under LTP/LTD programming. b PSC decay after 100 pulses, fitted to the Kohlrausch model.

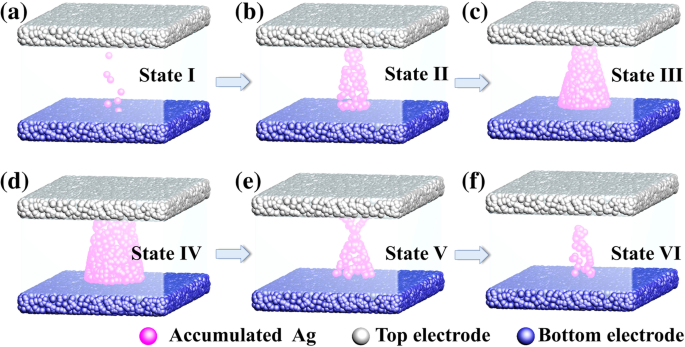

The underlying mechanism involves Ag‑ion migration forming conductive filaments (CF). Positive bias oxidizes Ag to Ag+, which migrates and reduces at the bottom electrode, thickening the CF (states I–III) and enhancing conductance. Negative bias ruptures the filament, reducing conductance (states d–f) (Fig. 4). This reversible CF dynamics underpins the observed LTP/LTD.

a–c CF growth during successive positive pulses (LTP). d–f CF rupture during successive negative pulses (LTD).

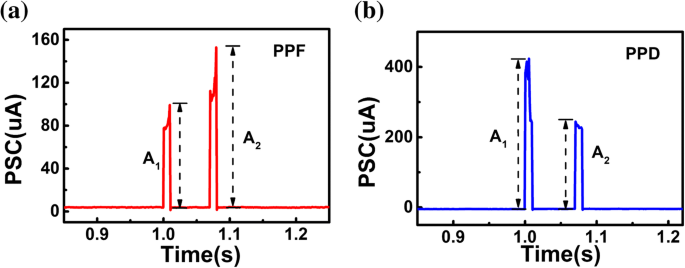

Short‑term plasticity is evidenced by paired‑pulse facilitation (PPF) and depression (PPD). A 2 V, 10 ms pair with a 60 ms interval enhances the second PSC (PPF), while a −1.5 V pair suppresses it (PPD) (Fig. 5). These behaviors mirror synaptic temporal filtering observed in biology.

a PPF induced by a pair of positive spikes. b PPD induced by a pair of negative spikes.

Retention tests over 1000 s confirm stable post‑synaptic currents in both excitatory (positive) and inhibitory (negative) states (Fig. 6), underscoring the device’s potential for long‑term memory storage.

a Long‑term retention after a positive pulse. b Stability after a negative pulse over 1000 s.

Conclusions

We have demonstrated a PET/ITO/HZO/Ag flexible memristor fabricated by low‑temperature ALD that exhibits reliable bipolar switching and a comprehensive set of synaptic plasticity phenomena—LTP, LTD, PPF, PPD, and forgetting. The gradual conductance modulation originates from controllable Ag‑ion conductive filaments. This device constitutes a viable building block for scalable, flexible neuromorphic hardware capable of simultaneous learning and memory.

Abbreviations

- ALD

Atomic layer deposition

- HRS

High‑resistance state

- LRS

Low‑resistance state

- LTD

Long‑term depression

- LTP

Long‑term potentiation

- STP

Short‑term plasticity

Nanomaterials

- Impact of AlN Layer Thickness on Interface and Electrical Performance of ALD‑AlN on c‑Plane GaN

- High-Performance Silicon Nanowire Heterojunction Solar Cells Using Al₂O₃ Passivation via Atomic Layer Deposition

- Ultra‑Thin TiO₂ Nanomembranes via Atomic Layer Deposition Deliver Record‑High Capacitance for Pseudocapacitor Electrodes

- Ru-Based RRAM Devices Show Negative Differential Resistance: Insights from Atomic Layer Deposition Fabrication

- Boosting PERC Solar Cell Performance: ALD‑Deposited Al₂O₃ with Optimized Two‑Step Annealing for Superior Si Passivation

- Ultrathin Al₂O₃ Layers Enhance Mg‑Doped LiNbO₃ Film Reliability and Fatigue Endurance

- Optimizing Buffer Layers via Atomic Layer Deposition for High‑Performance Vertically Aligned Carbon Nanotube Arrays

- Enhancing Memory Window and Endurance of Hf0.5Zr0.5O2 FeFETs with ZrO2 Seed Layers: Fast‑Pulse Characterization

- Optimizing Energy Band Alignment in AZO/β‑Ga₂O₃ (𝟐01) Heterojunctions via Atomic Layer Deposition

- Precursors Determine Ferroelectric Performance in ALD Hf0.5Zr0.5O2 Thin Films: TEMA vs. TDMA