Enhancing Memory Window and Endurance of Hf0.5Zr0.5O2 FeFETs with ZrO2 Seed Layers: Fast‑Pulse Characterization

Abstract

HfO₂‑based ferroelectric field‑effect transistors (FeFETs) with a metal/ferroelectric/insulator/semiconductor (MFIS) gate stack are emerging as strong candidates for high‑density, high‑speed non‑volatile memories. Although their retention performance meets industrial demands, the memory window (MW) and endurance still fall short of the stringent requirements for large‑scale deployment. In this study we examine the effect of a crystalline ZrO₂ seed layer on the MW, retention, and endurance of Hf₀.₅Zr₀.₅O₂ (HZO) FeFETs, using fast voltage‑pulse measurements. The HZO FeFET incorporating the ZrO₂ seed layer shows a larger initial MW of 1.4 V, a 10‑year extrapolated MW of 0.9 V, and markedly improved endurance (exceeding 10⁴ switching cycles) compared with devices lacking the seed layer. These findings confirm that a direct crystalline high‑k/Si gate stack can further enhance the performance and reliability of HfO₂‑based FeFETs.

Background

HfO₂‑derived ferroelectric thin films have attracted significant interest for FeFET gate stacks because of their compatibility with CMOS processes and excellent scalability. Among the many gate‑stack architectures, the MFIS structure is particularly attractive because it aligns with current MOS device designs and can be integrated with high‑k metal‑gate (HKMG) technologies. Consequently, MFIS FeFETs have been explored for embedded non‑volatile memories, negative‑capacitance FETs, neuromorphic devices, and logic‑in‑memory circuits [1–8].

State‑of‑the‑art MFIS FeFETs fabricated using HKMG processes have demonstrated high integration density and rapid write speeds [9,10]. However, for non‑volatile memory applications, a large MW and robust retention and endurance are essential [11–14]. HfO₂‑based FeFETs typically offer reliable retention (10‑year extrapolation) [15–17], but their endurance ranges from 10⁴ to 10⁷ switching cycles [17–23]. Theoretical studies suggest that a high‑k insulator can reduce the electric field across the MFIS stack, thereby mitigating band bending and improving both MW and endurance [12,14]. Experimentally, increasing the dielectric constant of the ultrathin insulator layer (e.g., replacing SiO₂ with SiON) has been shown to enhance endurance and MW [13]. Prior work has also indicated that inserting a crystalline ZrO₂ layer improves the crystalline quality of HZO films and suppresses the deleterious monoclinic phase, resulting in an MW of 2.8 V measured by DC sweep [24].

Here we present a systematic study of the MW, retention, and endurance of HZO FeFETs with and without a crystalline ZrO₂ seed layer, characterized by fast positive and negative voltage pulses. We discuss how the seed layer influences the ferroelectric properties, electrical reliability, and overall device performance.

Methods

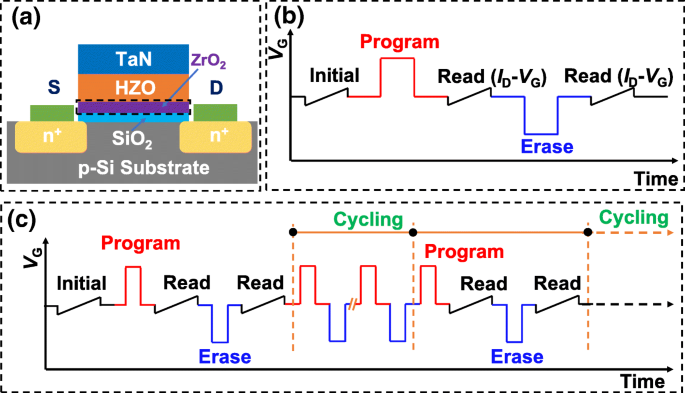

Both n‑channel FeFETs—with and without a ZrO₂ seed layer—were fabricated using a gate‑last process as detailed in Ref. [24]. The ZrO₂ seed and the HZO layers were deposited at 300 °C by atomic‑layer deposition (ALD). Device geometry is shown in Fig. 1a, with channel width W = 80 µm and length L = 7 µm. In addition, TaN/HZO/TaN and TaN/HZO/ZrO₂/TaN capacitors were fabricated to evaluate the ferroelectric properties of the HZO films. Polarization–voltage (P–V) hysteresis loops were measured using a Radiant Technologies RT66A ferroelectric tester, while FeFET characteristics were recorded with an Agilent B1500A analyzer equipped with a pulse generator (B1525A) [20].

Two main test sequences were employed (Fig. 1b,c). For MW and retention studies, program/erase (P/E) pulses were first applied to the FeFET gates, followed by read operations at various time intervals using I_D–V_G sweeps (V_D = 0.1 V). The threshold voltage V_TH was extracted at a drain current of 10⁻⁷ A·W/L [25], and the MW was defined as the difference in V_TH between the programmed and erased states. Endurance was assessed by measuring the MW after a specified number of alternating P/E pulses.

a Schematic of the fabricated FeFETs. The crystalline ZrO₂ seed layer is highlighted by black gridlines. b, c Test sequences for MW and endurance measurements.

Results and Discussion

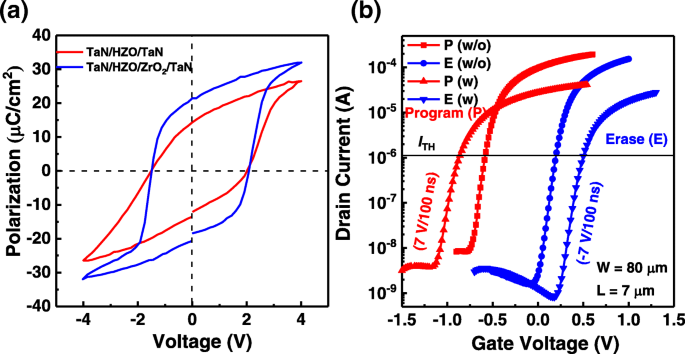

Figure 2a shows the P–V hysteresis loops of the TaN/HZO/TaN and TaN/HZO/ZrO₂/TaN capacitors. The inclusion of the crystalline ZrO₂ seed layer markedly improves the ferroelectric response, consistent with previous reports [26], and confirms that the seed layer enhances the crystallinity of the HZO film and suppresses the monoclinic phase [24].

a P–V hysteresis loops of TaN/HZO/TaN and TaN/HZO/ZrO₂/TaN structures measured at 4 V and 5 kHz. b I_D–V_G curves of HZO FeFETs with (w) and without (w/o) ZrO₂ seed layers after a program pulse (+7 V/100 ns) and an erase pulse (−7 V/100 ns).

In the FeFETs, counter‑clockwise I_D–V_G characteristics confirm that the MW originates from ferroelectric polarization switching rather than charge trapping. The FeFET with the ZrO₂ seed layer achieves an MW of 1.4 V—nearly 1.8 times larger than the 0.8 V observed in the seed‑free device—and matches the best values reported to date [9,11,14,17,21–23,27].

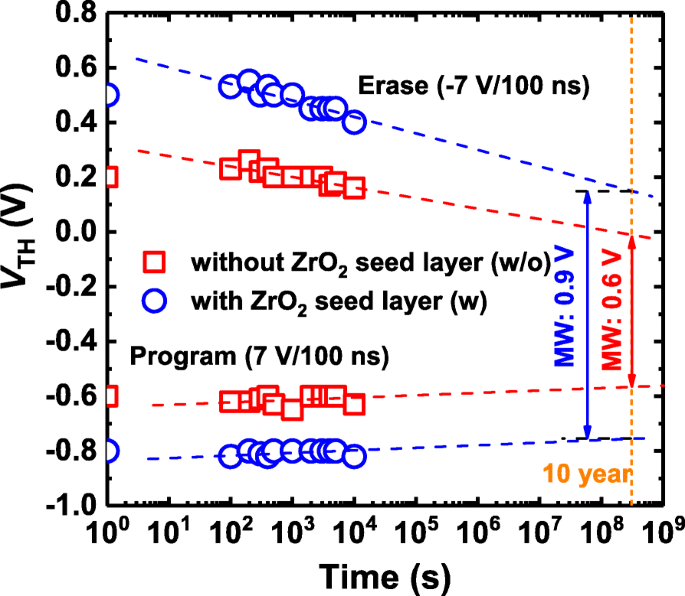

Retention performance was evaluated by measuring V_TH after program and erase pulses at room temperature (Fig. 3). Both devices exhibit a roughly linear V_TH trend versus log(time). Extrapolation to 10 years yields a MW of 0.9 V for the seed‑layer device, compared with 0.6 V for the seed‑free device. The larger CET of the ZrO₂/SiO₂ stack (1.5 nm/2.6 nm) increases the depolarization field, suggesting that further retention gains could be achieved by thinning the SiO₂ layer.

Retention characteristics of HZO FeFETs with and without ZrO₂ seed layers.

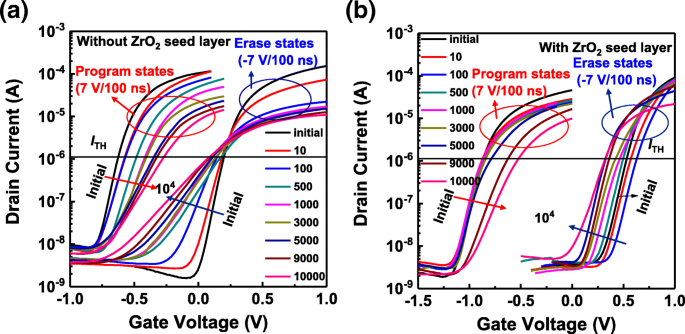

Figure 4 traces the evolution of I_D–V_G curves under ±7 V/100 ns alternating P/E cycles. The seed‑free device shows significant shift and slope degradation from early cycles, with the erased state suffering greater slope loss. In contrast, the seed‑layer device exhibits only a minor positive shift in the erased state—attributable to the wake‑up effect [13,28–32]—and negligible shift in the programmed state up to 1×10³ cycles. Both states also display only slight slope degradation, indicating reduced interface‑trap generation.

Evolution of I_D–V_G curves of HZO FeFETs a without and b with ZrO₂ seed layers under P/E cycling.

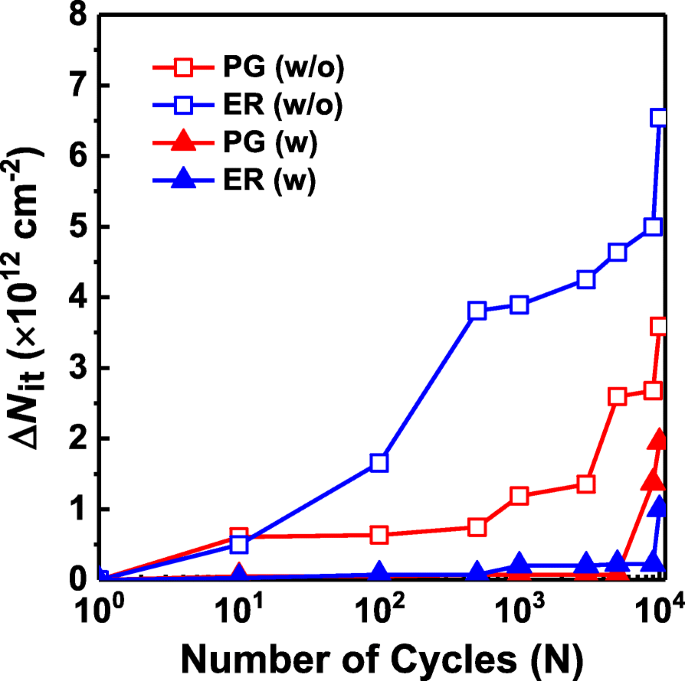

Interface‑trap density (ΔN_it) was derived from the sub‑threshold swing change using ΔSS = (ΔN_it kT ln 10)/(C_FI ϕ_F) [34,35]. As shown in Fig. 5, ΔN_it rises sharply in the seed‑free device from the first few cycles and is markedly higher in the erased state. Conversely, the seed‑layer device shows almost no ΔN_it change up to 1×10³ cycles and consistently lower values than the seed‑free device. The reduced electric field across the gate stack, owing to the high‑k seed layer, diminishes band bending and suppresses interface‑trap generation [12,14].

Evolution of ΔN_it with P/E cycling.

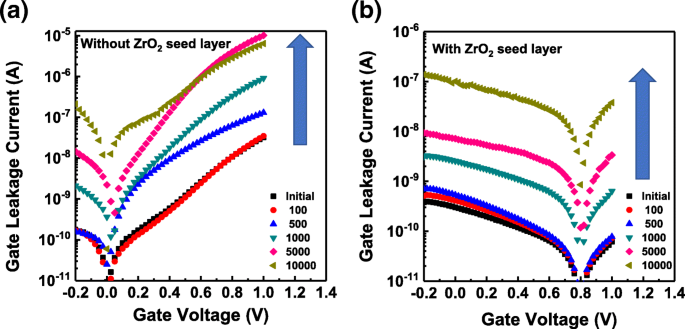

Gate‑leakage currents (I_G–V_G) also reflect the impact of the seed layer (Fig. 6). The seed‑free device experiences a dramatic rise in leakage from the earliest cycles, whereas the seed‑layer device shows negligible change up to 5×10² cycles and maintains lower leakage throughout. Since interface traps can enhance leakage, the suppression of trap generation in the seed‑layer device explains the observed stability.

Evolution of gate‑leakage current characteristics (I_G–V_G) of HZO FeFETs a without and b with ZrO₂ seed layers under P/E cycling.

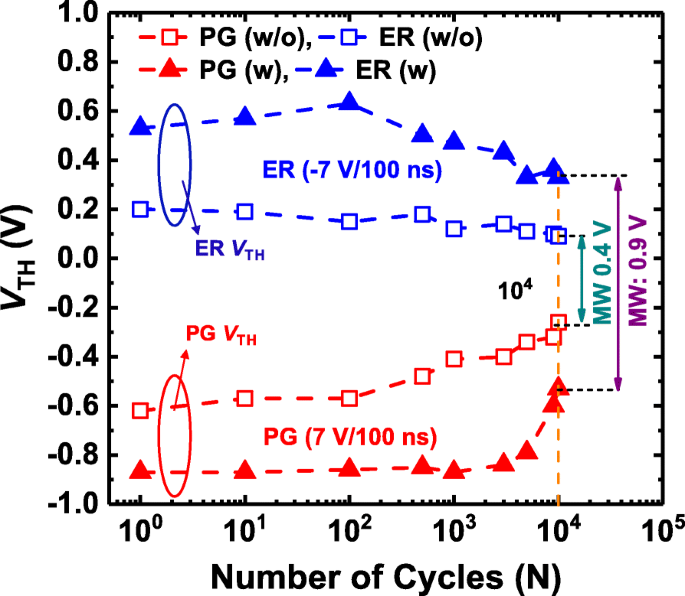

Finally, V_TH values extracted from the I_D–V_G curves over P/E cycles (Fig. 7) reveal that the seed‑layer device consistently maintains a larger MW than the seed‑free device. While the seed‑free MW degrades rapidly, the seed‑layer MW declines only slightly up to 1×10³ cycles and remains above 0.9 V even after 1×10⁴ cycles—approximately 2.3 times the 0.4 V MW of the seed‑free device. The reduced required electric field for achieving saturated polarization states likely underpins this endurance advantage.

Evolution of V_TH with P/E cycling.

Conclusions

Fast‑pulse measurements on HZO FeFETs with TaN/HZO/SiO₂/Si and TaN/HZO/ZrO₂/SiO₂/Si MFIS gate stacks demonstrate that a crystalline ZrO₂ seed layer significantly boosts the memory window and endurance. The seed‑layer device achieves an initial MW of 1.4 V, a 10‑year extrapolated MW of 0.9 V, and sustains a MW above 0.9 V after 10⁴ P/E cycles—substantially outperforming the seed‑free counterpart. The improvements stem from enhanced crystallinity of the HZO layer and reduced interface‑trap generation due to the lowered electric field across the gate stack. These results suggest that integrating a direct crystalline high‑k/Si gate stack will further elevate the MW and reliability of HfO₂‑based FeFETs, paving the way for their adoption in next‑generation memory and logic‑in‑memory technologies.

Availability of Data and Materials

The datasets supporting the conclusions of this article are included within the article.

Abbreviations

- CMOS:

Complementary metal‑oxide‑semiconductor

- FeFET:

Ferroelectric field‑effect transistor

- FeFETs:

Ferroelectric field‑effect transistors

- HKMG:

High‑k metal‑gate

- HZO:

Hf0.5Zr0.5O₂

- ID:

Drain current

- L:

Length

- MFIS:

Metal/ferroelectric/insulator/semiconductor

- MW:

Memory window

- P/E:

Program/erase

- P–V:

Polarization–voltage

- SS:

Subthreshold swing

- VG:

Gate voltage

- VTH:

Threshold voltage

- W:

Width

- ΔNit:

Generated interface traps

Nanomaterials

- Compliance‑Free ZrO₂/ZrO₂₋ₓ/ZrO₂ Tri‑Layer Resistive Memory Enables Controllable Interfacial Multistate Switching

- Enhanced Endurance of HfO₂-Based RRAM via Nitridation Treatment

- Enhancing THz Micro‑Bolometer Performance with Spiral‑Type Antenna‑Coupled Micro‑Bridge Designs

- GeSiSn Thin Films with Nanoislands: Strain‑Driven Morphology, Superstructure Control, and Mid‑IR Photoluminescence

- 2‑nm Source‑Drain FETs: High‑Performance Rectangular Gate U‑Channel Design

- Low‑Temperature ALD Flexible Hf0.5Zr0.5O2 Memristor Exhibiting Short‑ and Long‑Term Synaptic Plasticity

- High‑Stability Voltage Regulator with Transient Enhancement & PSR Boost

- Ultra‑Low‑Voltage 2D MoS2 Ferroelectric Memory Transistor with Hf₁₋ₓZrₓO₂ Gate for CMOS Compatibility

- HDAC1 Regulates miR‑124‑5p and NPY to Modulate Learning and Memory in Depressive Rat Models

- Enhancing Thermoelectric Performance: Silicon Substrates with Highly Doped Porous Si via Metal-Assisted Chemical Etching