Cadence Unveils Rapid-Performance Emulation & Prototyping Solutions for Billion‑Gate SoC Verification

Cadence Design Systems today introduced its latest emulation and prototyping platforms, promising the fastest, highest‑performance pre‑silicon hardware debugging and software validation for billion‑gate SoC designs.

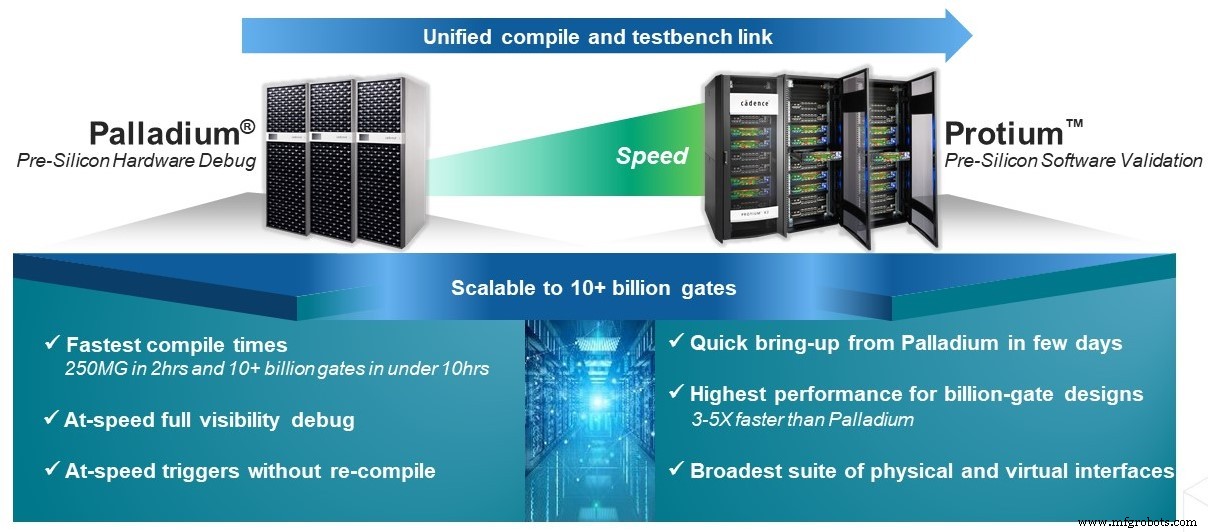

With a unified compiler interface and common debug and testbench interfaces, the new Palladium Z2 enterprise emulation and Protium X2 enterprise prototyping systems deliver twice the capacity and 1.5‑times the performance of their predecessors. The breakthrough modular compile technology can process 10 billion gates in under 10 hours on Palladium Z2 and under 24 hours on Protium X2.

Central to the Palladium Z2 / Protium X2 combination is the unified compiler interface: a design that compiles for Palladium will compile and run on Protium. The seamlessly integrated flow, unified debug, shared virtual and physical interfaces, and common testbench content enable rapid migration from emulation to prototyping. Scalable capacity addresses the demands of mobile, consumer, and hyperscale computing designs.

Cadence’s Paul Cunningham, senior vice president and general manager of the system and verification group, said, 'Pre‑silicon verification of advanced SoC design requires a solution with multi‑billion‑gate capacity that offers both highest performance and rapid, predictable debug. Our new dynamic duo meets these requirements with two tightly integrated systems: Palladium Z2 emulation optimized for rapid, predictable hardware debug and Protium X2 prototyping optimized for highest performance multi‑billion‑gate software validation. We are excited by the strong customer interest and look forward to partnering with them to leverage these new systems to achieve the highest verification throughput on their designs.'

Early customers have highlighted the benefits of the common front‑end verification throughput. At Nvidia, senior director for hardware engineering Narendra Konda said, 'The complexity of our high‑end graphics and hyperscale designs increases with each generation, while our time‑to‑market schedules tighten. Using the common front‑end flow in the Cadence Palladium Z2 and Protium X2 systems, we are optimizing workload distribution between verification, validation and pre‑silicon software bring‑up. With twice the usable capacity, 50 percent higher throughput, and faster modular compiler turnaround, we can validate our most sophisticated GPU and SoC designs comprehensively and on schedule.'

Meanwhile, at Arm, senior director of design services Tran Nguyen said, 'Best‑in‑class emulations are key to our success, and Arm uses emulation extensively together with simulation on Arm‑based servers to achieve the highest verification throughput. With the new Cadence Palladium Z2 system, we have seen up to 50 percent improvement in performance and 2‑times improvement in capacity for our latest designs, providing us with the powerful pre‑silicon capabilities needed to verify our next‑generation IP and products.'

Like their predecessors, Palladium Z2 and Protium X2 are built to a standard rack configuration and are intended to be installed inside a data center and accessed from the engineers’ desk. Both can handle many designs concurrently, depending on how much capacity the individual designs actually require. The granularity that can be shared is at the individual chip inside the system, and both systems scale so that each individual chip can be used in parallel for a different design:

- Palladium Z2 scales from one chip with 8 million gates and can have up to 144 concurrent jobs per rack. Or it can scale to 18.4 billion gates per rack if the whole rack is used for a single design. Beyond that, up to 12 racks can be used for a single design and scale all the way to 18.4 billion gates.

- A full rack of Protium X2 contains 60 FPGAs and we do have customers who run 60 jobs in parallel. Since a single FPGA in Protium X2 holds ~40 million gates, these are not small designs. The whole rack can be used for a single design of 2.4 billion gates. Or, as with Palladium Z2, a large design can be further scaled across several racks.

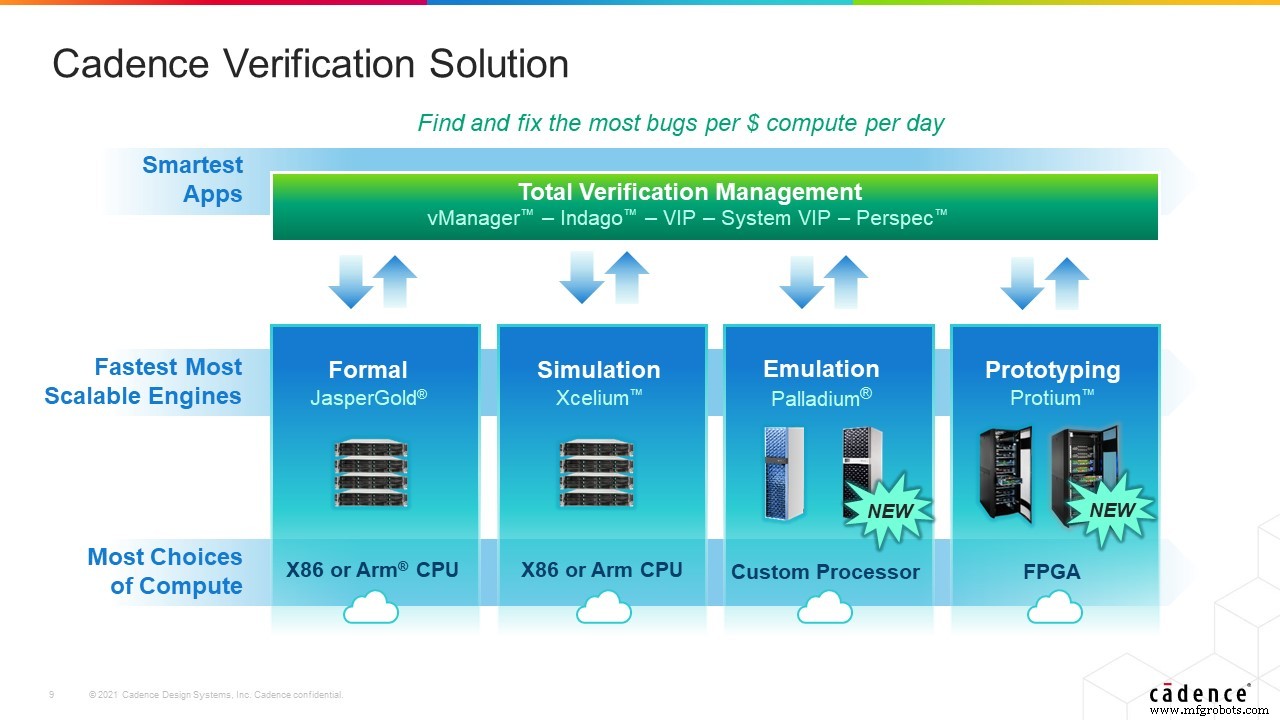

The Cadence verification full flow, including Palladium Z2 emulation, Protium X2 prototyping, Xcelium logic simulation, the JasperGold formal verification platform and the Cadence suite of smart verification applications, delivers the highest verification throughput of bugs per dollar per day, according to the company.

Embedded

- How Embedded Systems Drive Modern Vehicle Innovation

- VE-VIDES Initiative Unveils Trustworthy Design & Verification Framework for IoT Security

- From Bare-Metal to Operating Systems: Why I Shifted My Embedded Development Focus

- Pre‑Silicon Software Development: Accelerating Time‑to‑Market with SoC Emulation

- Strengthening Security in Automotive Systems: Safeguarding the Future of Connected Vehicles

- Automating C Test Generation for Comprehensive Embedded SoC Verification

- Overcoming Challenges in Automotive Camera Link Technologies

- Cadence Unveils Cloud Passport Partner Program to Accelerate Cloud Migration for Chip Design

- Hitachi Acquires Robotics Integrator JR Automation for $1.4B

- ABB Dominates Distributed Control Systems Market with 20% Share, 22-Year Streak