Astera Labs Unveils CXL 2.0 & PCIe 5.0 Solutions to Slash Latency and Power Heterogeneous Compute

Fabless semiconductor startup Astera Labs has announced purpose‑built CXL 2.0 and PCIe 5.0 connectivity solutions designed to unlock heterogeneous compute architectures and address latency‑sensitive workloads in data centers. The new solutions target system‑wide performance bottlenecks in data‑centric applications.

With data growth and specialized workloads such as AI and machine learning, purpose‑built accelerators must operate side‑by‑side with general‑purpose CPUs on the same board or rack while sharing a unified memory space. CXL 2.0 interconnect is essential for creating cache‑coherent topologies.

The first product in the portfolio is the Aries Compute Express Link (CXL 2.0) smart retimer family (PT5161LX, PT5081LX), delivering low‑latency CXL.io connectivity. These devices are currently in sampling with strategic customers. CEO Jitendra Mohan said, “By expanding into the CXL ecosystem, Astera Labs is taking another giant leap to provide purpose‑built solutions that unlock complex heterogeneous compute and composable disaggregation system topologies.”

The CXL 2.0 specification, released by the CXL Consortium in November 2020, extends the open, industry‑standard interconnect with cache coherency and memory semantics. New features include switching for fan‑out to support more devices, memory pooling for higher utilization and on‑demand capacity, and persistent memory support—all while maintaining full backward compatibility with CXL 1.1 and 1.0.

Barry McAuliffe, president of the CXL Consortium, noted, “As an early CXL Consortium member, Astera Labs contributed its connectivity expertise to advance the CXL standard. It is great to see its first CXL silicon implementation come to market in support of a fast‑growing CXL ecosystem.”

New PCIe 5.0 Solutions in Collaboration with Intel

Astera Labs announced a new low‑latency mode in its Aries smart retimer portfolio for PCIe connectivity with Intel Xeon Scalable processors. Developed in partnership with Intel, this mode reduces PCIe link latency to sub‑10 ns and boosts performance in data‑centric workloads. Astera Labs claims to be the first vendor to demonstrate robust PCIe 5.0 interoperability with Intel’s Sapphire Rapids Xeon Scalable platform.

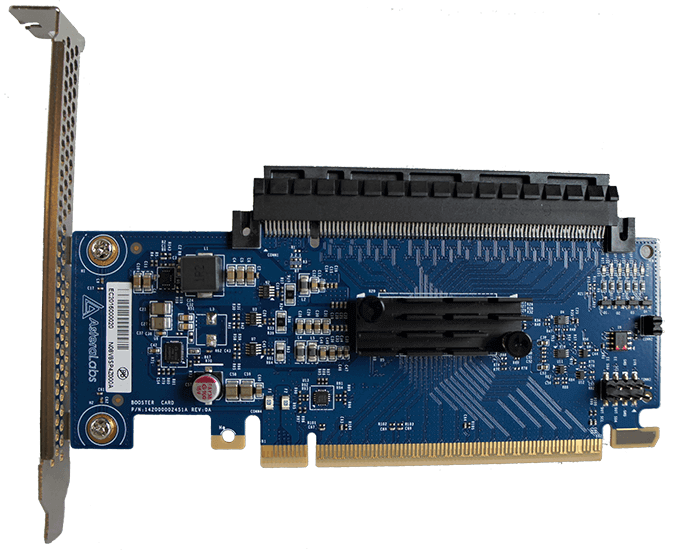

A new plug‑and‑play Smart retimer add‑in‑card, Equinox, was also launched. Developed with Intel, the card and its purpose‑built firmware simplify the creation of PCIe 5.0‑enabled systems using Intel’s latest Xeon Scalable processors, marking Astera Labs’ shift toward user‑friendly, plug‑and‑play boards that accelerate complex system topology deployment.

“PCIe Gen5 and CXL are foundational technologies for heterogeneous compute workloads and data‑center architectures today and tomorrow,” said Zane Ball, Intel corporate VP and general manager for data‑center engineering and architecture. “Intel is collaborating with ecosystem leaders like Astera Labs to significantly reduce PCIe and CXL interconnect latency on upcoming Intel Xeon Scalable platforms, including Sapphire Rapids.”

Related Contents:

- Retiming USB4 over USB‑C

- Building high‑performance interconnects with multiple PCIe generations

- Xilinx targets data center offload with ‘composable’ hardware

- How edge supercomputing will transform the great data deluge

Embedded

- Industrial IoT Communication: 6 Proven Infrastructure Protocols

- DATA MODUL Showcases Cutting‑Edge Digital Signage Solutions at ISE Amsterdam

- Swissbit Showcases Cutting‑Edge Hardware Security for IoT Devices at it‑sa

- Datafication & Edge Autonomy: The Cornerstones of Tomorrow’s Smart Cities and Industries

- AWS IoT Solutions Design Best Practices

- Enable Phone Calls on Arduino UNO Using Twilio & Yaler – Call My Arduino Project

- C64 Retro Controller: Arduino Nano Interface

- Mini Acoustic Levitation Demo with Arduino UNO & HC-SR04 Ultrasonic Sensor

- Enhancing Industrial Performance: Overcoming Monitoring Challenges with IoT & Analytics

- Eliminating Bottlenecks: Harnessing Analytics for Manufacturing Efficiency