Enhanced Retention in TaO/HfO and TaO/AlO RRAM: A Self‑Rectifying Switching Model

Abstract

A comprehensive retention model for self‑rectifying TaO/HfOx and TaO/AlOx resistive random‑access memory (RRAM) is presented. In defect‑trapping RRAM, the low‑resistance state (LRS) typically degrades faster than the high‑resistance state (HRS) due to the limiting influence of the internal TaO resistor layer. Stacking TaO/AlOx in the switching stack markedly improves LRS retention, with extrapolation predicting over 5 years at room temperature. Both structures share a common TaO capping layer and exhibit an identical activation energy of 0.38 eV. The AlOx layer introduces a higher oxygen‑diffusion barrier, substantially enhancing retention and maintaining a stable LRS under biased conditions.

Background

NAND flash technology is approaching its scaling limits, making vertical RRAM (VRRAM) with minimal film stacks, high yield, and no cross‑coupling a promising solution for ultra‑dense memory [1,2,3]. The 1TnR 3‑D architecture enables ultralow bit cost in compact arrays [4,5,6]. Recent work has shifted RRAM operation toward low‑current, defect‑trapping, vacancy‑modulating, or interface‑type switching mechanisms [7,8,9], yet retention failures linked to oxygen‑vacancy migration remain unresolved [3,10]. Filamentary‑type retention studies propose various models to explain losses [11,12,13], suggesting a shift in switching mechanisms could improve endurance. Prior studies of TaO/HfOx devices have shown nonlinearity of ~40, endurance >1000 cycles, and 85 °C data retention [6,7]. Achieving stable retention at low current levels, however, remains a challenge. This letter introduces a retention model based on the Arrhenius method for two defect‑trapping devices, highlighting the role of the AlOx layer in enhancing retention through dense bonding.

Methods

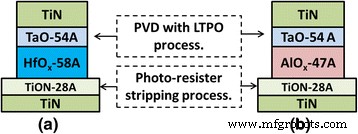

TaO/HfOx and TaO/AlOx devices were fabricated on 8‑in. Si/thermal‑oxide substrates. Bottom electrodes (TiN) were deposited by PVD, patterned, and etched via conventional lithography. Post‑etch cleaning employed O2/H2O plasma at 180 °C, forming a thin TiON oxidation layer on TiN. Switching layers of HfOx and AlOx were deposited by ALD using HfCl4-H2O and TMA-H2O precursors at 300 °C and 250 °C, respectively. A TaO capping layer was then added by low‑temperature plasma oxidation (LTPO) at 0.2 Å/s, providing an internal self‑compliance resistor. Top electrodes (TiN) were deposited by PVD. Figure 1 illustrates the layer stack and thicknesses for both device types. After patterning, a low‑temperature oxide (250 °C) was deposited for passivation, followed by standard back‑end processing for contacts and pads.

Cell schematic with thickness details for a TaO/HfOx and b TaO/AlOx devices. Both stacks use LTPO‑deposited TaO and plasma‑oxidized TiON interfacial layers.

Results and Discussion

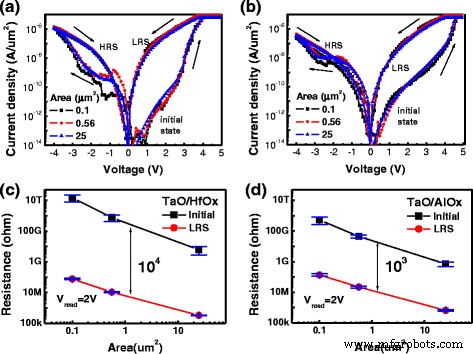

The electrical performance was evaluated with an HP4156C semiconductor parameter analyzer. Figures 2a and 2b show the J–V characteristics for TaO/HfOx and TaO/AlOx cells, respectively, across three device areas (0.1, 0.56, and 25 µm2). All devices started in the HRS, were programmed to LRS with a positive bias, and then reset to HRS with a negative bias. The J–V curves exhibit consistent current density across cell sizes, indicating uniform field‑driven programming and confirming defect‑trapping switching behavior. The LRS and HRS resistances scale inversely with area (Fig. 2c, 2d), reinforcing the current‑density‑controlled switching mechanism. TaO/AlOx devices require slightly higher set (4–4.5 V) and reset (–1.5 to –2.5 V) voltages than TaO/HfOx (3–4 V, –0.5 to –1.5 V), reflecting the higher energy barrier in the AlOx layer.

Current density vs. voltage for a TaO/HfOx and b TaO/AlOx devices; resistance vs. area for c TaO/HfOx and d TaO/AlOx devices (read at 2 V). Each point averages 10 devices with standard deviation.

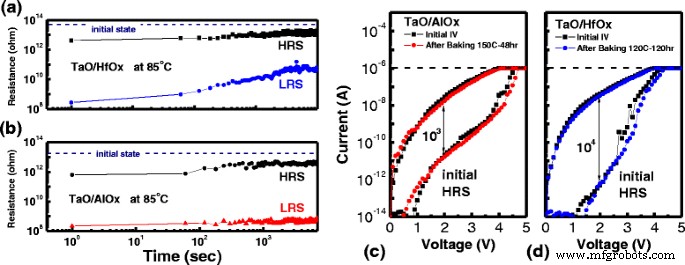

Retention behavior was assessed at 85 °C and 1 V. Figures 3a and 3b reveal that LRS degrades more noticeably than HRS in both device types, yet TaO/AlOx shows superior LRS stability. Over time, both HRS and LRS drift toward the initial resistance state (IRS), as highlighted by dashed lines in the plots. Figure 3c and 3d illustrate that baking TaO/AlOx at 150 °C for 48 h and TaO/HfOx at 120 °C for 120 h restores the LRS to its initial condition, underscoring the role of oxygen‑ion/vacancy recombination in retention loss.

Resistance variation over time for a TaO/HfOx and b TaO/AlOx at 85 °C (1 V). Post‑baking LRS restoration shown in c TaO/AlOx (150 °C/48 h) and d TaO/HfOx (120 °C/120 h).

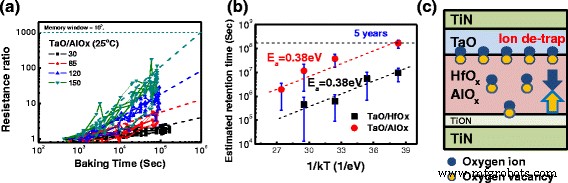

Retention times were extracted using the Arrhenius method. By analyzing the LRS resistance ratio over time (30–150 °C) and extrapolating to 103× the initial LRS, we estimated retention times of 106 s at 150 °C and ~2 × 108 s (≈5 years) at room temperature for TaO/AlOx devices. Both TaO/HfOx and TaO/AlOx share the same activation energy of 0.38 eV, indicating that the TaO capping layer dominates the vacancy‑ion recombination process. The AlOx layer’s higher atomic density and shorter Al–O bond length reduce oxygen‑ion mobility, creating a higher diffusion barrier that extends retention.

a Resistance ratio vs. baking time for various temperatures in TaO/AlOx devices (average initial R = 179 MΩ at 2 V). b Estimated retention time (×103) vs. 1/kT; extracted activation energies are 0.38 eV for both device types. c Schematic of oxygen diffusion barriers in HfOx vs. AlOx with TaO capping.

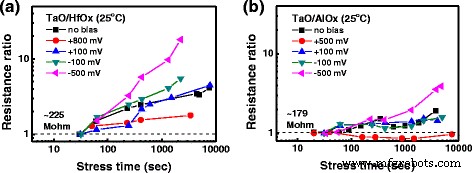

The retention mechanisms differ between filamentary and defect‑trapping RRAM. In filamentary devices, lateral vacancy diffusion governs rupture, whereas defect‑trapping devices exhibit longitudinal diffusion parallel to the electric field, making retention sensitive to bias polarity. Figures 5a and 5b show on‑bias retention: a positive bias prolongs LRS, while a negative bias accelerates degradation. At ±100 mV, on‑bias effects are negligible, likely due to band offsets at TiON–HfOx, TiON–AlOx, and TiN–TaO junctions. A 500 mV positive bias on TaO/AlOx produces no observable degradation.

On‑bias resistance ratio vs. stress time for a TaO/HfOx and b TaO/AlOx devices at room temperature.

Conclusions

Comparative analysis of TaO/HfOx and TaO/AlOx self‑rectifying RRAM reveals that the AlOx switching layer delivers higher switching voltages and markedly improved LRS thermal stability. The enhanced retention arises from a higher oxygen‑diffusion barrier rather than changes in activation energy. The activation energy (0.38 eV) is governed by the TaO resistive layer’s ion de‑trap process, while the dense AlOx film suppresses vacancy diffusion, extending LRS retention. The proposed retention‑loss schematic, supported by on‑bias experiments, offers valuable guidance for designing low‑current, long‑retention, self‑rectifying RRAM for next‑generation high‑density memory.

Nanomaterials

- Circuit With a Switch: A Practical Guide to Basic Electrical Circuits

- Optimized HfO2/TiO2/HfO2 Trilayer RRAM: Electrode-Dependent Bipolar Switching and Enhanced Uniformity via Atomic Layer Deposition

- Optimizing HfO₂/Ge Gate Dielectrics: In Situ SiO₂ Interlayers via PEALD Enhance Interface, Electrical, and Band Alignment

- Optimized Biocompatibility of Anodic Tantalum Oxide Nanotube Arrays

- Enhanced Endurance of HfO₂-Based RRAM via Nitridation Treatment

- Electronic Structure and Transport in InSe Nanoribbons: Edge Effects and Hydrogen Passivation

- Mitigating Random Telegraph Noise in FinFET‑Based RRAM Through Stress Analysis and On‑Chip Annealing

- High‑Stability Voltage Regulator with Transient Enhancement & PSR Boost

- Step-by-Step Guide to Wiring a GFCI Combo Switch and Outlet: Diagrams & Installation Tips

- Professional Wiring Guide for Combo Switch/Outlet Devices – Diagrams & Installation Tips