Mitigating Random Telegraph Noise in FinFET‑Based RRAM Through Stress Analysis and On‑Chip Annealing

Abstract

We report a systematic investigation of random telegraph noise (RTN) observed in the read current of a FinFET‑based dielectric RRAM (FIND RRAM) cell. After repeated cycling stress, the RTN amplitude and frequency increase markedly, compromising data integrity. Our measurements show that high‑temperature annealing suppresses these noise spikes, enabling a practical on‑chip annealing strategy that restores device performance.

Introduction

The relentless scaling of CMOS has delivered impressive gains in speed and density, yet it also magnifies single‑atom variability such as random dopant fluctuations (RDF) and line‑edge roughness (LER) [1–4]. In sub‑20 nm nodes, these variations manifest as unpredictable behavior, notably random telegraph noise (RTN) in ultra‑scaled devices like NAND flash and resistive RAM [5–11]. In this work, we focus on an n‑channel FinFET‑based FIND RRAM cell that has been successfully integrated into 1 kbit arrays [12]. We quantify how cycling stress and temperature influence RTN and demonstrate that a targeted anneal can mitigate the resulting read‑current instability.

Background and Methods

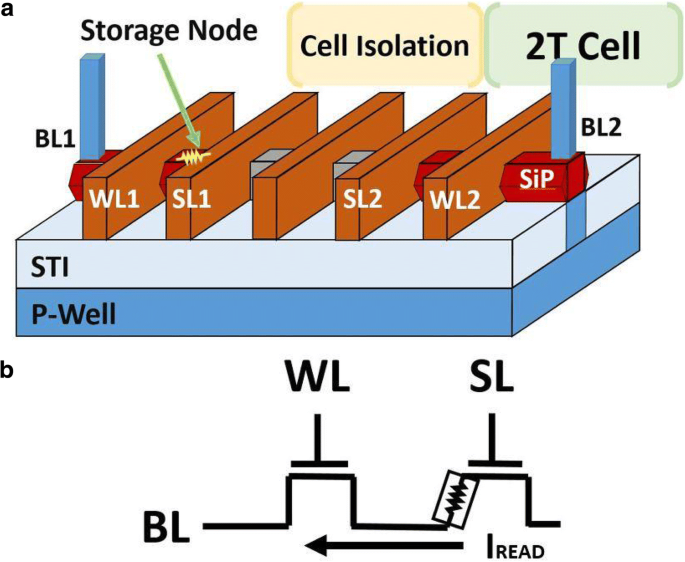

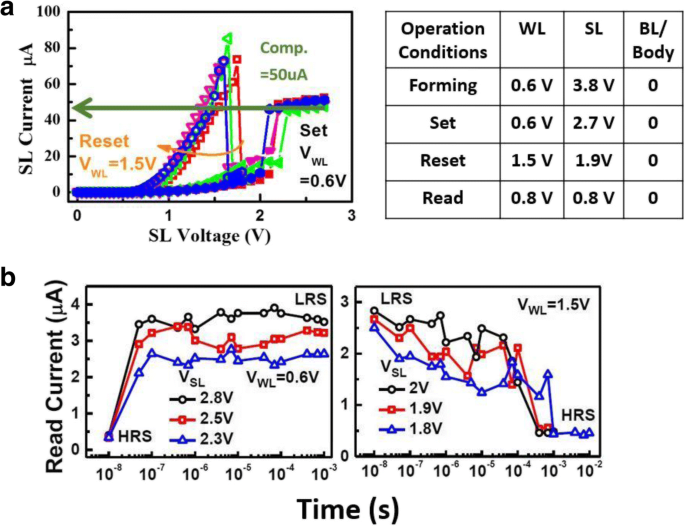

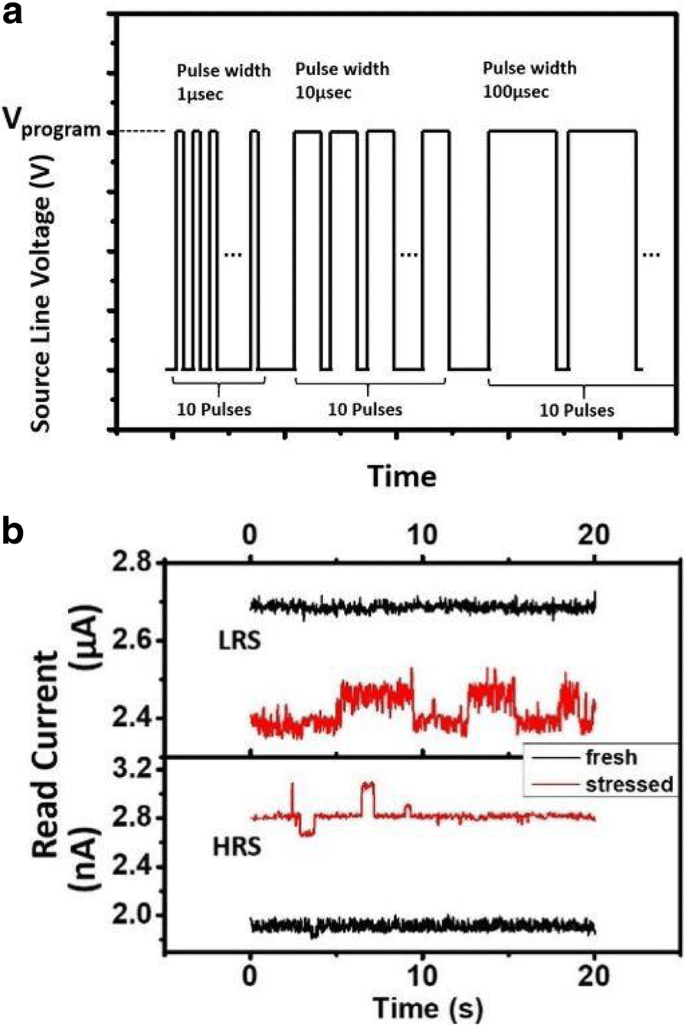

A FIND RRAM device comprises two FinFET transistors: a word‑line (WL) selector and a storage node formed by a high‑k gate dielectric between the source and drain of the second transistor (Fig. 1a). The gate stack consists of HfO₂/SiO₂/TiN, with a tungsten top electrode and TaN bottom electrode [12]. During read, WL and substrate‑line (SL) are biased at 0.8 V to drive a sufficient read current (Fig. 1b). The cell switches between high‑resistance state (HRS) and low‑resistance state (LRS) via set/reset pulses [13]. DC sweeps confirm stable resistive switching, while pulse‑width scaling is required to achieve target read currents of ≥ 3 µA (LRS) and ≤ 1 µA (HRS) (Fig. 3a). RTN manifests as discrete current steps in both states (Fig. 3b), attributed to charge trapping/detrapping along the conduction path [14–17]. Repeated cycling induces stress in the transition‑metal‑oxide (TMO) dielectric, increasing the likelihood of RTN events. We monitored read currents before cycling, after 10 × cycles, and after 100 × cycles to capture stress evolution. Temperature effects were probed by cooling to 0 °C, heating to 50 °C, and sampling read currents continuously for 20 s at 500 Hz. This protocol reveals how trap dynamics shift with temperature.

a 3D illustration of the 2‑T FIND RRAM cells fabricated with CMOS FinFET technology; b read‑condition circuit schematic (VSL = VWL = 0.8 V, BL = 0 V).

The DC resistive‑switching characteristics of the FIND RRAM and its operation conditions (a); time‑to‑set and time‑to‑reset summaries (b).

a Pulse‑width evolution during set/reset; b comparison of read current before and after 100 cycles (VSL = VWL = 0.8 V, VBL = 0, sampling 500 Hz).

Results and Discussion

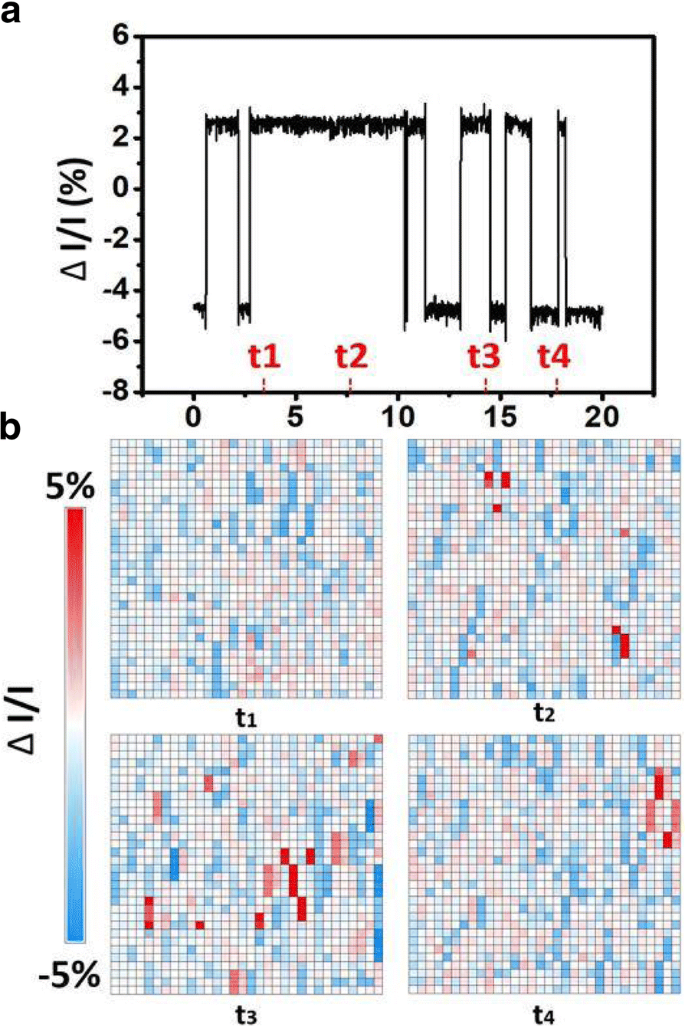

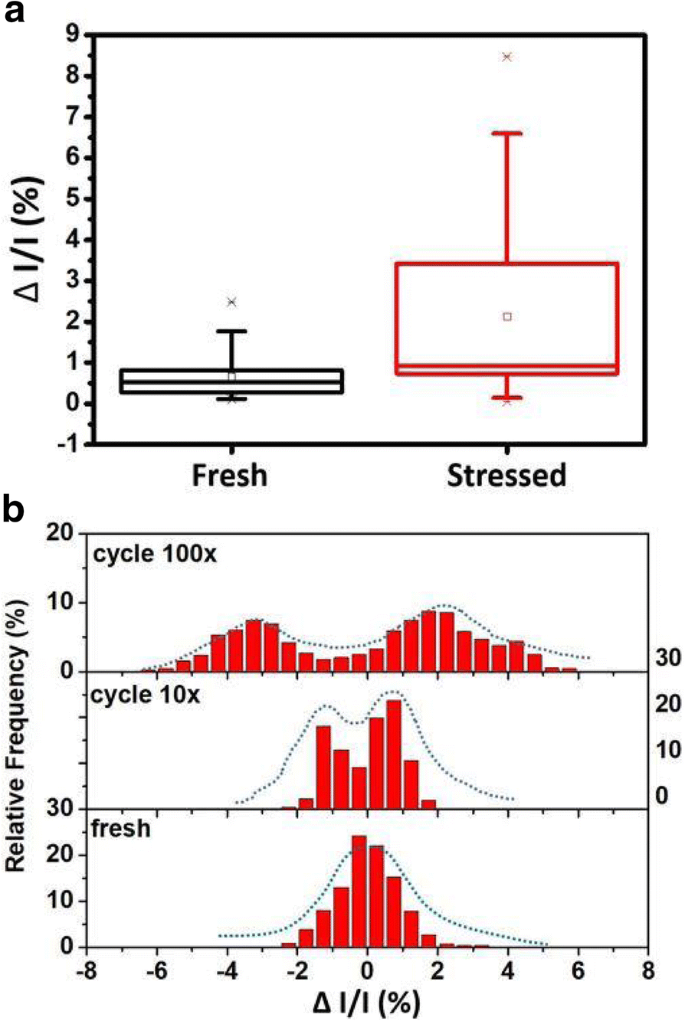

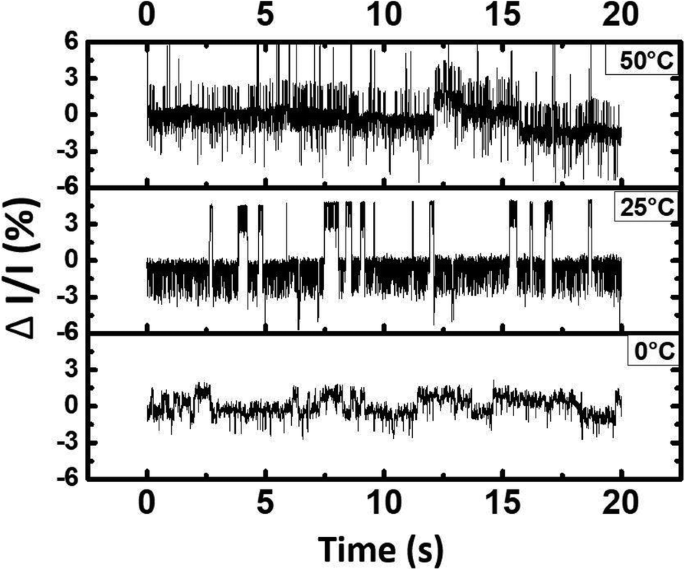

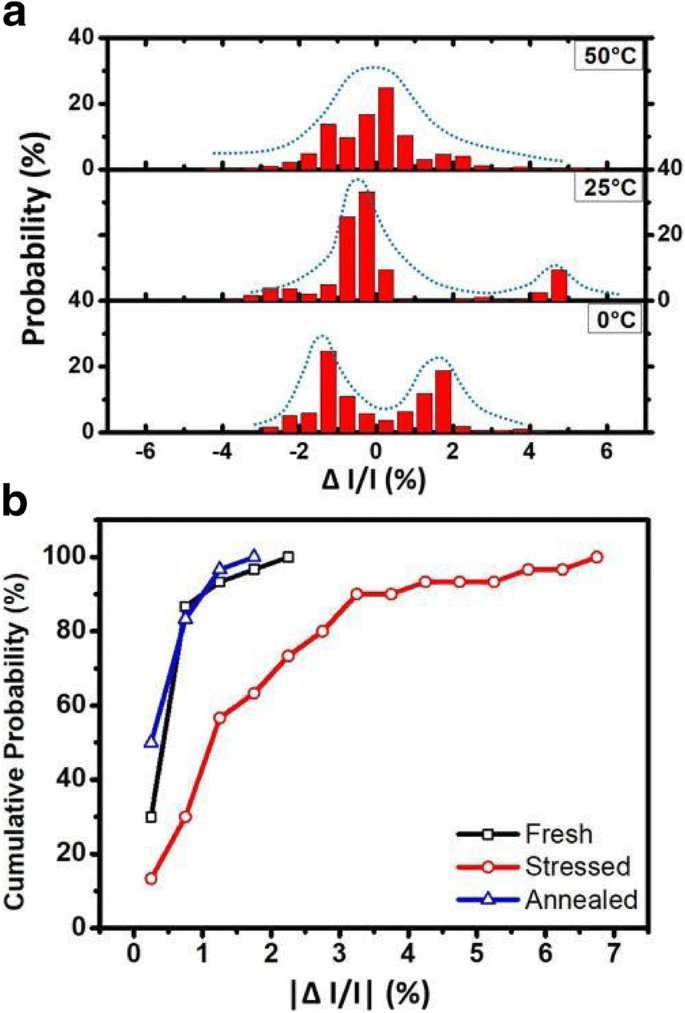

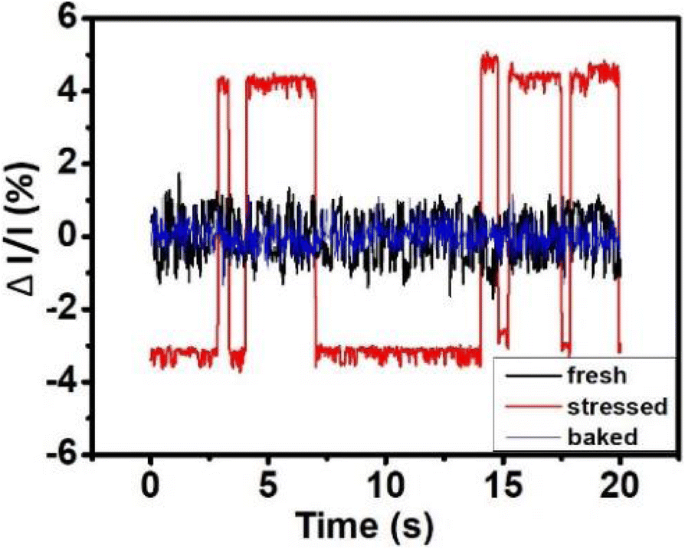

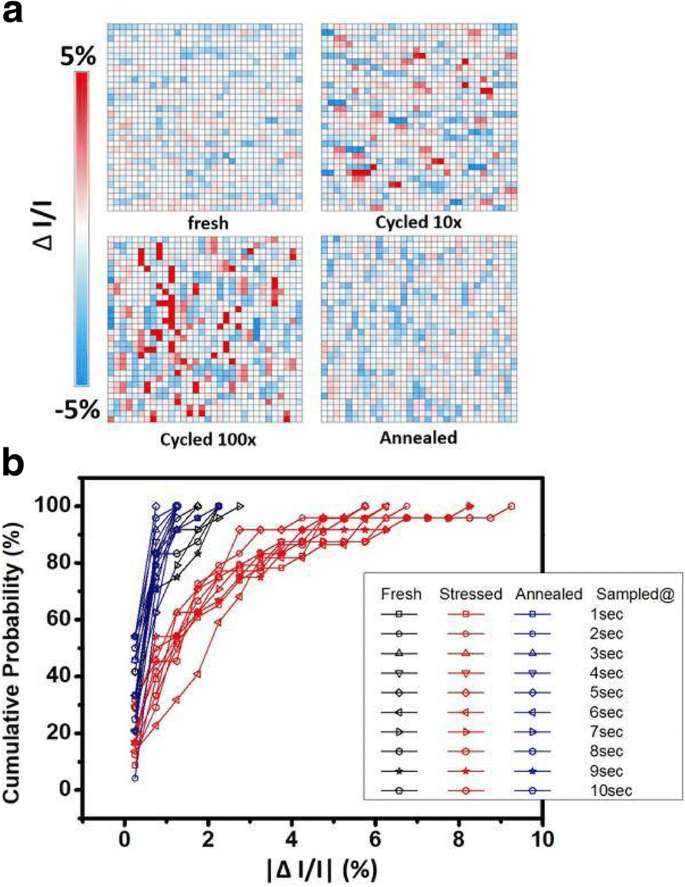

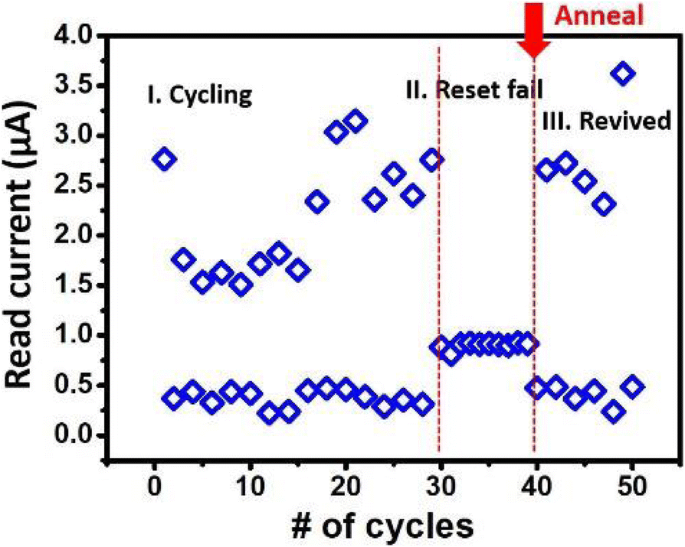

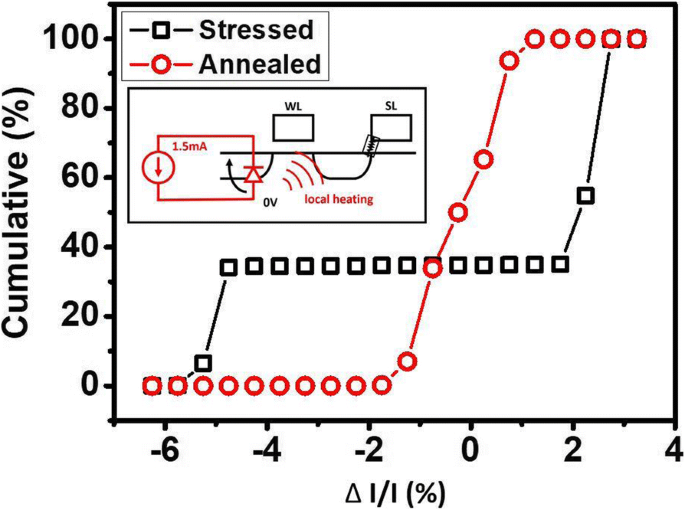

RTN is most pronounced in the LRS, making it the focal point of our analysis. In a 1 kbit array after 10 cycles, RTN drives measurable read‑current fluctuations up to ± 5 % (Fig. 4a). A normalized current map (Fig. 4b) confirms that these deviations are spatially correlated with stressed cells. Across 50 sampled cells, 90 % exhibit increased ΔI/I after cycling, evidencing a cumulative degradation of read stability (Fig. 5a). Fresh cells display a single‑peak current distribution (Fig. 5b), whereas stressed cells show bimodal or multimodal distributions, indicative of trap‑induced current states. Temperature dependence follows established trap kinetics: capture and emission times decrease with rising temperature, increasing RTN frequency. As temperature rises from 0 °C to 25 °C, fluctuations become more frequent (Fig. 6). At 50 °C, however, the two‑state signature diminishes, suggesting thermally activated annealing of traps that reduces RTN amplitude (Fig. 7a). Cumulative distributions of ΔI/I before stress, after stress, and post‑annealing reveal that a large fraction of cells recover to near‑original noise levels after high‑temperature bake (Fig. 7b). Further heating to 75 °C followed by 30‑minute cooldown also restores cell performance, as demonstrated in Fig. 8. The high‑temperature bake effectively re‑establishes the conductive filament by redistributing oxygen vacancies, thereby mitigating RTN and preventing mid‑state stalling. We translate this bulk anneal into an on‑chip approach: a 1.5 mA forward‑bias current applied for 10 s locally heats the TMO region (Fig. 11a). Post‑anneal measurements show a dramatic reduction in RTN, with cumulative probability curves aligning closely with fresh‑state behavior (Fig. 11b). This on‑chip annealing method offers a scalable path to extend FIND RRAM lifetime without off‑chip thermal cycles.

a Normalized read current at 25 °C (500 Hz) for a cell after 10 cycles, showing RTN‑induced time‑variance; b snapshot comparison of a 1 kbit array at 25 °C (t = 3 s, 7.5 s, 14 s, 17.5 s).

a Box‑plot of |ΔI/I| for 50 cells before and after cycling; b histogram of normalized read current distributions pre‑ and post‑stress.

Normalized read currents of a single LRS cell after 100 cycles measured at 0 °C, 25 °C, and 50 °C (500 Hz).

a Histograms of normalized read currents at 0 °C, 25 °C, and 50 °C; b cumulative |ΔI/I| distributions before stress, after stress, and post‑annealing.

Read currents of fresh and stressed cells at 25 °C (500 Hz) compared with the post‑bake state, showing recovery to fresh‑state levels.

a Normalized read currents of a 1 kbit array at fresh, lightly stressed, highly stressed, and post‑annealed states; b cumulative |ΔI/I| probabilities across time for 50 cells.

Application of 125 °C bake restores a cell that was stuck in a mid‑state, extending its functional lifetime.

The on‑chip annealing scheme: applying −1 V at BL with a 1.5 mA forward‑bias current. Cumulative current distributions before and after the process show a pronounced reduction in RTN‑induced fluctuation.

Conclusion

Our study confirms that cycling stress amplifies RTN in FIND RRAM arrays, degrading read‑current stability. High‑temperature annealing—whether bulk or localized on‑chip—effectively neutralizes the underlying traps, restoring performance to near‑fresh levels. This approach offers a viable pathway to prolong the operational life of FinFET‑based resistive memories in scaled CMOS technologies.

Abbreviations

- FIND RRAM

- Fin field‑effect transistor dielectric resistive random access memory

- HRS

- High resistance state

- LER

- Line‑edge roughness

- LRS

- Low resistance state

- RTN

- Random telegraph noise

- TMO

- Transition metal oxide

Nanomaterials

- Build a Remote Temperature Sensor with Raspberry Pi and Python – Step‑by‑Step Guide

- Build a Multi‑Sensor Temperature & Light Monitoring System with Raspberry Pi & DS18B20

- Optimizing Annealing for Amorphous Polymers: Practical Guidelines and Insights

- Impact of Post‑Irradiation Annealing on Microstructural Evolution and Hardening of Helium‑Hydrogen‑Implanted V‑4Cr‑4Ti Alloys

- Cost‑Effective, Tunable Visible Absorbers via Simple Evaporation and Thermal Annealing

- Raman Analysis of G and D′ Phonon Shifts in Vacancy-Engineered Monolayer to Few-Layer Graphene Across 78–318 K

- Verilog Arrays and Memories: Mastering Multi-Dimensional Data Structures

- Arduino Weather Clock – Real-Time Date, Time, Temperature & Humidity Display

- NASA Goddard’s Lab‑On‑Chip Sensor Delivers Real‑Time Flow & Temperature Monitoring

- Stress Relief & Annealing: Essential Heat Treatments for Metal Performance