A Fully CMOS‑Compatible 4T2R nv‑SRAM Using STI‑RRAM with Self‑Inhibit Load – Zero Static Power and High Speed

Abstract

We present a novel 4‑transistor/2‑resistor (4T2R) non‑volatile SRAM (nv‑SRAM) that integrates STI‑based resistive random‑access memory (RRAM) directly within a standard CMOS logic process. The cell employs a self‑inhibit load mechanism that enables data to be stored non‑volatilely while maintaining the fast read/write characteristics of conventional SRAM. Because the RRAM resides in the STI region adjacent to the floating nodes, the design preserves full logic compatibility and incurs no additional process layers, achieving zero static power during data retention.

Background

As CMOS scaling enters the nanometer regime, leakage currents in standard SRAM cells rise sharply, driving static power consumption to unacceptable levels for portable and IoT devices. Researchers have explored a variety of cell topologies and biasing schemes to mitigate this issue, often incorporating non‑volatile storage elements such as RRAM or MRAM to eliminate hold power while preserving speed. However, integrating these NVMs typically requires additional BEOL layers or specialized process steps, which add complexity and increase parasitic capacitance that slows the access time. In our earlier work, we introduced a zero‑static‑power 4T nv‑SRAM that uses STI‑RRAMs adjacent to the floating nodes. This paper expands on that concept by presenting a fully logic‑compatible 4T2R nv‑SRAM that delivers both zero‑holding power and high‑speed operation while remaining fully implementable in a 40 nm CMOS logic flow.

Methods

STI‑RRAM Cell Structure

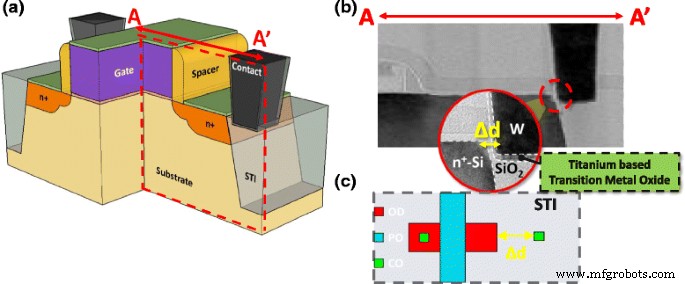

The 3‑D STI‑RRAM design (Fig. 1a) places a transition‑metal‑oxide (TMO) film between an N+ source and a tungsten plug. By carefully positioning the contact in the STI with a defined spacing Δd from the N+ diffusion, the TMO thickness – and thus the device resistance – is precisely controlled. TEM images (Fig. 1b) and layout schematics (Fig. 1c) confirm that the resulting RRAM forms a high‑resistance (≈10⁸ Ω) initial state. Experimental data (Fig. 2a) show a clear correlation between Δd and the initial resistance; a Δd of 10 nm yields the lowest forming voltage and a favorable distribution of both low‑resistance state (LRS) and high‑resistance state (HRS) (Fig. 2b). During set/forming, the select transistor limits the current, which improves endurance (Fig. 4b).

a 3‑D illustration of a 1T1R cell with STI‑RRAM adjacent to the n+ junction.

b TEM cross‑section showing the TMO film between the N+ region and tungsten plug.

c Layout view.

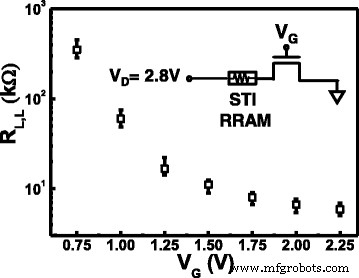

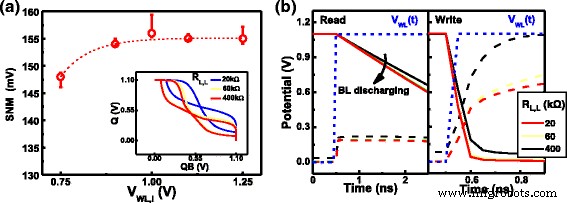

Gate voltage (V_G) controls the LRS read current (Fig. 3), allowing precise tuning of the load resistance. The R_L,L values can be set by adjusting the word‑line (WL) voltage during forming; a WL range of 0.75–1.25 V produces R_L,L between 20 and 400 kΩ (Fig. 3). Lower R_L,L increases standby current (Fig. 7) but also enlarges the resistive window between states.

a Correlation between load resistance R_L,L and applied gate voltage during set.

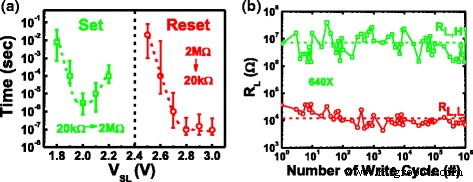

Set and reset times are optimized at V_SL=2 V and 2.8 V, respectively (Fig. 4a). With an incremental step pulse programming algorithm, the RRAM endures 10⁶ cycles with a stable read window (Fig. 4b).

a Time‑to‑set and time‑to‑reset versus pulse amplitude (V_PP).

b Endurance test over 1 M cycles.

Non‑volatile SRAM Concept

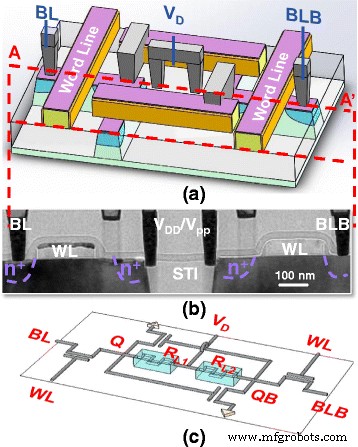

The 4T2R nv‑SRAM (Fig. 5) embeds two STI‑RRAMs as both non‑volatile storage nodes and load resistors. They are positioned between the Q and QB N+ regions and the STI contacts, yielding a compact layout that keeps the RRAM at the same level as the transistors. The resulting cross‑section (Fig. 5b) demonstrates seamless integration without additional BEOL metal layers.

a 3‑D illustration of the proposed 4T2R nv‑SRAM cell.

b Cross‑section TEM of the STI‑RRAM pair.

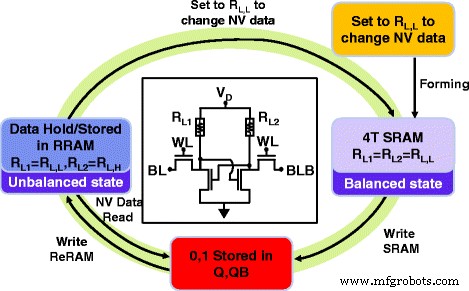

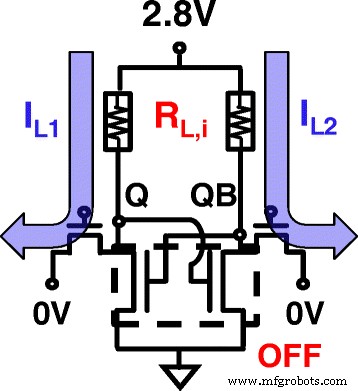

The cell supports both volatile and non‑volatile modes. In the balanced state, the two load resistors are equal (R_L1 = R_L2 = R_L,L), and the cell behaves as a conventional 4T SRAM. To commit data non‑volatilely, a self‑inhibit mechanism resets one RRAM side based on the stored latch value (Fig. 6). After reset, the supply can be turned off, achieving zero hold power. Re‑applying V_DD restores the latch state from the RRAMs, and a blanket set pulse can refresh the memory if needed.

Operational flowchart illustrating volatile and non‑volatile modes.

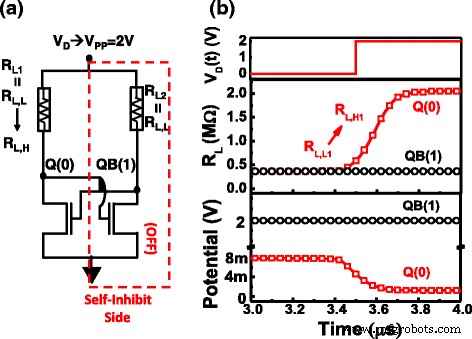

During initialization, a blanket forming pulse (V_D = 2.8 V) sets both R_L1 and R_L2 to the same R_L,L (20–370 kΩ) by controlling the WL voltage. The cell then reaches a balanced state ready for conventional SRAM operation. The self‑inhibit write (Fig. 9) uses a 300 ns, 2 V pulse to selectively reset one RRAM, storing the latch data non‑volatilely while keeping the other RRAM in the opposite resistance state.

a Self‑inhibit write: only one RRAM resets during a V_PP pulse.

b Dynamic response confirming selective reset.

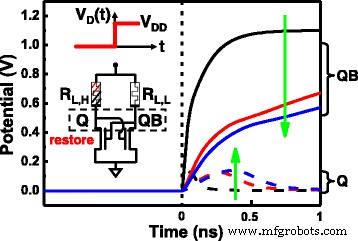

Restoration of volatile data after power‑off is achieved by re‑applying V_DD; the unbalanced RRAMs automatically feed the latch nodes (Fig. 11). The restoration occurs in a few nanoseconds.

Non‑volatile data recovery into Q and QB nodes after power return.

Results and Discussion

Electrical Analysis

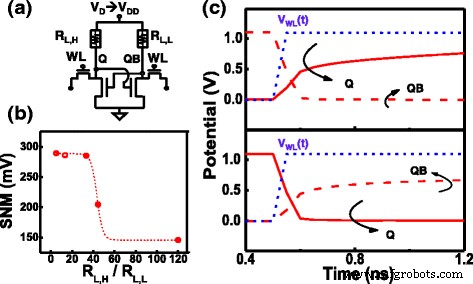

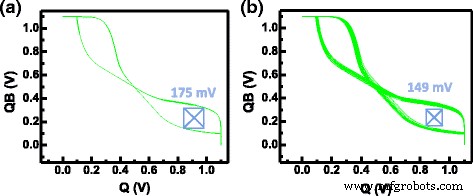

The transition conditions between operational states are listed in Table 1. By varying the WL voltage during initialization, R_L,L can be tuned across 20–400 kΩ. Lower R_L,L values increase standby current (Fig. 7) but also broaden the resistive window, enhancing the dynamic read/write margins. Static noise margin (SNM) measurements (Fig. 8a) show that balanced cells maintain SNM across the entire R_L,L range, with reasonable read margins achieved at WL voltages below V_DD. Dynamic read/write traces (Fig. 8b) confirm sub‑nanosecond access times; higher R_L,L slightly slows the pull‑up but remains acceptable.

a Read SNM versus WL voltage; b Dynamic read/write performance.

Non‑volatile write is accomplished by a 300 ns, 2 V V_PP pulse. Figure 9b demonstrates that selective reset occurs cleanly on one side of the RRAM pair, while the other side remains unchanged. Even with an initial unbalanced load ratio of 2 MΩ/400 kΩ, the cell can write both logic states successfully (Fig. 10c). Upon power‑on, the latch nodes recover automatically (Fig. 11). These results confirm the viability of the self‑inhibit mechanism.

a Unbalanced load scenario.

b SNM under various WL voltages.

c Dynamic write on 400 kΩ load.

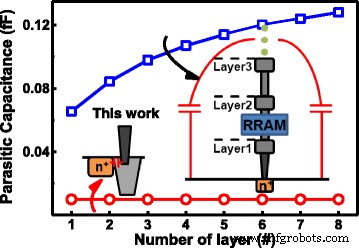

Parasitic Effect and Comparison

Because the STI‑RRAMs reside within the same diffusion layer as the SRAM transistors, the design avoids additional BEOL metal stacks, resulting in negligible parasitic capacitance on the latch nodes. Post‑layout simulations (Fig. 12) confirm that parasitic capacitance remains low even as the number of metal layers increases, in contrast to back‑end‑of‑line RRAM or MRAM implementations. Consequently, the 4T2R nv‑SRAM achieves faster dynamic read times and reduced power consumption compared to prior works [29–31]. Table 2 summarizes key metrics, highlighting the trade‑offs between state‑switching voltage and parasitic overhead.

Parasitic capacitance on latch nodes versus metal layer count.

Variation‑Induced Static Noise Margin Degradation

Process variations in RRAM resistance and transistor threshold voltage (V_T) affect the SNM. Monte‑Carlo simulations (Fig. 14) show that variations in both R_L,L and V_T narrow the SNM distribution. The self‑inhibit mechanism mitigates some of this sensitivity, but further work on process tuning is required to maintain robust margins in deep‑scaled nodes.

V_T variation impacts initialization compliance currents.

Monte‑Carlo butterfly curves showing SNM degradation.

Conclusions

We have demonstrated a 4T2R nv‑SRAM that integrates STI‑RRAMs into a 40 nm CMOS logic process without additional masks or steps. The cell offers self‑inhibit and self‑restore functionality, zero static power during retention, minimal parasitic capacitance, and high‑speed operation. These attributes make the STI‑RRAM‑based nv‑SRAM an attractive solution for low‑power, high‑density non‑volatile logic memory in future systems.

Nanomaterials

- Integrated Circuits: Fundamentals of Digital Logic Gates

- Understanding Power in Resistive and Reactive AC Circuits

- Optimized HfO2/TiO2/HfO2 Trilayer RRAM: Electrode-Dependent Bipolar Switching and Enhanced Uniformity via Atomic Layer Deposition

- Compliance‑Free ZrO₂/ZrO₂₋ₓ/ZrO₂ Tri‑Layer Resistive Memory Enables Controllable Interfacial Multistate Switching

- Engineering Angle‑Dependent Structural Color Patterns with Aligned ZnO Nanofibers

- High-Performance, Low-Voltage HfAlOx RRAM via Atomic Layer Deposition for In-Memory Computing

- Resistive Random‑Access Memory (RRAM): Materials, Switching, Performance, MLC Storage, Modeling, and Real‑World Applications

- High-Performance Multilevel Resistive Switching Memory Using KCl-Enhanced MAPIC Films on ITO Glass

- Enhanced Broadband THz Absorption in Microbolometer Arrays via Integrated Split‑Ring Resonators

- Latch‑Up‑Resistant LVTSCR with Integrated PMOSFET for Enhanced ESD Protection in 28‑nm CMOS