Cu-Catalyzed Growth of Amorphous Silicon Nanowires on SiO₂ by Annealing: A Simple, Contamination‑Free Method

Abstract

We demonstrate a straightforward, catalyst‑free synthesis of amorphous silicon nanowires (α‑SiNWs) directly on 300‑nm SiO₂/Si(100) substrates. Micron‑scale Cu patterns, deposited by sputtering and patterned through photolithography, act as solid‑liquid‑solid (SLS) catalysts during annealing at 1080 °C for 30 min in an Ar/H₂ atmosphere. The Cu patterns form Cu silicide upon reacting with SiO₂, creating a diffusion channel that supplies Si atoms for nanowire growth. Wire length scales linearly with annealing time (up to 24 µm after 30 min), while diameter decreases from 81 nm to 57 nm, yielding a resistivity of 2.15 × 10³ Ω·cm at room temperature. This low‑temperature, toxic‑gas‑free process offers precise control over nanowire density, position, and dimensions, paving the way for CMOS‑compatible device integration.

Background

Silicon nanowires (SiNWs) are pivotal in electronics, photovoltaics, photonics, batteries, and sensing technologies. Traditional top‑down methods—reactive ion etching, metal‑catalyzed electroless etching, and MEMS patterning—provide excellent site control but involve expensive lithography or complex steps. Bottom‑up chemical vapor deposition (CVD) with Au or other metal catalysts delivers high‑quality, ultra‑thin SiNWs but introduces contamination incompatible with CMOS processing. Recent catalyst‑free approaches, such as oxide‑assisted growth or laser ablation, lack integration compatibility or require hazardous materials. Copper, widely used in ICs for its thermal and electrical properties, presents an attractive, CMOS‑compatible catalyst that can be integrated without introducing deep‑level impurities. In this study, we exploit Cu‑mediated SLS growth on SiO₂ to synthesize α‑SiNWs, avoiding toxic precursors and maintaining device‑grade cleanliness.

Methods

Chip Fabrication

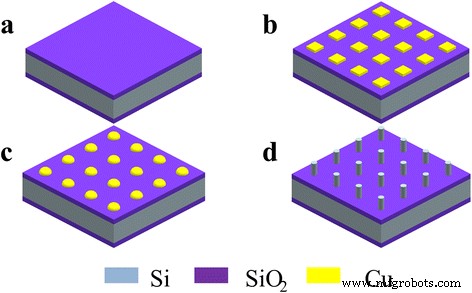

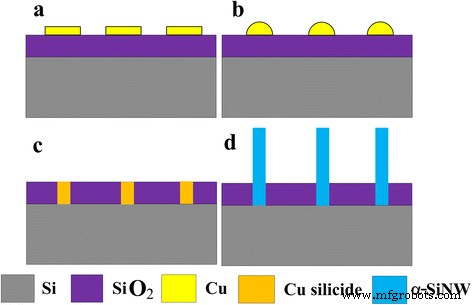

300‑nm SiO₂ was thermally grown on n‑type Si(100) wafers (Fig. 1a). A 400‑nm Cu film was sputtered and patterned into 1.9 µm diameter, 400‑nm thick micron‑scale arrays by standard photolithography and ammonium persulfate etching (Fig. 1b). Chips were diced, cleaned sequentially in ethanol, acetone, and deionized water, then blow‑dried with N₂.

Schematic of the fabrication process. a Thermal oxidation. b Cu pattern array. c Cu hemispheres. d Nanowire growth.

α‑SiNW Growth

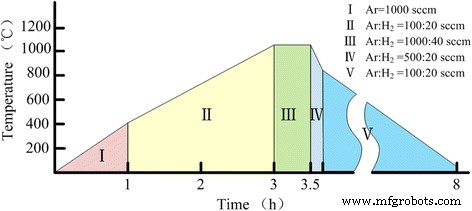

After loading chips onto a quartz boat, the furnace was purged with 1000 sccm Ar for 10 min. Five temperature stages were applied (Fig. 2): (I) ramp to 400 °C in 1 h (Ar only); (II) ramp to 1080 °C in 2 h (100 sccm Ar + 20 sccm H₂); (III) hold 30 min at 1080 °C (1000 sccm Ar + 40 sccm H₂); (IV) rapid cool (10 min, 500 sccm Ar + 20 sccm H₂); (V) slow cool to RT (100 sccm Ar + 20 sccm H₂). Cu patterns dewet and form Cu silicide, providing a diffusion channel for Si atoms that precipitate into α‑SiNWs at the pattern sites.

Thermal processing diagram. See text for stage details.

Characterization

SEM (Hitachi S‑4800) and HR‑TEM (JEM‑2100F, 200 kV) with EDS assessed morphology and composition. TEM samples were mounted on Mo grids; FIB‑etched roots were protected with a thin Au layer. Two‑terminal resistivity measurements employed a Cascade HP 4156 probe station on Pt‑welded devices fabricated via FIB.

Results and Discussion

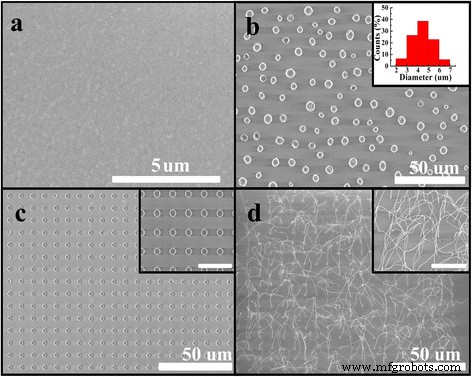

SEM images before and after annealing (Fig. 3) reveal stark differences: a continuous Cu film (sample I) forms random Cu balls (~4.4 µm) after annealing, while a Cu pattern array (sample II) yields single α‑SiNWs (~57 nm diameter, 20 µm length) per pattern, directly reflecting the pattern pitch (10 µm). This confirms that micron‑scale Cu patterns are essential for controlled nanowire nucleation and density.

SEM before/after 30‑min annealing. a Cu film pre‑anneal. b Cu film post‑anneal (Cu ball size distribution). c Cu pattern array pre‑anneal. d Nanowire growth post‑anneal.

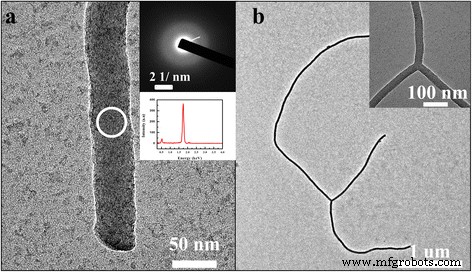

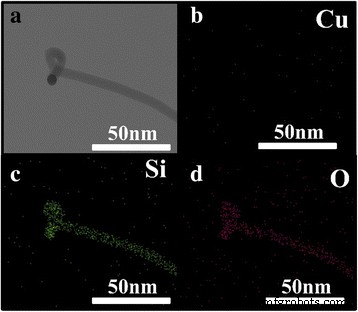

HR‑TEM (Fig. 4) confirms the wires are fully amorphous; SAED shows a diffuse ring pattern, while EDS reveals a Si:O ratio of ~4, indicating minimal oxidation. The wires were grown in an Ar/H₂ atmosphere, so any surface oxidation is due to post‑growth air exposure.

HR‑TEM of α‑SiNW. a Nanowire tip. b SAED pattern. c EDS spectrum.

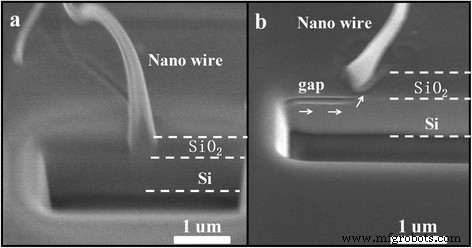

Cross‑sectional SEM (Fig. 5) shows the wires originate at the Si/SiO₂ interface, with a pronounced Si gap indicating that Si diffusion from the substrate, not Cu, supplies the growth material. No metal particle is observed at the wire tip, supporting a SLS mechanism where Cu silicide dissolves Si and re‑precipitates as a wire.

Cross‑section SEM of α‑SiNW root at 45°. A Si gap appears at the Si/SiO₂ interface.

The growth pathway is illustrated in Fig. 6: Cu dewetting, silicide formation, Si diffusion, and precipitation into α‑SiNWs. Cu’s rapid diffusion into Si at high temperature explains the absence of Cu in the final wire.

Schematic of Cu‑mediated SLS growth.

Mapping (Fig. 7) confirms the absence of Cu at the wire tip or root, supporting the diffusion‑driven growth mechanism.

TEM/EDS mapping of wire tip. No Cu detected.

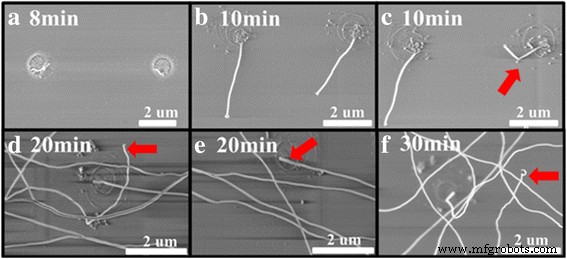

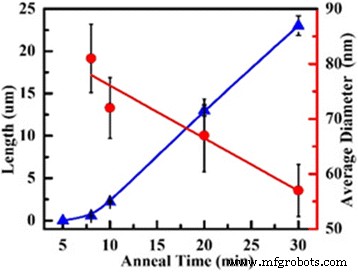

Annealing‑time studies (Fig. 8) show uniform diameters but a slight taper: root diameters (~49 nm) are smaller than tips (~76 nm), implying diameter shrinkage during growth. The average diameter decreases from 81 nm to 57 nm as annealing time extends to 30 min.

SEM images of α‑SiNWs at different annealing times.

Length versus annealing time (Fig. 9) yields a growth rate of ~1.1 µm min⁻¹, comparable to VLS‑grown SiNWs. The rapid deposition prevents crystalline ordering, resulting in amorphous wires. Diameter reduction with time reflects decreasing Cu silicide volume as Cu diffuses deeper into Si.

Length and diameter versus annealing time.

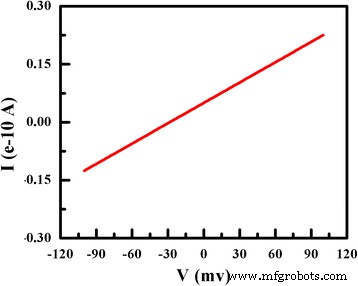

Electrical measurements (Fig. 10) reveal near‑ohmic I‑V behavior. The measured resistivity (2.15 × 10³ Ω·cm) is an order of magnitude higher than doped single‑crystal Si wires, consistent with the amorphous structure and size‑dependent conduction.

Electrical transport of α‑SiNW. Resistivity measured by two‑probe method.

Conclusions

We have established a simple, scalable route to grow Cu‑catalyzed α‑SiNWs on SiO₂ by annealing in an Ar/H₂ atmosphere, avoiding toxic precursors and minimizing metal contamination. Cu patterning dictates wire density and location; annealing time tunes diameter (57–81 nm) and length (up to 24 µm). The wires exhibit a room‑temperature resistivity of 2.15 × 10³ Ω·cm, confirming their potential for future CMOS‑compatible nanodevices.

Nanomaterials

- Optimized Anti‑Solvent Process Yields Fully Covered, Stable FASnI₃ and CsSnI₃ Perovskite Films for Lead‑Free Solar Cells

- Electroless HF/AgNO3 Etching of n‑Si(100) Wafers: High‑Density Silicon Nanowire Arrays with Low Reflectance and Ohmic Conductance

- Large-Area WS₂ Film with Giant Single Domains Grown by Atmospheric‑Pressure CVD

- Rapid Thermal Annealing Enables Uniform In₂Se₃ Nanowire Growth at Low Temperatures

- UV-Enhanced Copper Oxide Nanowire Sensor for Rapid Hydrogen Detection at Room Temperature

- Laser‑Assisted Fabrication of Superhydrophobic PTFE SERS Substrates: A Low‑Cost, Ultra‑Sensitive Platform

- Optimizing Deposition Pressure in PECVD for Low‑Defect Nanocrystalline Si:H Thin Films

- Cost‑Effective, Tunable Visible Absorbers via Simple Evaporation and Thermal Annealing

- Comparative Study of Inkjet‑Printed and Spin‑Coated ZrO₂ Dielectrics for High‑Performance IGZO Thin‑Film Transistors

- Graphene Paper Substrates Deliver Ultra-Lightweight, High Power-Density Silicon Solar Cells