High‑Mobility Germanium p‑MOSFETs with Amorphous Silicon Passivation: Surface‑Orientation Effects

Abstract

We demonstrate that amorphous silicon (a‑Si) passivation, deposited by magnetron sputtering at room temperature, yields germanium (Ge) p‑MOSFETs with record‑high effective hole mobility on (001)‑oriented substrates. With a 0.9‑nm a‑Si cap, the (001) devices deliver a peak μeff of 278 cm²/V·s—almost three times the Si universal mobility—while maintaining low subthreshold swing and leakage. Devices on (011) and (111) orientations show lower mobility and higher interface‑state density, underscoring the importance of crystal orientation in Ge‑MOSFET design.

Background

Germanium offers a higher hole mobility and a lower thermal budget than silicon, making it attractive for next‑generation CMOS and thin‑film transistors [1–6]. Achieving this potential requires an interface with minimal defect density. Amorphous‑Si caps have emerged as a leading passivation strategy because they suppress interface states, exhibit good thermal stability, and can be deposited at low temperature by physical vapor deposition (PVD) [7–13]. In this work we use magnetron sputtering to grow a‑Si on Ge(001), Ge(011) and Ge(111) wafers, then evaluate the resulting electrical performance.

Methods

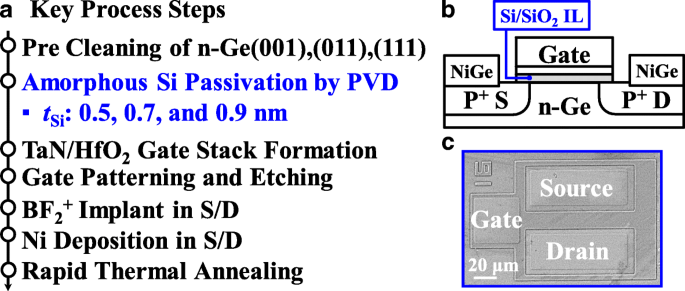

Figure 1a shows the process flow. After a dilute HF (1:50) clean, a 0.5–0.9‑nm a‑Si layer is sputtered at 50 W for 60–100 s. A 5‑nm HfO₂ gate dielectric is deposited by ALD (250 °C, TDMAHf/H₂O). A 50‑nm TaN gate electrode is sputtered, patterned, and etched. BF₂⁺ ions (30 keV, 1×10¹⁵ cm⁻²) are implanted into the source/drain, followed by 15‑nm Ni metallization and a 400 °C rapid thermal anneal for activation. Figures 1b and 1c illustrate the cross‑section and top‑view of a completed device.

a Process sequence showing the key steps employed to fabricate the Ge pMOSFETs with different tSi. b Cross‑sectional schematic of a Ge pMOSFET with SiO₂ IL. c Top‑view microscope image of a fabricated Ge pMOSFET

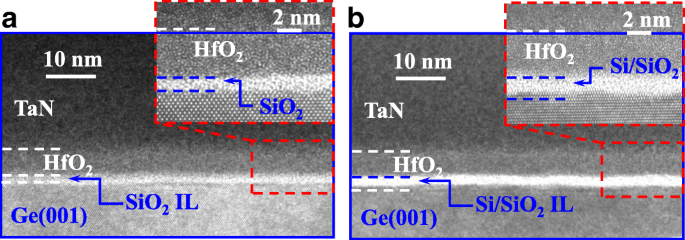

Transmission electron microscopy (TEM) of the 0.5‑nm and 0.9‑nm a‑Si stacks (Fig 2) reveals that the thinner cap is fully oxidized, whereas the thicker one retains two Si monolayers after annealing. The Si/SiO₂ interfacial layer (IL) therefore depends on the a‑Si thickness.

Cross‑sectional TEM images of Ge pMOSFET gate stacks with a 0.5‑nm tSi and b 0.9‑nm tSi. HRTEM insets show the Si/SiO₂ IL formed between HfO₂ and the Ge channel.

Results and Discussion

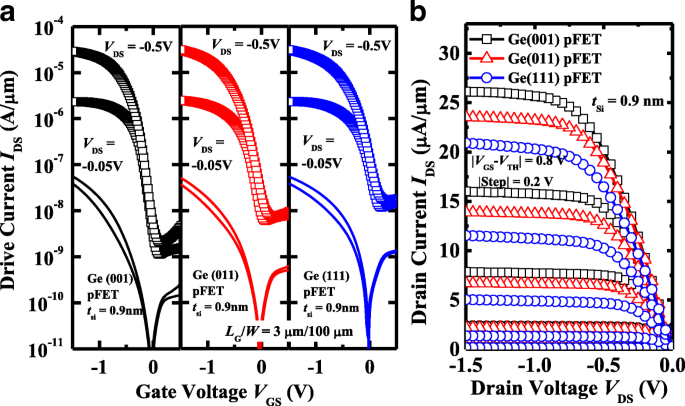

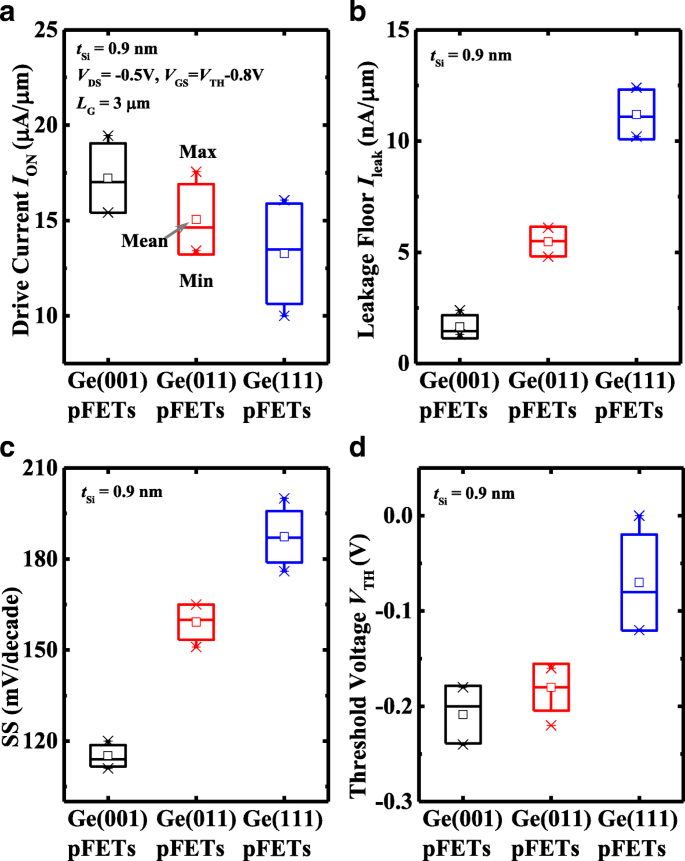

Figure 3a displays the I_D–V_G and I_G–V_G curves for (001), (011) and (111) devices with 0.9‑nm a‑Si. All devices exhibit excellent transfer characteristics (L_G = 3 µm, W = 100 µm, channel direction [110]). At a V_G–V_TH of –0.8 V, the (001) transistor delivers the highest I_ON (Fig 3b), which is attributed to its superior μ_eff. Statistical analysis (Fig 4) confirms that (001) devices have the highest I_ON, lowest leakage, best subthreshold swing (SS), and most favorable V_TH among the three orientations.

a Measured I_D–V_G and I_G–V_G curves of (001), (011) and (111) Ge pMOSFETs with 0.9‑nm tSi. b I_D–V_D curves measured at various V_G–V_TH for the devices.

Comparison of a I_ON, b leakage, c SS, and d V_TH for (001), (011) and (111) Ge pMOSFETs with 0.9‑nm tSi.

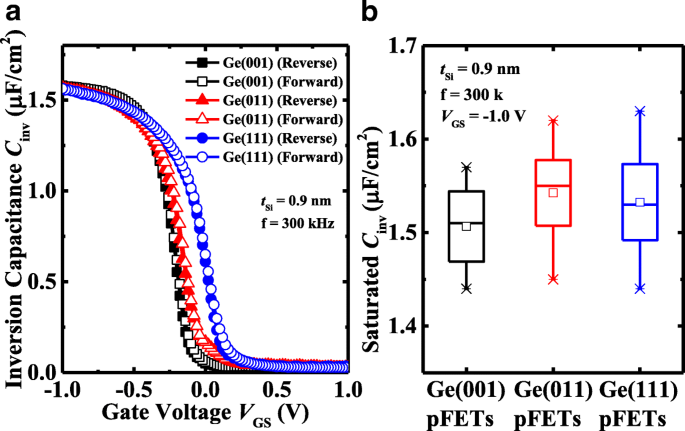

Capacitance–voltage measurements (Fig 5) show a nearly identical inversion capacitance (~1.56 µF/cm²) for all orientations, indicating that the a‑Si deposition rate is independent of crystal face. The resulting capacitive effective thickness (CET) is 2.2 nm. The slight V_TH shifts are consistent with minor doping variations across wafers.

a C_inv–V_G curves for Ge pMOSFETs with 0.9‑nm tSi on different orientations. b Statistical plots of saturated C_inv, showing negligible variation.

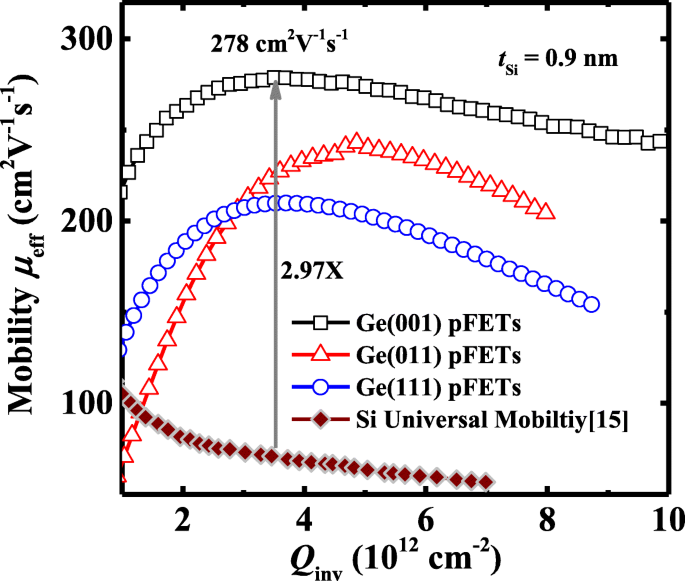

Mobility extraction (Fig 6) reveals a peak μ_eff of 278 cm²/V·s at Q_inv ≈ 3.5×10¹² cm⁻² for the (001) device—nearly three times the Si universal value. The higher μ_eff is attributed to a reduced density of interface states (D_it) rather than surface roughness, which is comparable across orientations.

μ_eff versus Q_inv for Ge pMOSFETs with 0.9‑nm tSi on (001), (011) and (111) substrates. The (001) device achieves a 2.97× improvement over the Si universal mobility at 3.5×10¹² cm⁻².

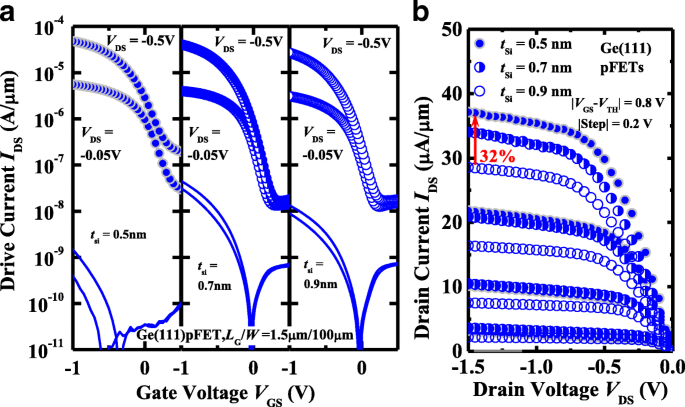

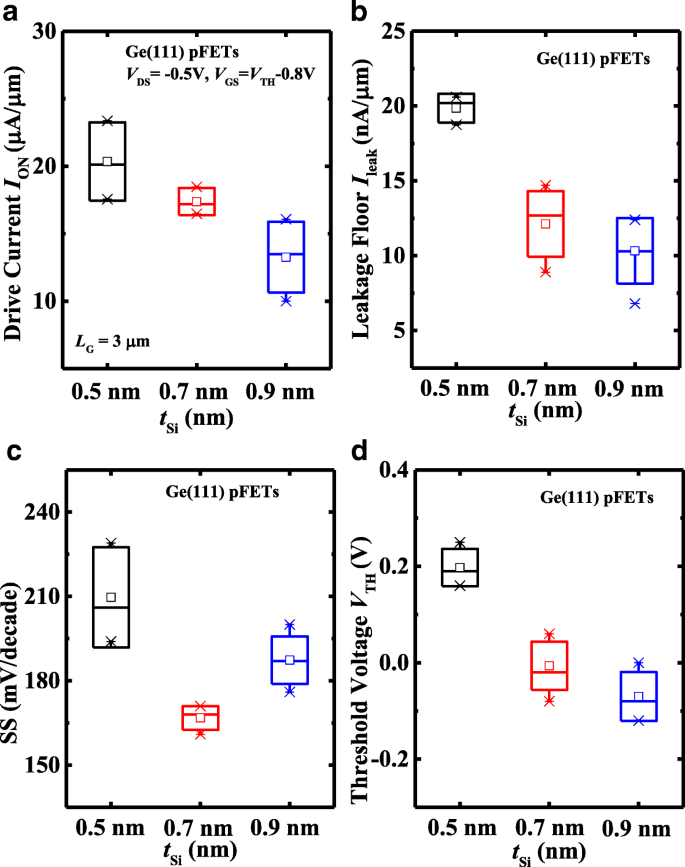

Figure 7 explores the impact of a‑Si thickness on (111) devices. Reducing tSi from 0.9 nm to 0.5 nm increases I_ON by 32 % at V_DS = –1.5 V and V_G–V_TH = –0.8 V, but simultaneously degrades SS and raises leakage, owing to a higher D_it. The trade‑off is quantified in Fig 8: thinner caps yield lower CET and higher C_inv, enhancing drive current, but higher D_it leads to poorer SS and leakage.

a I_D–V_G and I_G–V_G for (111) Ge pMOSFETs with various tSi. b I_D–V_D curves at V_DS = –0.05 V and –0.5 V.

Statistical comparison of a I_ON, b leakage, c SS, and d V_TH for (111) Ge pMOSFETs with tSi = 0.5, 0.7 and 0.9 nm.

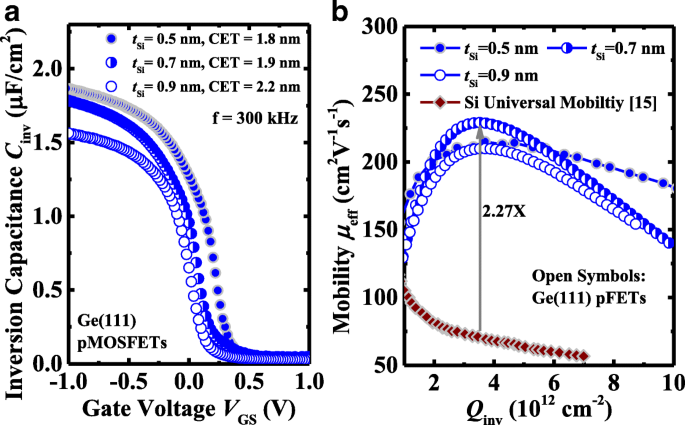

Figure 9 shows that the 0.5‑nm cap yields the highest μ_eff (229 cm²/V·s) at high Q_inv, but at the cost of increased D_it. The CET values extracted from C_inv–V_G (Fig 9a) are 1.8, 1.9 and 2.2 nm for tSi = 0.5, 0.7 and 0.9 nm, respectively.

a C_inv–V_G measured at 300 kHz for (111) devices with 0.5, 0.7 and 0.9 nm tSi. b μ_eff versus Q_inv for the same devices.

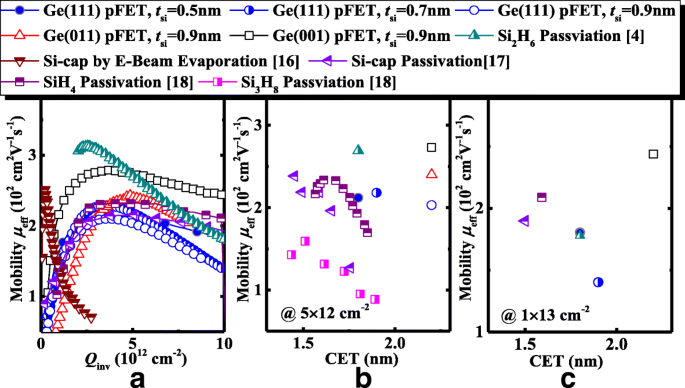

Benchmarking against literature (Fig 10) confirms that our a‑Si passivation delivers competitive μ_eff, though further optimization could close the gap with Si₂H₆‑based techniques.

a μ_eff for the Ge pMOSFETs in this work compared with published relaxed Ge devices. b and c Benchmarking of μ_eff at Q_inv = 5×10¹² cm⁻² and 1×10¹³ cm⁻², respectively, for various CET values.

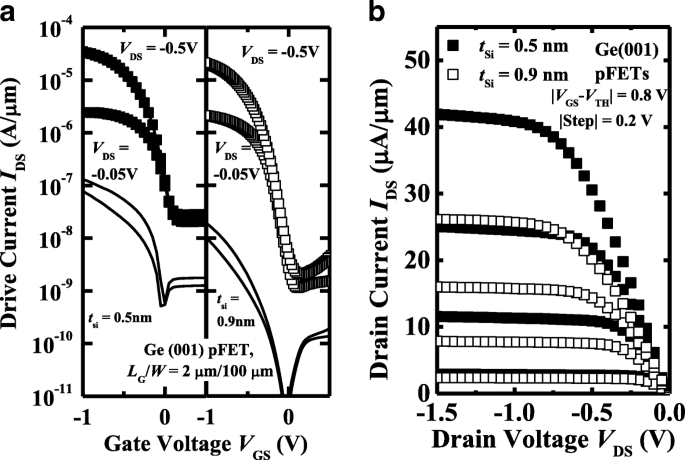

Finally, (001) devices with thinner a‑Si (0.5 nm) show improved I_ON but slightly higher leakage compared to the 0.9‑nm counterpart, illustrating the trade‑off between CET and D_it.

a I_D–V_G and I_G–V_G curves of (001) Ge pMOSFETs with 0.5 and 0.9 nm tSi. b I_D–V_G curves for the two devices.

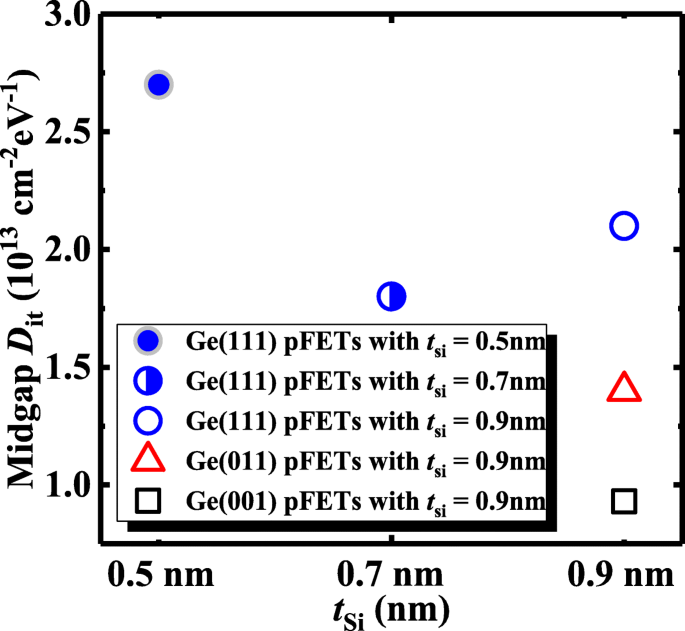

D_it was extracted from SS measurements (Eq. 1) and plotted against tSi for each orientation (Fig 12). The lowest D_it values are found for (001) devices with 0.9 nm and for (111) devices with 0.7 nm. This correlation explains the superior SS of the (001) devices.

D_it versus a‑Si thickness for Ge pMOSFETs on (001), (011) and (111) substrates.

Conclusions

Amorphous‑Si passivation by magnetron sputtering at room temperature produces Ge p‑MOSFETs with high drive current and low leakage, particularly on (001) substrates. A 0.9‑nm a‑Si cap yields a peak μ_eff of 278 cm²/V·s, a 2.97× increase over Si, and excellent SS. Reducing the cap thickness to 0.5 nm further boosts I_ON through a thinner CET, but at the expense of increased D_it, higher leakage, and degraded SS. These results demonstrate that both crystal orientation and a‑Si thickness must be optimized to balance drive, leakage, and interface quality in Ge‑based devices.

Abbreviations

- ALD

Atomic layer deposition

- BF₂⁺

Boron fluoride ion

- CET

Capacitive effective thickness

- Ge

Germanium

- GeOₓ

Germanium oxide

- HF

Hydrofluoric acid

- HfO₂

Hafnium dioxide

- HRTEM

High‑resolution transmission electron microscope

- IL

Interfacial layer

- MOSFETs

Metal‑oxide‑semiconductor field‑effect transistors

- Ni

Nickel

- Si

Silicon

- SS

Subthreshold swing

- TaN

Tantalum nitride

- TDMAHf

Tetrakis (dimethylamido) hafnium

Nanomaterials

- High‑Performance PEDOT:PSS/n‑Si Solar Cells with Textured Surfaces and Silver Nanowire Electrodes

- Enhanced Organic–Nanostructured Silicon Hybrid Solar Cells via Surface Modification for Superior Efficiency

- Ultra‑Low‑Power Resistorless Voltage Reference with Exceptional PSRR

- High‑Performance Germanium pMOSFETs via Ozone‑Induced GeOₓ Passivation: A Comparative Analysis with Plasma Post‑Oxidation

- Unveiling the Key Factors that Limit Carrier Transport in Ultra‑Thin Amorphous Sn‑Doped In₂O₃ Films with Superior Hall Mobility

- Optimizing Germanium pMOSFET Performance with ZrO₂ Dielectrics: The Role of Post‑Metal and Post‑Deposition Annealing

- High‑Performance All‑Perovskite Photodetector Delivering Ultrafast Response

- SnxPy Monolayers: Promising 2D Materials with High Stability, Exceptional Carrier Mobility, and Ferromagnetic Behavior

- Boost LiCoO₂ Battery Life at 4.5 V with Conductive Amorphous LLTO Thin‑Film Coating

- High-Mobility Germanium nMOSFETs Using ZrO₂ Gate Dielectric