Optimizing Germanium pMOSFET Performance with ZrO₂ Dielectrics: The Role of Post‑Metal and Post‑Deposition Annealing

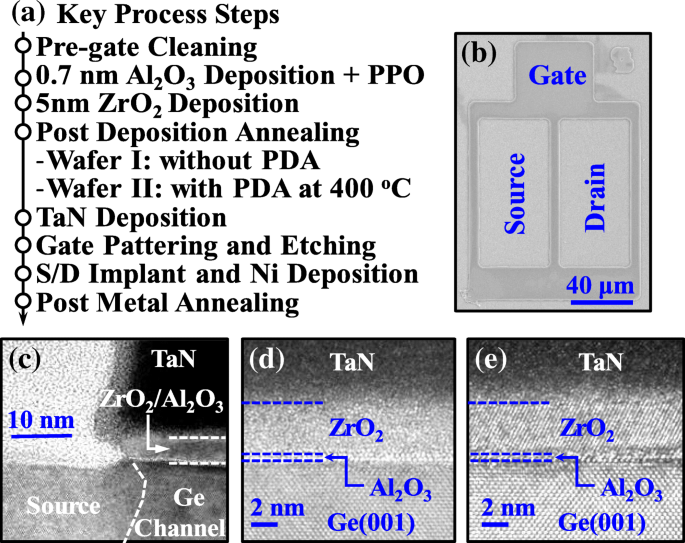

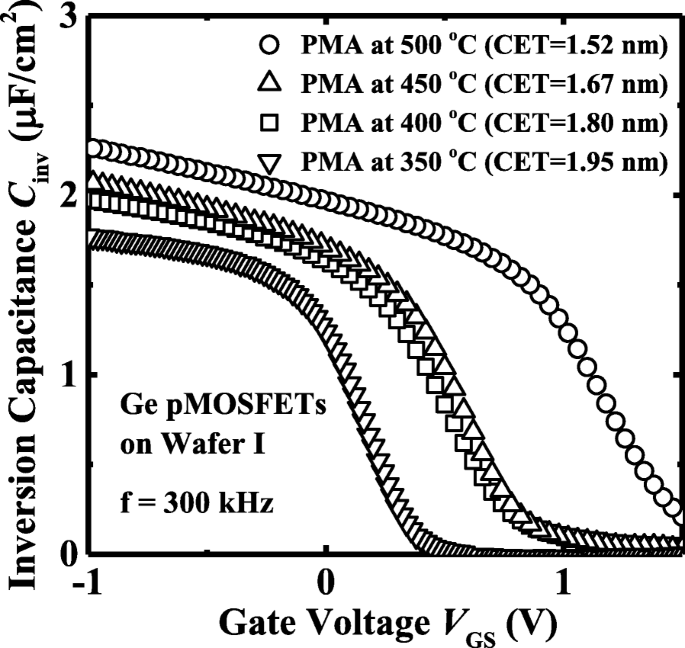

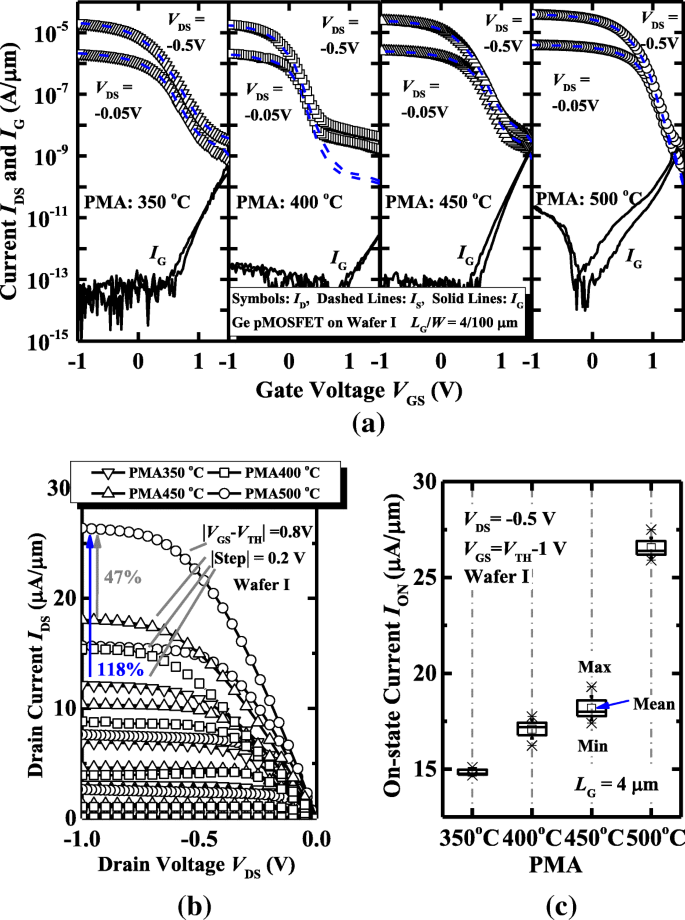

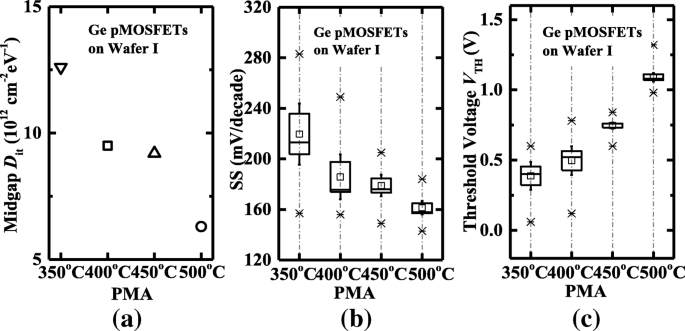

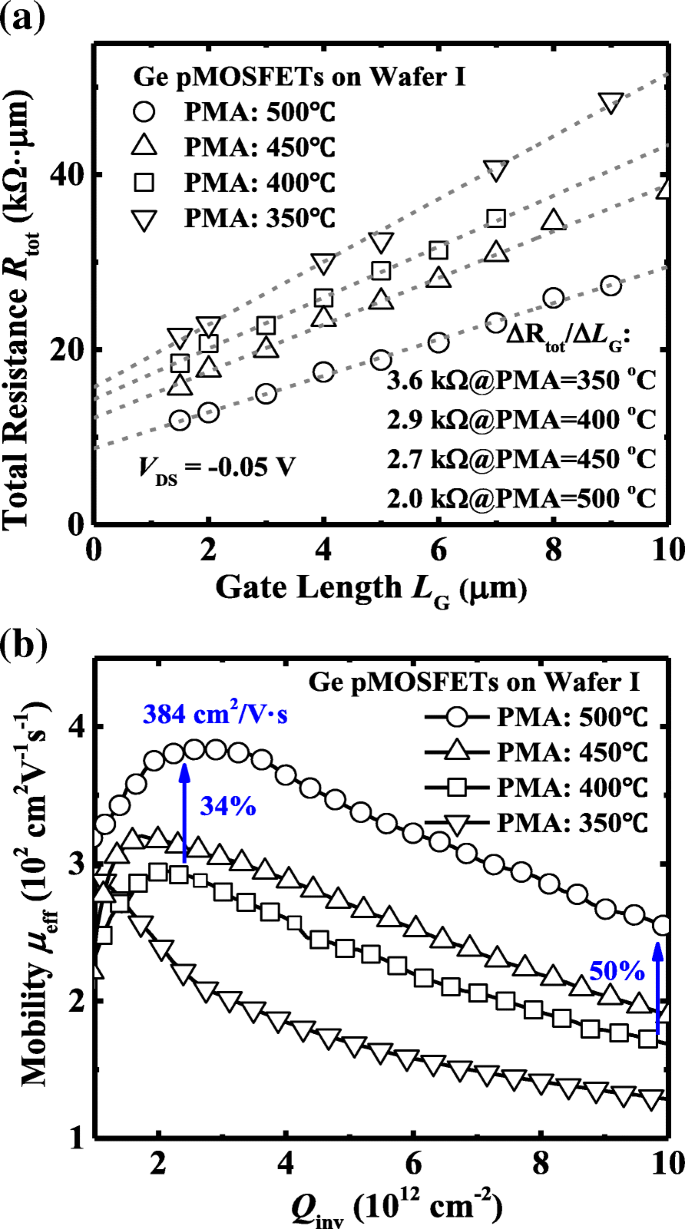

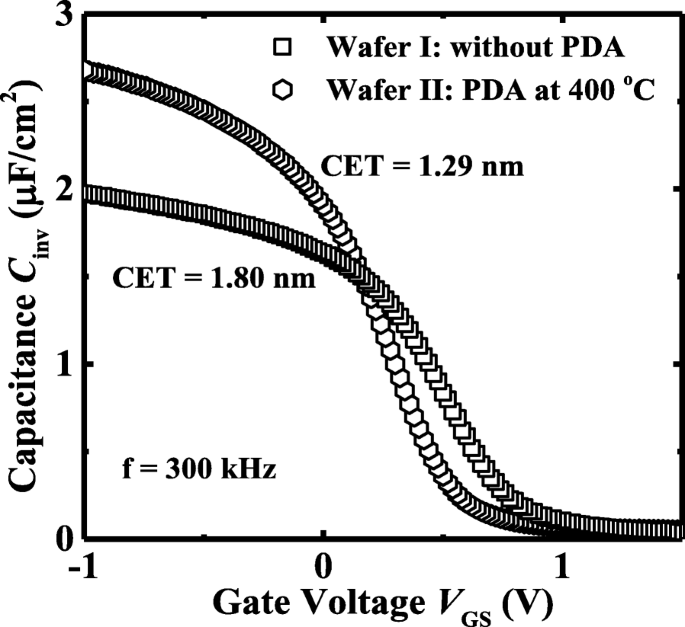

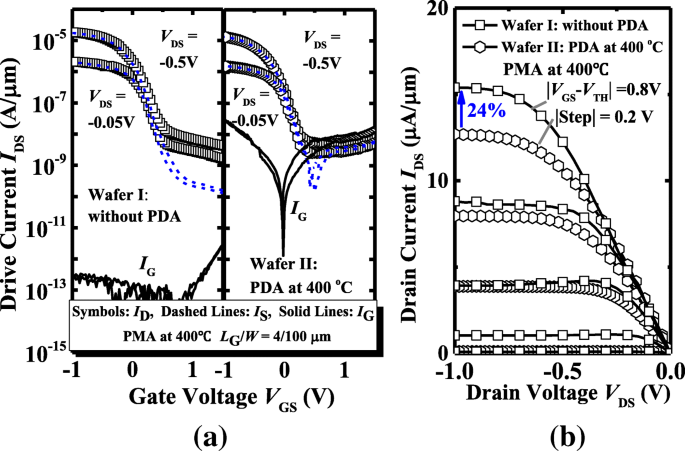

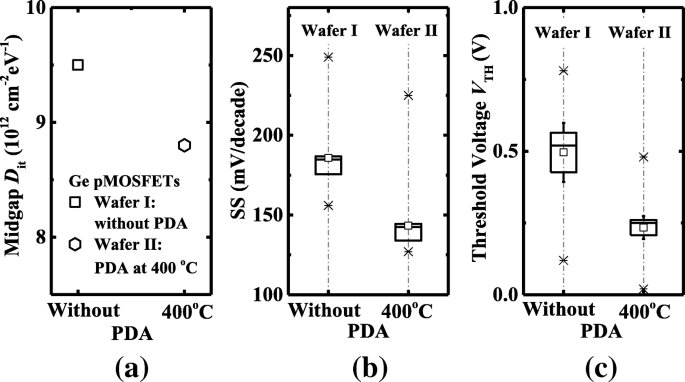

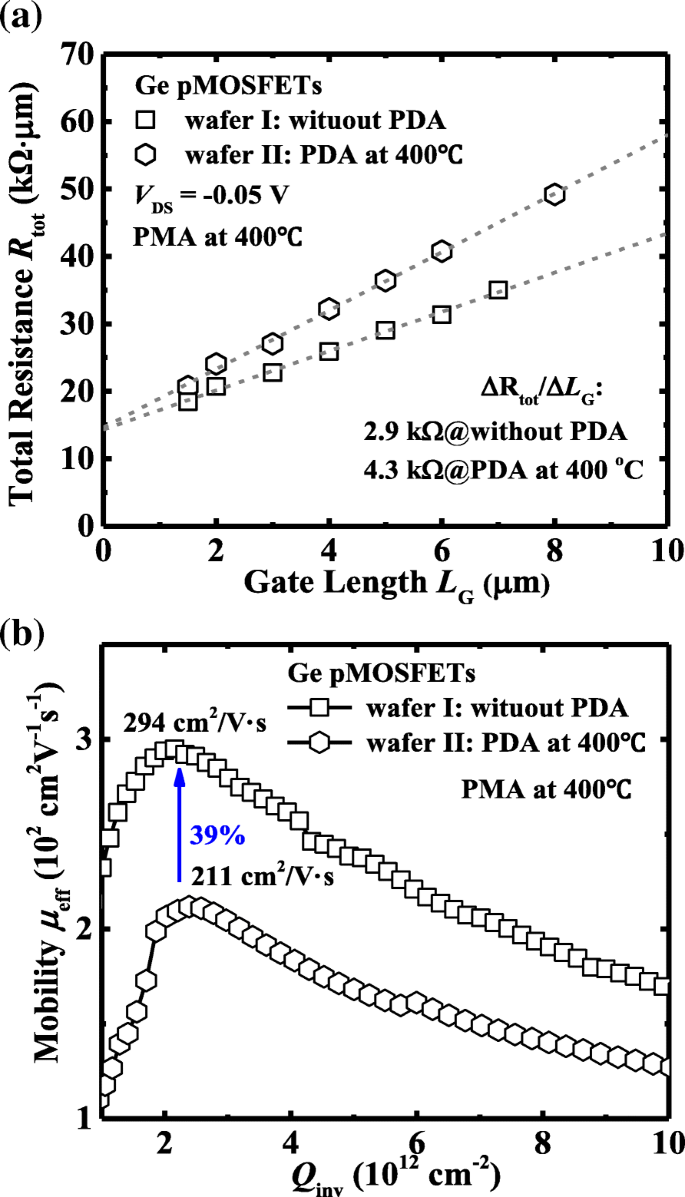

This study examines how post‑metal annealing (PMA) and post‑deposition annealing (PDA) influence the electrical performance of Germanium p‑type MOSFETs (pMOSFETs) that employ a ZrO₂ gate dielectric. Devices that skip PDA exhibit progressive improvements in on‑state current (I_ON), subthreshold swing (SS), and capacitance‑equivalent thickness (CET) as the PMA temperature is raised from 350 °C to 500 °C. The crystallization of ZrO₂ at higher PMA temperatures increases its permittivity and reduces the interface‑state density (D_it), leading to a lower CET and a higher effective hole mobility (μ_eff). Conversely, devices that receive a PDA step at 400 °C achieve a smaller CET and a steeper SS, yet their μ_eff is lower than devices without PDA. Germanium (Ge) is increasingly recognized as a high‑mobility p‑channel material for next‑generation CMOS, offering hole mobilities that exceed silicon by a significant margin [1–3]. To fully exploit this advantage, a gate dielectric of superior quality and robust surface passivation are essential for achieving high effective carrier mobilities (μ_eff) and drive currents in Ge transistors [4–7]. Several high‑k dielectrics—HfO₂, ZrO₂, La₂O₃, and Y₂O₃—have been explored to reduce the capacitance‑equivalent thickness (CET) below 1 nm. Among them, ZrO₂ stands out due to its high dielectric constant (κ ≈ 28–30 in the crystalline phase) and excellent interfacial quality with Ge [12–14]. Crystallization of ZrO₂ has been shown to lower CET and boost μ_eff [15, 16], yet the impact of different annealing routes on device performance remains under‑studied. This work investigates how PMA and PDA affect Ge pMOSFETs with ZrO₂ dielectrics, demonstrating that higher PMA temperatures markedly enhance μ_eff and reduce CET. The fabrication flow of Ge pMOSFETs with ZrO₂ dielectrics is illustrated in Figure 1a. Devices were grown on n‑type Ge(001) wafers (0.088–0.14 Ω·cm). After sequential HF (1:50) clean and DI rinse, the wafers entered an ALD chamber. An ozone‑post‑oxidation (OPO) step—depositing a 1‑nm Al₂O₃ layer at 300 °C followed by 15 min of in‑situ OPO—provided surface passivation. Subsequently, a 5‑nm ZrO₂ layer was deposited at 250 °C using TDMAZr and H₂O precursors, with the Zr source heated to 85 °C. Select samples underwent PDA at 400 °C for 60 s in a rapid‑thermal annealer (wafer II); the remaining wafers served as the no‑PDA group (wafer I). A 100‑nm TaN gate was sputtered, patterned, and etched. Source/drain regions were formed by BF₂⁺ implantation (30 keV, 1 × 10¹⁵ cm⁻²), followed by 15‑nm Ni contacts via lift‑off. Finally, PMA was performed at 350, 400, 450, and 500 °C for 30 s to activate dopants and complete metallization. a Fabrication flow for Ge pMOSFETs with ZrO₂. b SEM image of a finished transistor. c XTEM cross‑section showing the gate stack and source/drain. d HRTEM of a device annealed at 400 °C. e HRTEM of a device annealed at 500 °C. Figure 1b presents an SEM view of a typical device, while Figure 1c displays the XTEM cross‑section highlighting the gate, dielectric, and source/drain regions. Figures 1d and 1e show that the ZrO₂ layer is fully crystallized after PMA at 500 °C, with an Al₂O₃ interfacial thickness of ≈ 0.7 nm. Figure 2 shows inversion capacitance (C_inv) versus gate voltage (V_GS) measured at 300 kHz for devices on wafer I. Extracted CET values are 1.95, 1.80, 1.67, and 1.52 nm for PMA temperatures of 350, 400, 450, and 500 °C, respectively. The reduction in CET with higher PMA is attributed to ZrO₂ crystallization, which increases κ from ~20–23 (amorphous) to ~28–30 (crystalline) and lowers bulk trap density. This shift in C‑V curves confirms improved dielectric quality. Inversion C_inv–V_GS curves for Ge pMOSFETs on wafer I with PMA at 350, 400, 450, and 500 °C. Figure 3a presents transfer characteristics and gate leakage (I_G) for the devices on wafer I. All transistors have L_G = 4 µm and W = 100 µm. Gate leakage remains below the drain current for all PMA temperatures. Notably, the device annealed at 500 °C achieves an I_ON/I_OFF ratio > 10⁴. Figure 3b shows I_D–V_DS curves at different overdrives (|V_GS – V_TH|). Compared to 350 °C, the 500 °C device exhibits 47 % and 118 % higher drive currents at V_DS = –1.0 V and |V_GS – V_TH| = 0.8 V, respectively. Figure 3c summarizes I_ON statistics at V_DS = –0.5 V and |V_GS – V_TH| = –1 V, confirming that 500 °C annealing delivers superior on‑state performance due to reduced source/drain resistance, lower CET, and higher μ_eff. a I_D, I_S, and I_G vs. V_GS for devices annealed at 350, 400, 450, and 500 °C. b I_D–V_DS curves at various overdrives. c 500 °C device shows the highest I_ON. Figure 4 presents statistical plots of midgap D_it, SS, and V_TH for the different PMA temperatures. Extracted D_it values (via the maximum‑conductance method) are 1.3 × 10¹³, 9.5 × 10¹², 9.2 × 10¹², and 6.3 × 10¹² cm⁻² eV⁻¹ for 350, 400, 450, and 500 °C, respectively. The 500 °C device demonstrates the steepest SS due to the smallest D_it and CET. Although D_it and SS remain above the best‑reported Ge transistors, further optimization of the OPO process (Al₂O₃ thickness, oxidation temperature, duration) could yield additional improvements. V_TH shifts positively with increasing PMA temperature, reflecting reduced CET and D_it. Overall, the optimal electrical performance is achieved with PMA at 500 °C. Comparison of a midgap D_it, b SS, and c V_TH for devices annealed at 350, 400, 450, and 500 °C. Effective hole mobility (μ_eff) is extracted using the ΔR_tot/ΔL_G method [18] across devices with L_G ranging from 1.5 to 9 µm. Figure 5a shows R_tot versus L_G at |V_GS – V_TH| = –1 V and V_DS = –0.05 V; the corresponding R_SD values are 7.85, 7.15, 6.10, and 4.35 kΩ·µm for 350, 400, 450, and 500 °C, indicating improved dopant activation at higher PMA temperatures. The slope ΔR_tot/ΔL_G is smallest for the 500 °C device, yielding a peak μ_eff of 384 cm² V⁻¹ s⁻¹—31 % higher than the 400 °C counterpart. At high inversion charge densities (Q_inv ≈ 1 × 10¹³ cm⁻²), the 500 °C device maintains superior mobility. Crystalline ZrO₂ reduces bulk trap density, thereby minimizing remote Coulomb scattering, and the smoother ZrO₂/Ge interface reduces surface‑roughness scattering, shifting the peak mobility to higher Q_inv. a R_tot vs. L_G at |V_GS – V_TH| = –1 V and V_DS = –0.05 V for devices with various PMA temperatures. b μ_eff vs. Q_inv, highlighting the peak at 500 °C. We next examine the influence of PDA on device characteristics. Figure 6 compares C_inv–V_GS for devices on wafer I (no PDA) and wafer II (PDA at 400 °C) annealed at 400 °C. The PDA device exhibits a markedly lower CET (1.29 nm vs. 1.80 nm). Figure 7a shows that PDA increases gate leakage, likely due to the reduced CET. However, the device without PDA delivers a 24 % higher drive current at the same overdrive (–0.8 V) in the saturation region, as illustrated in Figure 7b. C_inv–V_GS plots for devices on wafer I and II annealed at 400 °C. a I_D, I_S, and I_G vs. V_GS for devices on wafer I and II (400 °C PMA). b I_D–V_DS curves at various overdrives. Figure 8 summarizes statistical results of D_it, SS, and V_TH for devices with and without PDA. The PDA device shows a lower D_it and a mean SS of 142 mV/decade, indicating an improved ZrO₂/Ge interface. V_TH differs between the two groups, reflecting variations in trap density near the bandgap. Comparison of a D_it, b SS, and c V_TH for devices on wafer I and II annealed at 400 °C. Figure 9 shows R_tot vs. L_G for the 400 °C PMA devices. R_SD is 7.15 kΩ·µm (no PDA) and 7.30 kΩ·µm (PDA). The PDA device exhibits a peak μ_eff of 211 cm² V⁻¹ s⁻¹, lower than the 400 °C no‑PDA device. The reduced mobility is attributed to enhanced remote Coulomb scattering from fixed charges in the ZrO₂ dielectric. a R_tot vs. L_G for wafer I and II (400 °C PMA). b μ_eff vs. Q_inv for devices with and without PDA. We have systematically explored how PMA and PDA affect Ge pMOSFETs with ZrO₂ dielectrics. Crystallization of the ZrO₂ gate dielectric, achieved by PMA at 500 °C, substantially lowers CET and boosts hole mobility—yielding a peak μ_eff of 384 cm² V⁻¹ s⁻¹ and enhanced drive current. While a PDA step at 400 °C further reduces CET and D_it, it compromises mobility and increases leakage compared to devices without PDA. Thus, high‑temperature PMA without PDA is the preferred route for optimizing Ge pMOSFET performance. The datasets supporting the conclusions of this article are included in the article. Atomic layer deposition Boron fluoride ion Capacitance‑equivalent thickness Germanium Hydrofluoric acid High‑resolution transmission electron microscope Interfacial layer Metal‑oxide‑semiconductor field‑effect transistors Nickel Post‑deposition annealing Post‑metal annealing Subthreshold swing Tantalum nitride Tetrakis (dimethylamido) zirconium Zirconium dioxide Effective carrier mobilityAbstract

Background

Methods

Results and Discussion

Conclusions

Availability of Data and Materials

Abbreviations

Nanomaterials

- Compliance‑Free ZrO₂/ZrO₂₋ₓ/ZrO₂ Tri‑Layer Resistive Memory Enables Controllable Interfacial Multistate Switching

- Microwave Annealing Boosts Dielectric Performance of Al₂O₃/ZrO₂/Al₂O₃ MIM Capacitors

- Ultra‑Low‑Power Resistorless Voltage Reference with Exceptional PSRR

- High‑Mobility Germanium p‑MOSFETs with Amorphous Silicon Passivation: Surface‑Orientation Effects

- Boosting PERC Solar Cell Performance: ALD‑Deposited Al₂O₃ with Optimized Two‑Step Annealing for Superior Si Passivation

- High‑Performance Germanium pMOSFETs via Ozone‑Induced GeOₓ Passivation: A Comparative Analysis with Plasma Post‑Oxidation

- Unveiling the Key Factors that Limit Carrier Transport in Ultra‑Thin Amorphous Sn‑Doped In₂O₃ Films with Superior Hall Mobility

- High‑Performance All‑Perovskite Photodetector Delivering Ultrafast Response

- SnxPy Monolayers: Promising 2D Materials with High Stability, Exceptional Carrier Mobility, and Ferromagnetic Behavior

- High-Mobility Germanium nMOSFETs Using ZrO₂ Gate Dielectric