High‑Performance Germanium pMOSFETs via Ozone‑Induced GeOₓ Passivation: A Comparative Analysis with Plasma Post‑Oxidation

Abstract

We compare the electrical performance of germanium pMOSFETs that receive a GeOx passivation layer formed by either ozone post‑oxidation (OPO) or plasma post‑oxidation (PPO). Both processes are applied to an Al2O3/n‑Ge (001) substrate, followed by a 5‑nm HfO2 gate dielectric deposited in situ by ALD. X‑ray photoelectron spectroscopy (XPS) and transmission electron microscopy (TEM) confirm that the PPO treatment introduces a positive threshold‑voltage shift and a lower ION/IOFF ratio, indicating a degraded interface. In contrast, OPO yields a four‑order‑of‑magnitude higher ION/IOFF ratio, a steeper sub‑threshold swing, and superior carrier mobility. A thicker Al2O3 blocking layer in the OPO process further enhances mobility. Overall, OPO provides a more effective route to a high‑quality Ge/oxide interface and improved effective mobility in Ge pMOSFETs.

Background

Conventional CMOS devices are nearing their physical limits, making it difficult to boost performance with silicon alone. Germanium, with its higher carrier mobility, has emerged as a promising channel material, but achieving a low‑density interface state (Dit) remains a challenge due to the instability of GeO2 and dangling bonds. Numerous strategies have been explored to passivate the Ge/dielectric interface, such as pre‑depositing silicon monolayers or engineering self‑passivation via intentional GeO2 growth. Oxidation techniques—including high‑pressure oxidation, ozone, H2O plasma, and electron‑cyclotron‑resonance (ECR) plasma—have been employed to reduce Dit and enhance thermal stability.

Recent studies have demonstrated high‑performance Ge MOSFETs by post‑oxidation through an Al2O3/Ge interface. For example, a Ge CMOS inverter on Ge‑on‑insulator (GeOI) used rapid thermal annealing in pure O2 to grow GeOx after a 1‑nm Al2O3 layer. Ozone oxidation, which is more reactive than O2, enables lower‑temperature growth, and has been shown to improve GeOx thickness control and device performance. However, a systematic comparison between ozone and plasma post‑oxidation on the same Al2O3/n‑Ge interface has been lacking.

In this work, we fabricate Ge pMOSFETs using both OPO and PPO on Al2O3/n‑Ge interfaces and compare their electrical characteristics. All other process steps are identical. The influence of Al2O3 block‑layer thickness and the underlying mobility‑degradation mechanisms are also examined. Our results demonstrate that OPO is a superior passivation method for future Ge MOSFET technology.

Methods

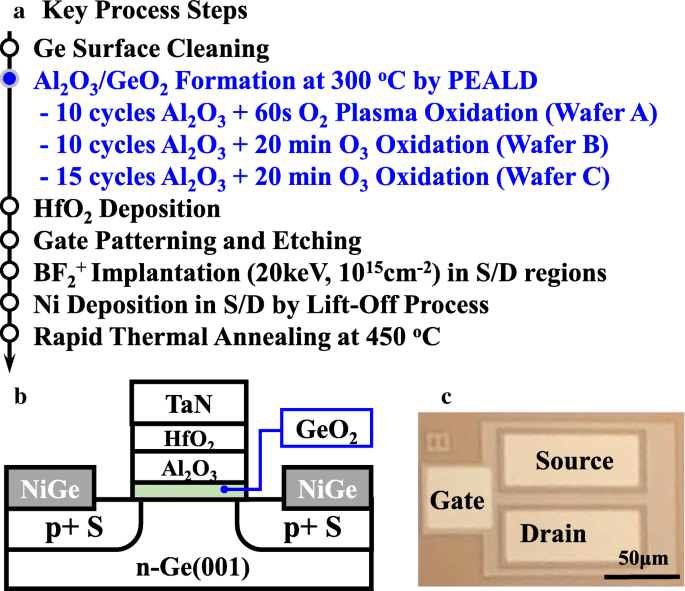

Ge pMOSFETs were fabricated on 4‑inch n‑Ge (001) wafers (resistivity 0.14–0.183 Ω cm). After a dilute HF (1:50) clean, a ~1 nm Al2O3 film was deposited at 300 °C by plasma‑enhanced ALD (PEALD) using trimethylaluminium (TMA) and H2O. The thin Al2O3/GeO2 interfacial layer (denoted AlOx/GeOx) was then subjected to either 60 s of oxygen plasma (PPO) via a remote plasma source or to a 20‑min ozone (OPO) treatment in a 50 % O3/O2 mixture. Immediately after oxidation, a 5‑nm HfO2 gate dielectric was deposited at 300 °C by ALD (60 cycles, using TDMAHf and H2O). A 100‑nm TaN gate metal was sputtered, followed by lithography and etching. Source/drain regions were self‑aligned BF2+ implanted (20 keV, 1 × 1015 cm−2), capped with 20 nm Ni, and activated by rapid thermal annealing at 450 °C for 30 s.

a Process flow for Ge pMOSFET fabrication with three passivation methods. b Schematic and c SEM image of the fabricated transistor.

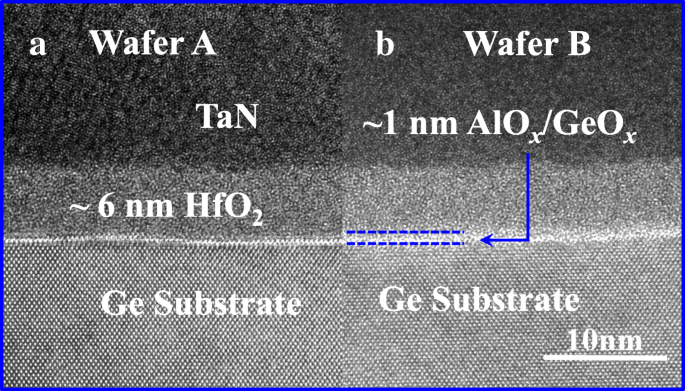

Cross‑sectional TEM images reveal the gate stack TaN/HfO2/AlOx/GeOx/Ge for PPO and OPO. In the PPO sample, a distinct AlOx/GeOx interlayer separates HfO2 from Ge, whereas the OPO sample shows a more diffuse interface, consistent with literature reports on GeO2 thickness.

Cross‑sectional TEM of the high‑k/metal gate stack with (a) OPO‑formed and (b) PPO‑formed AlOx/GeOx interfacial layers on n‑Ge (001).

Results and Discussion

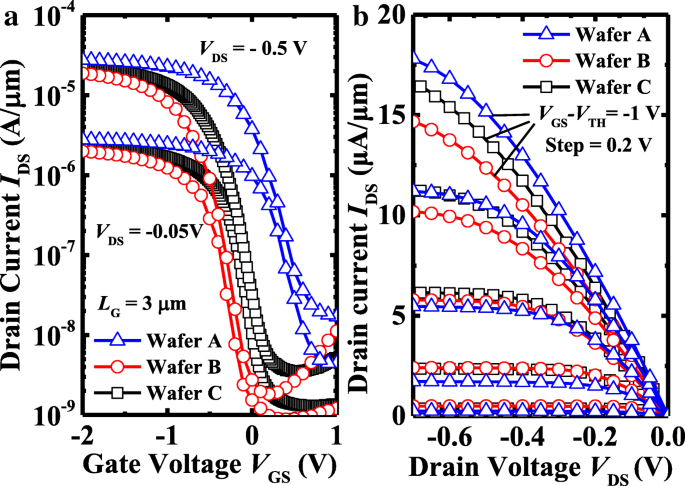

Device characterization was performed with a Keithley 4200‑SCS system. All transistors have a 3 µm gate length. The PPO device (wafer A) shows higher saturated drain current but also a higher OFF‑state current compared to the OPO devices (wafers B and C). Importantly, the OPO devices operate in enhancement mode, whereas the PPO device remains in depletion mode, indicating residual p‑type character due to a higher Dit.

a IDS–VGS and b IDS–VDS for PPO (wafer A) and OPO (wafers B, C) Ge pMOSFETs.

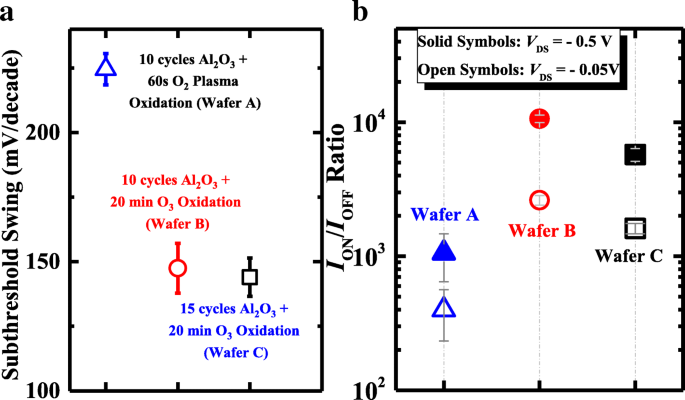

Statistical analysis of the ION/IOFF ratio and sub‑threshold swing (SS) confirms that OPO devices achieve up to four orders of magnitude higher ION/IOFF and a steeper SS, reflecting a cleaner interface. Increasing the Al2O3 block thickness from 10 to 15 cycles improves the ON‑state current but reduces the ION/IOFF ratio due to a larger equivalent oxide thickness (EOT).

Statistical plots of a SS and b ION/IOFF for PPO versus OPO devices.

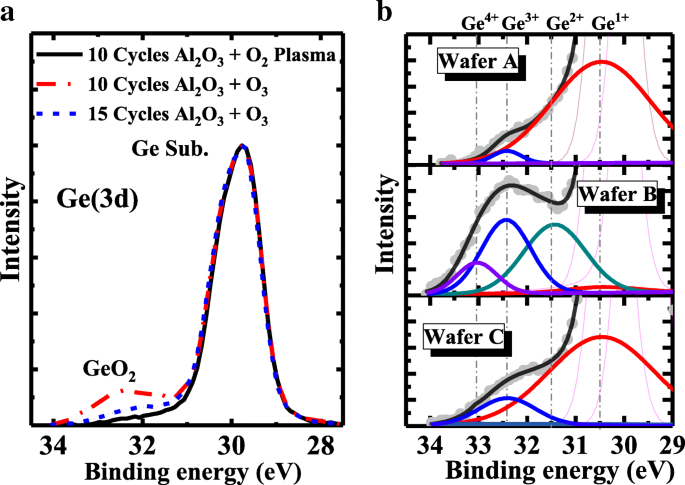

XPS measurements on dummy samples (without HfO2 and TaN) reveal that PPO produces a GeOx layer dominated by Ge1+ and Ge3+ species, while OPO yields a higher oxidation state distribution, reducing the Ge1+ component and indicating a more complete GeO2 formation.

a Ge 3d XPS spectra for Al2O3/GeOx/Ge under PPO, OPO‑10, and OPO‑15 conditions. b Peak fitting of the Ge 3d spectra.

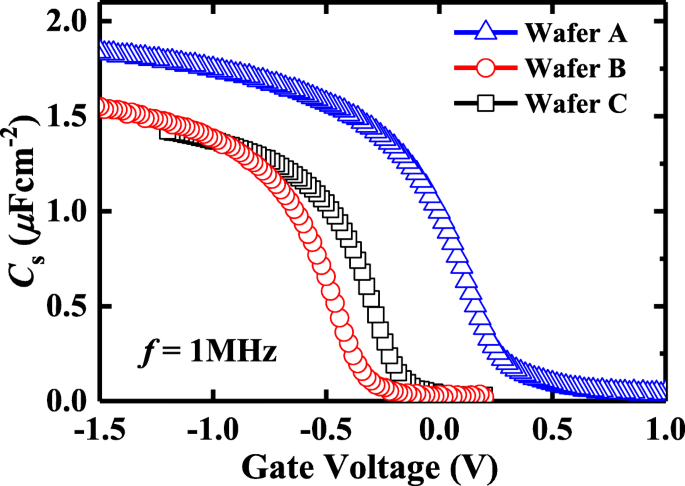

Gate‑to‑source C‑V measurements at 1 MHz show that the OPO process results in a higher EOT compared to PPO, with the 15‑cycle OPO (wafer C) exhibiting the largest EOT. This is attributed to the thicker Al2O3 blocking layer. Despite the higher EOT, the OPO devices maintain superior SS and mobility.

Gate‑to‑source C‑V of PPO (wafer A) and OPO (wafers B, C) devices.

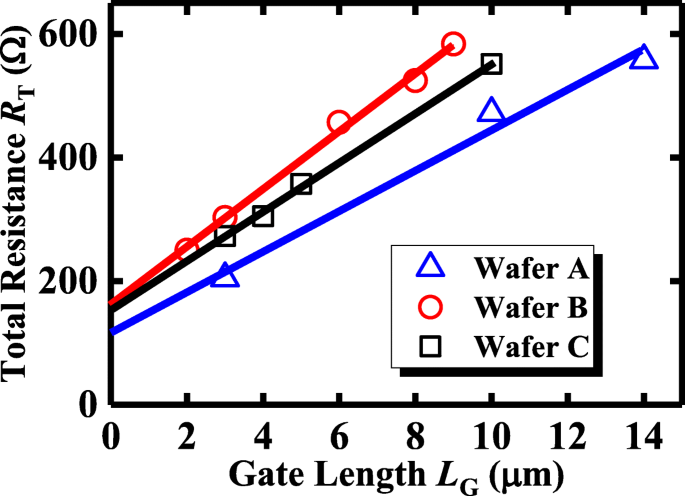

Total resistance (RT) versus gate length analysis indicates that PPO devices have lower series and channel resistances, consistent with the C‑V data. However, the higher RSD and RCH for OPO devices are compensated by improved mobility.

RT versus LG for the three device types.

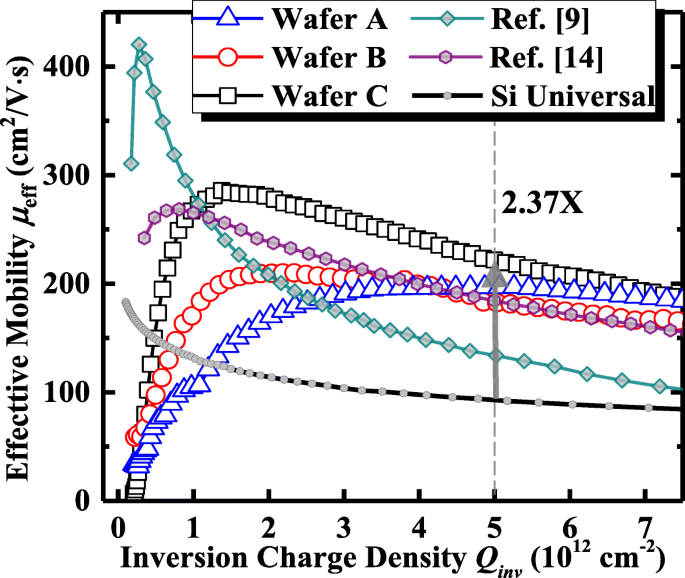

Effective hole mobility (μeff) was extracted from the total‑resistance slope. OPO devices exhibit higher peak μeff than PPO, with wafer C (15‑cycle OPO) achieving 283 cm2/Vs. Compared with literature, this represents a 2.37× improvement over silicon’s universal mobility at an inversion charge density of 5 × 1012 cm−2. The mobility advantage is attributed to reduced Coulomb scattering and better interface quality.

μeff versus Qinv for PPO and OPO devices. The 15‑cycle OPO (wafer C) reaches a peak μeff of 283 cm2/Vs.

Conclusions

We have demonstrated that Ge pMOSFETs with GeOx passivation fabricated via ozone post‑oxidation outperform those using plasma post‑oxidation. OPO yields higher ION/IOFF ratios, steeper sub‑threshold swings, and superior peak μeff. Increasing the Al2O3 blocking layer thickness in the OPO process improves mobility at the cost of a larger EOT. These findings confirm that OPO is an effective passivation strategy for high‑quality Ge/oxide interfaces, making it a promising candidate for next‑generation Ge MOSFET technology.

Abbreviations

- Al2O3:

Aluminum oxide

- ALD:

Atomic layer deposition

- BF2+:

Boron fluoride ion

- EOT:

Equivalent oxide thickness

- Ge:

Germanium

- GeOx:

Germanium oxide

- HF:

Hydrofluoric acid

- HfO2:

Hafnium dioxide

- TEM:

Transmission electron microscope

- MOSFETs:

Metal‑oxide‑semiconductor field‑effect transistors

- OPO:

Ozone post‑oxidation

- PPO:

Plasma post‑oxidation

- Qinv:

Inversion charge density

- SS:

Subthreshold swing

- XPS:

X‑ray photoelectron spectroscopy

- μeff:

Effective hole mobility

Nanomaterials

- Enduring Success: Lessons in Persistence from Abraham Lincoln and Maintenance Leadership

- Lowering Metal–Ge Contact Resistance with ZnO Interlayers and Argon Plasma: Achieving Ohmic Al Contacts on n‑Ge

- High‑Mobility Germanium p‑MOSFETs with Amorphous Silicon Passivation: Surface‑Orientation Effects

- Boosting PERC Solar Cell Performance: ALD‑Deposited Al₂O₃ with Optimized Two‑Step Annealing for Superior Si Passivation

- Optimizing Germanium pMOSFET Performance with ZrO₂ Dielectrics: The Role of Post‑Metal and Post‑Deposition Annealing

- PdO‑CeO₂ Rod‑Like Nanoporous Catalysts with Superior CO Oxidation and Methane Combustion Performance

- AlGaN/GaN HEMTs with 803 V Breakdown: Fluorine‑Doped SiNx Passivation Yields Low Dynamic ON‑Resistance

- Enhanced Gene Delivery Using Gold Nanoparticles Functionalized with Chitosan, N‑Acylated Chitosan, and Chitosan Oligosaccharide

- High‑Stability Voltage Regulator with Transient Enhancement & PSR Boost

- Enhancing Thermoelectric Performance: Silicon Substrates with Highly Doped Porous Si via Metal-Assisted Chemical Etching