Micro Magic Unveils RISC‑V Core Delivering 110,000 CoreMarks/Watt

California‑based EDA firm Micro Magic, after announcing the world’s fastest RISC‑V core, has now set a new performance benchmark: 8,000 CoreMarks at 3 GHz.

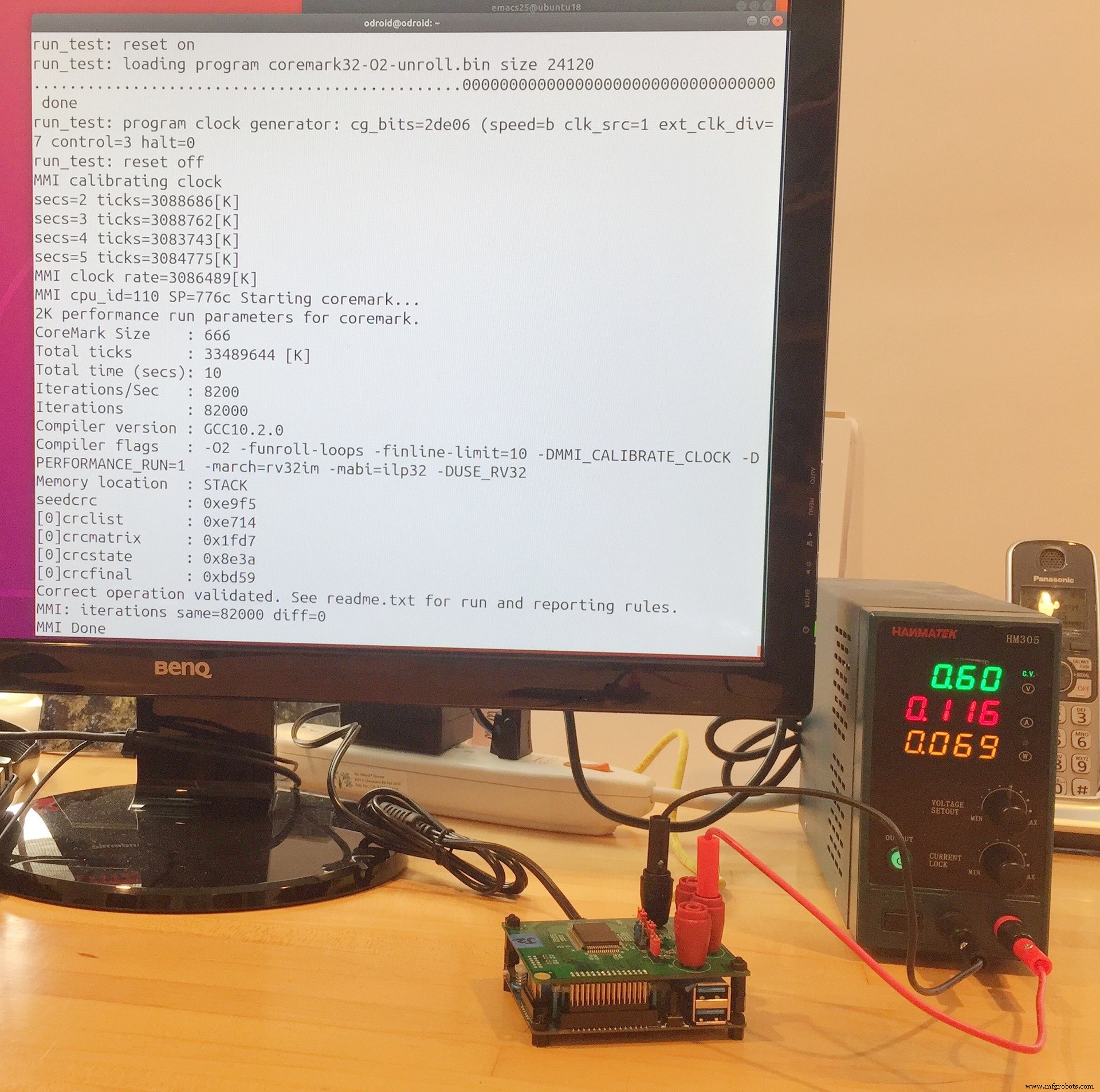

Co‑founder Mark Santoro said, “After hitting 13,000 CoreMarks at 5 GHz, we surpassed expectations with 8,000 CoreMarks at 3 GHz while consuming under 70 mW. Leveraging our advanced EDA tools, Micro Magic produced silicon that closely matched simulations, all within record‑time and with a small team.” This translates to roughly 110,000 CoreMarks per watt.

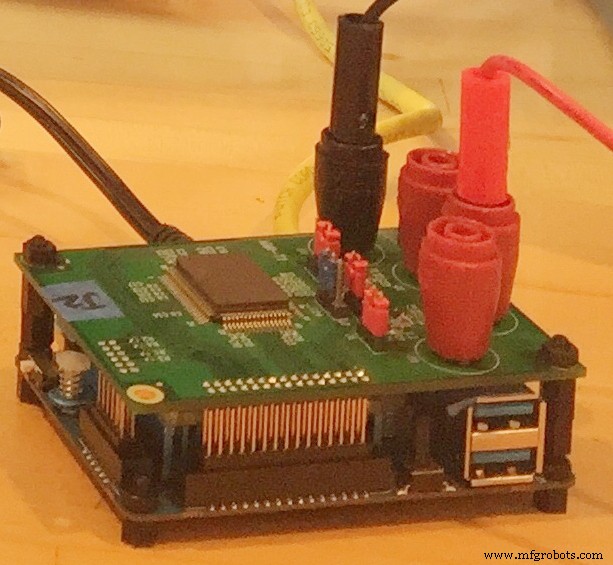

Earlier, Micro Magic told EE Times that its core outperforms both the Apple M1 and the Arm Cortex‑A9. In a demonstration on an Odroid board, the core reached 4.327 GHz at 0.8 V and 5.19 GHz at 1.1 V. A single core at 0.8 V delivers 11,000 CoreMarks at 4.25 GHz while drawing just 200 mW.

Andy Huang, advisor and creator of the FineSim simulator, noted, “Using the EEMBC benchmark, we achieved 55,000 CoreMarks per watt. The M1 chip scores roughly 10,000 CoreMarks in EEMBC terms—about 100 CoreMarks per watt across its eight cores and 15 W total. The fastest Arm processor, the quad‑core Cortex‑A9, scores 22,343 CoreMarks; divided by four cores and 5 W per core, that’s 1,112 CoreMarks per watt.”

In its most recent press release, Micro Magic emphasized that 110,000 CoreMarks per watt far outpaces existing parts. A quick survey of processors in the 3–5 GHz range shows its RISC‑V CPU exceeds any CISC, RISC, or MIPS implementation by more than tenfold.

Lee Tavrow, co‑founder, said, “For mobile applications, the difference between a device lasting a day versus several on a single charge is crucial. Low‑power devices typically sacrifice performance, but our IP delivers both world‑class speed at 5 GHz and low power at 70 mW at 3 GHz in the same silicon.”

Huang highlighted that CoreMarks per watt matters more than per MHz in battery‑operated devices. “A typical 5‑W device can host 25 cores—something the mobile industry rarely does. For companies needing reduced battery consumption, like Tesla, our core provides the necessary performance.”

Although Micro Magic has operated as an EDA services company, it plans to license the RISC‑V core to customers. “Our architecture scales across mobile, PCs, automotive, and data centers. We are fully self‑funded and not seeking external capital,” he said.

Founded in 1995, sold to Juniper Networks for $260 million, and revived in 2004 by the original founders, Micro Magic specializes in three‑dimensional TSV layout tools. It can load, view, and edit designs of over one trillion transistors in real time. Mark Santoro and Lee Tavrow previously developed a 300 MHz SPARC processor at Sun Microsystems.

The team believes it has realized David Patterson’s original RISC vision, delivering high performance within today’s battery budgets. Huang said, “We truly appreciate Patterson’s architecture. We’re extending its boundaries by enabling unprecedented power efficiency.”

Embedded

- Advantech Launches Edge AI Inference Systems with Allxon & Trend Micro for Secure Remote Management

- NSITEXE Launches NS31A, a RISC‑V 32‑bit CPU Meeting ISO 26262 ASIL D for Automotive Safety

- RISC‑V Summit 2020: Key Sessions & Highlights

- Ensuring Trustworthiness in Processor Design: Best Practices for Secure and Reliable ICs

- STM32WB50: Dual-Core Wireless MCU for Secure IoT Applications

- Infineon Unveils IMC300 Motor Controller with Integrated Arm Cortex‑M0 for Enhanced Flexibility

- RISC‑V Based Open‑Source GPU Architecture (RV64X)

- RISC‑V International and CHIPS Alliance Launch OmniXtend Working Group to Enhance Cache Coherency Standards

- congatec Unveils 100 W Ecosystem for High‑Performance Embedded Edge and Micro Servers

- Understanding JTAG and Arm Core Debugging: ADI and SWD Explained