Arm Unveils Ethos-U65 microNPU for Cortex‑A Application Processors

Arm has released the Ethos-U65, a next‑generation microNPU IP designed to integrate seamlessly with Cortex‑A CPU cores in application processors. The IP, licensed by NXP, will power a new line of i.MX processors that support advanced AI workloads such as pose estimation, multi‑face recognition, video object detection, and full‑speech recognition beyond keyword spotting.

Ethos-U65

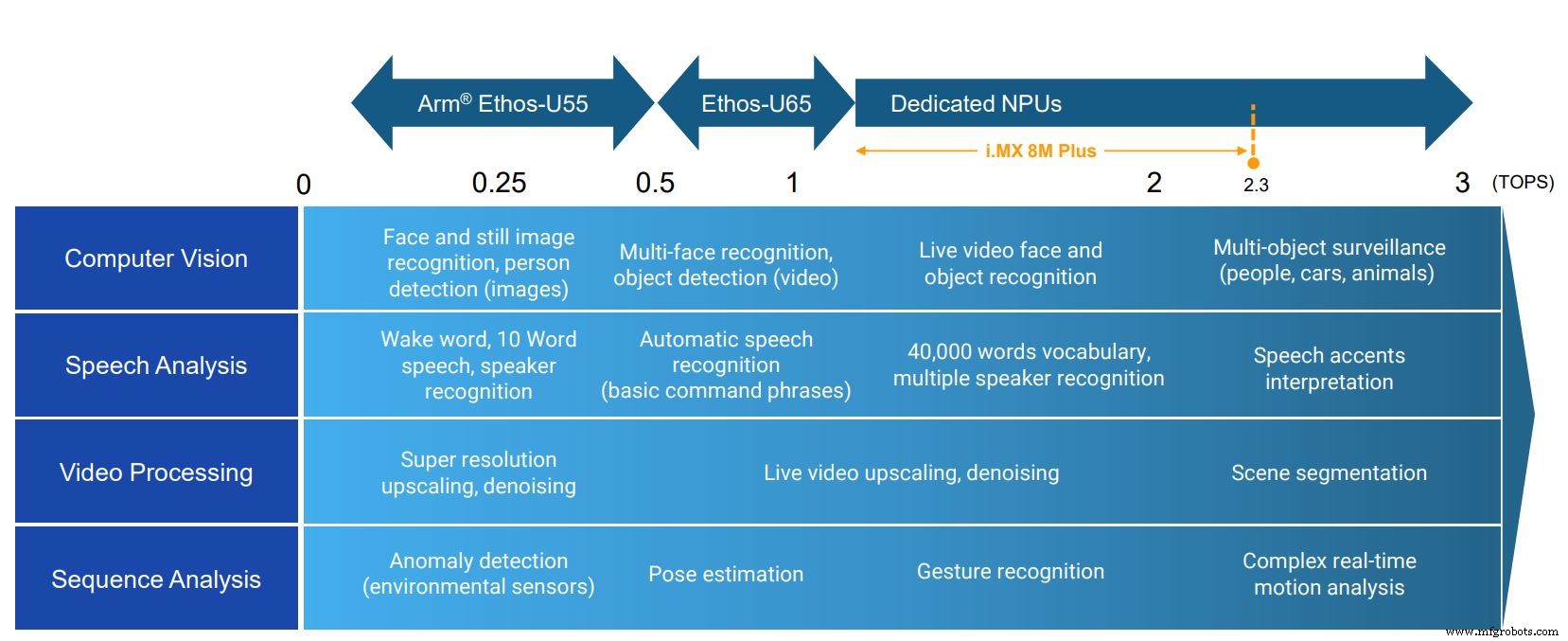

Arm’s earlier microNPU, the Ethos‑U55, debuted in February 2020 for microcontroller‑class systems paired with Cortex‑M cores, delivering up to 0.5 TOPS at 1 GHz in 16 nm or 7 nm nodes and featuring 3 to 256 MAC units. Arm’s broader portfolio includes the Ethos‑N77 (4 TOPS), N57 (2 TOPS), and N37 (1 TOPS).

The Ethos‑U65 builds on the U55’s low‑power design but doubles the MAC count to 512, enabling 1 TOPS at 1 GHz. Tailored for application‑processor environments, it also expands native support for machine‑learning operators, according to Arm’s technical brief.

Lead licensee

NXP, acting as the lead licensee, collaborated with Arm to define the system‑level specifications for the U65. The company announced plans to embed the microNPU into its forthcoming i.MX family of application processors.

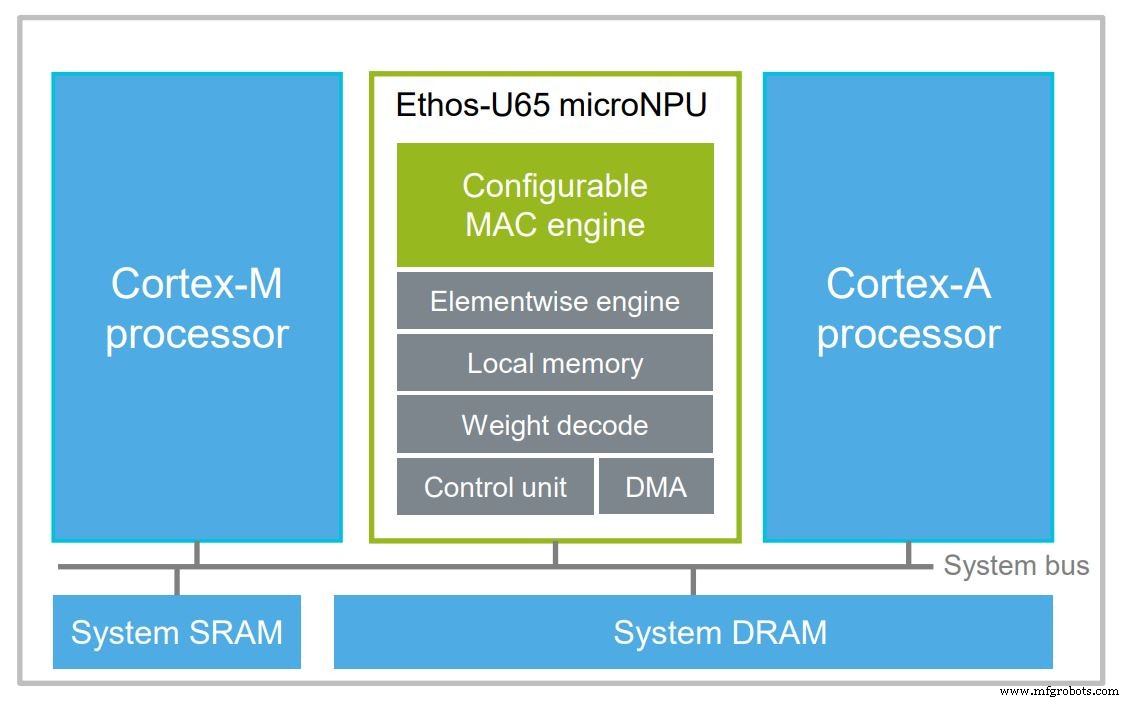

The NXP architecture for an AI application processor combines Cortex‑A and Cortex‑M cores with a microNPU (Image: NXP)

In the envisioned AI processor, the Ethos‑U65 sits alongside Cortex‑M and Cortex‑A cores, as explained by Ben Eckermann, NXP’s Chief Engineer of AI/ML Hardware. The Cortex‑A handles the application stack—drivers for peripherals such as microphones or cameras—while the microNPU and Cortex‑M tackle the machine‑learning workload, returning results to the Cortex‑A.

“Like the U55, the U65 relies on a nearby Cortex‑M to support operators that are rarely invoked and may not warrant full hardware implementation,” Eckermann noted. “This design offers flexibility and a degree of future‑proofing.”

The U65 features wider internal buses compared to the U55 and is engineered to accommodate the buffering and latency characteristics of DRAM, which is common in application‑processor systems, whereas Cortex‑M environments typically use SRAM.

Populating the portfolio

NXP is expanding its AI‑enabled SoC lineup. The previously announced i.MX 8M+ processors already house an NPU accelerator based on a Verisilicon design that delivers 2.3 TOPS, sufficient for tasks such as scene segmentation, live video face and object recognition, and speech accent interpretation. At the lower end, NXP’s microcontrollers with the Ethos‑U55 can perform person detection, wake‑word detection, and video denoising.

The Ethos‑U65‑enabled products will occupy the middle tier, handling AI applications such as multi‑face recognition, more sophisticated speech recognition, and pose estimation. According to Eckermann, this positioning ensures no overlap with the i.MX 8M+ line.

Compute requirements for various AI applications and the corresponding NPU (Image: NXP)

>> This article was originally published on our sister site, EE Times.

Embedded

- Application Spotlight: 3D Printing Revolutionizes Bearing Design and Production

- Revolutionizing Footwear: 3D Printing Drives Innovation, Customization, and Faster Time to Market

- Makerarm: The All‑in‑One Desktop Robotic Arm for Makers

- Arm Introduces Custom Instruction Support for Cortex‑M Cores, Expanding Flexibility

- Choosing Industrial Flash Storage: A Comprehensive Guide to Reliability, Temperature, and Long‑Term Support

- Cervoz Ultra‑Thin M.2 NVMe SSDs: High‑Performance Storage for Industrial Edge Applications

- NXP Launches i.MX 8M Plus: A Multicore Edge Processor with Built‑In Neural Processing Unit

- Arm Introduces Cortex‑M55 & Ethos‑U55: New IP Cores Empowering TinyML on Low‑Power Endpoints

- Edge AI Acceleration: Leading Specialized Processors for 2024

- Embedded Artists iMX8M COM Board – A Versatile ARM Cortex‑A53/Cortex‑M4F Platform