Ta2O5/TaOx Bi‑Layer via Low‑Temperature Annealing Boosts CBRAM Reliability

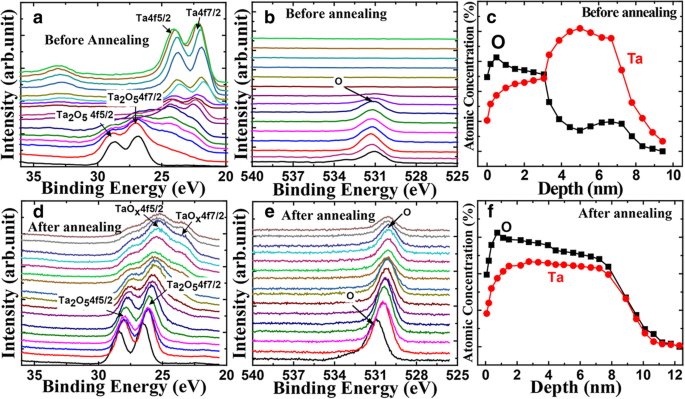

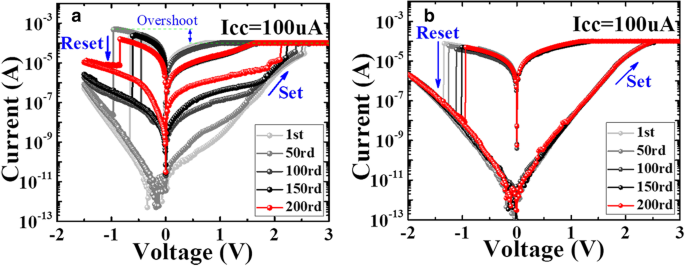

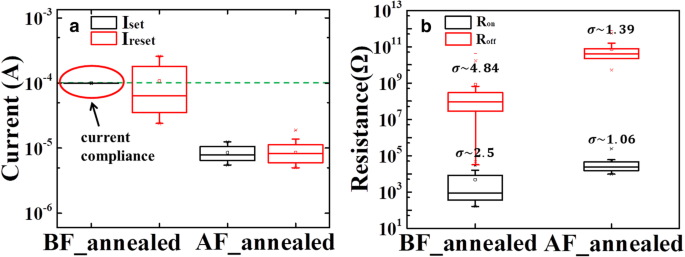

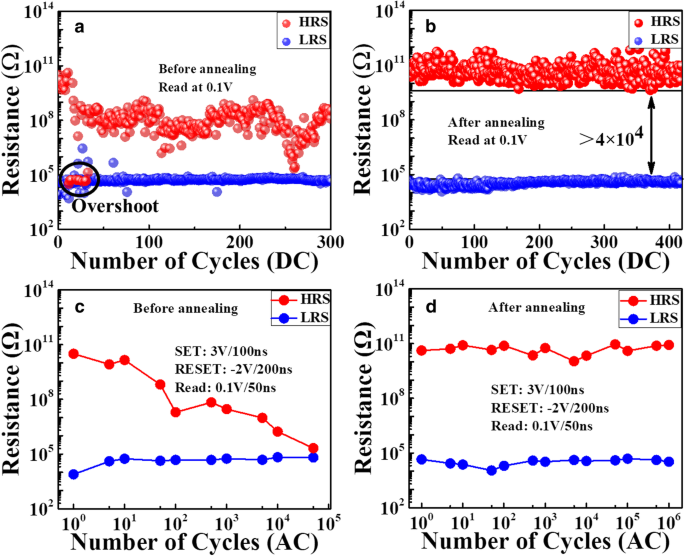

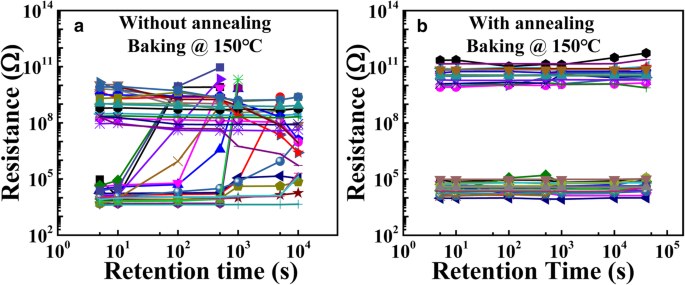

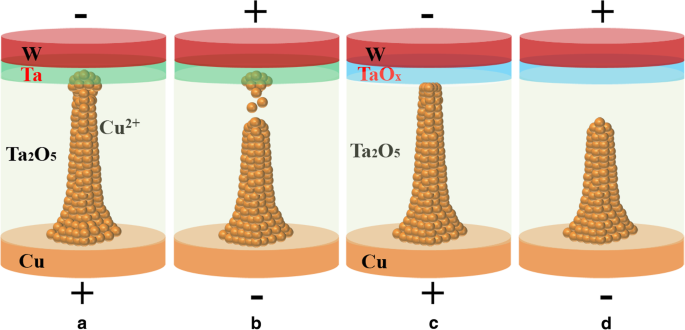

Bi‑layer architectures are routinely employed to enhance the reliability of conductive‑bridge random‑access memory (CBRAM). Here we introduce a cost‑effective, CMOS‑compatible method that generates a Ta2O5/TaOx bi‑layer through a low‑temperature anneal. The TaOx overlayer serves as an external resistor that limits the set‑current, enabling self‑compliance and eliminating the overshoot that broadens the high‑resistance state (HRS) and low‑resistance state (LRS) distributions. Consequently, the LRS retention is markedly improved thanks to defect annealing within the switching film. This approach offers a straightforward route to bolster CBRAM reliability. Conductive‑bridge resistive‑switching memory (CBRAM) is a promising next‑generation non‑volatile memory technology, prized for its exceptional scalability, minimal structural complexity, compatibility with 3‑D integration, and rapid switching speeds [1–3]. Despite these advantages, reliability issues—particularly data retention and endurance—remain the principal obstacles to commercial deployment. Structure engineering has emerged as the most effective strategy to mitigate these challenges [4–7]. For instance, Zhao et al. introduced a nano‑porous graphene interlayer that confines cation injection and markedly improves device performance [8], although its fabrication complexity hinders CMOS integration. Gong et al. demonstrated a CMOS‑compatible, self‑aligned CuSiN interfacial layer that enhances low‑resistance state (LRS) retention [9]. Similarly, Cao et al. employed a TiN barrier to suppress filament overgrowth and eliminate negative‑SET behavior [10]. While these bi‑layer designs successfully enhance reliability, they often entail complex process flows or reduced programming speed. Here we present a CMOS‑compatible, low‑temperature annealing technique that spontaneously forms a Ta2O5/TaOx bi‑layer. The resultant structure not only improves reliability but also preserves programming speed by avoiding a separate forming step. We show that the TaOx layer acts as a series resistor that enforces self‑compliance during set operations, thereby suppressing filament overgrowth and stabilizing the HRS/LRS distributions. Device fabrication began with a 1 µm‑diameter tungsten (W) plug serving as the bottom electrode (BE) after chemical‑mechanical polishing. A 5 nm Ta film was deposited via DC magnetron sputtering and subsequently oxidized in a plasma‑enhanced chemical vapor deposition (PECVD) chamber at 350 °C for 300 s in O2, yielding Ta2O5. A 40 nm copper (Cu) top electrode (TE) was then sputtered and patterned by lithography. Cell definition was achieved by reactive ion etching in an SF6/C3F8 mixture using the TE as a hard mask, followed by BE isolation using the Al pad. Finally, a CMOS‑compatible low‑temperature anneal at 400 °C for 30 min was applied to the entire stack, inducing the formation of the TaOx overlayer. Device dimensions were dictated by the 1 µm2 BE area. For comparison, a non‑annealed reference was also fabricated. Electrical characterization employed a Keithley 4200‑SCS semiconductor parameter analyzer, with voltage applied to the Cu TE while the W BE was grounded. X‑ray photoelectron spectroscopy (XPS) was used to examine the chemical states of Ta and O in the Ta2O5 films before and after annealing. The surface spectra revealed a characteristic Ta2O5 4f doublet (binding energies 26.70 eV and 28.60 eV) indicating the presence of fully oxidized Ta (Fig. 1a). Depth‑profiling showed that, beneath the surface, metallic Ta peaks (22.33 eV and 23.96 eV) appeared in the un‑annealed sample, confirming incomplete oxidation. After annealing, the spectra displayed coexistence of Ta2O5 and Ta4+ states up to ~4 nm depth, with a gradual reduction of the Ta5+ component and a uniform O signal throughout the film (Fig. 1d–f). These results demonstrate that the anneal transforms adsorbed oxygen into lattice oxygen, forming a ~3.5 nm TaOx overlayer atop the 4 nm Ta2O5. The XPS shows depth profile of Ta before (a) and after (d) annealing. b, e Depth profile of O before and after annealing, respectively. c, f Atomic concentration profile of O and Ta with depth before and after annealing, respectively Figure 2a,b compare the I–V characteristics of Cu/Ta2O5/W devices with and without annealing under a DC sweep. Both devices start in a high‑resistance state (Rinitial ≈ 10^9 Ω and 10^10 Ω, respectively), with the annealed device exhibiting a higher Rinitial due to the thicker oxide. Importantly, the annealed cell does not require a separate forming step. In the un‑annealed device, the LRS is reached abruptly at a critical voltage, accompanied by an overshoot that yields a RESET current far exceeding the compliance limit. This instability manifests as a highly variable HRS/LRS window (~ 20× over 200 cycles, Fig. 3b). Conversely, the annealed cell displays a gradual current increase that naturally clamps at the compliance current, eliminating overshoot and achieving a stable memory window of ~ 10^4× across cycles (Fig. 2b). Typical I‑V curves of Cu/TaOx/W devices before annealing (a) and after annealing (b) with 200 cycles a Set and RESET Current distributions before and after annealing, respectively. b The resistance distribution of HRS and LRS before/after annealing The absence of overshoot in the annealed device is further evidenced by the narrow IRESET distribution and its alignment with the ISET values (Fig. 3a). Device‑to‑device uniformity was quantified by measuring RON and ROFF across 20 cells. The annealed devices exhibited RON values between 10^4 Ω and 10^5 Ω, while the un‑annealed devices spanned 10^2 Ω to 10^5 Ω, reflecting the series resistance contributed by TaOx. The standard deviation of ROFF dropped from 4.84 to 1.39, underscoring the improved uniformity. Cycling under DC conditions revealed that the un‑annealed device loses its HRS/LRS ratio after ~ 10^4 cycles, with occasional soft errors (Fig. 4a). In stark contrast, the annealed device maintains a robust ~ 10^4 ratio over 10^6 cycles (Fig. 4b). Pulse‑mode endurance tests, optimized for 3 V/100 ns (SET), –2 V/200 ns (RESET), and 0.1 V/50 ns (READ), confirm the superior durability of the annealed structure (Fig. 4c,d). The enhanced endurance is attributed to the TaOx layer’s suppression of filament overgrowth into the counter electrode, which otherwise hampers RESET and induces negative‑SET behavior. The cycling results of a the devices without annealing under 300 DC cycles and b the devices with annealing under 400 DC cycles. c, d Endurance characteristics under AC mode with the optimized operation configuration: set 3 V/100 ns; RESET – 2 V/200 ns. Up to 10^6 cycles were obtained for the device after annealing Retention tests at 150 °C demonstrate that un‑annealed devices fail within 10^4 s, whereas annealed cells retain both HRS and LRS over the entire measurement window (Fig. 5a,b). An Arrhenius analysis extrapolates an 85 °C lifetime of ≈ 10 years for the annealed devices, consistent with state‑of‑the‑art CBRAM performance [17,18]. The improved retention is attributed to defect annealing that slows Cu ion diffusion. Retention characteristics of the HRS/LRS for a un‑annealed device and b annealed device at 150 °C Figure 6 illustrates the switching mechanism. In the un‑annealed stack (Cu/Ta2O5/Ta/W), Cu ions migrate through Ta2O5, forming a conductive filament that overgrows into the counter electrode during SET. During RESET, residual Cu+ ions drift back, leaving a partial filament tip and reducing HRS variability. In the annealed stack (Cu/Ta2O5/TaOx/W), the high‑resistance TaOx layer presents a diffusion barrier (Cu diffusivity ≈ 4.9 × 10^−20 cm^2 s^−1 vs. 1.0 × 10^−6 cm^2 s^−1 in Ta), effectively limiting filament growth and yielding a more stable RESET. The physical modeling for the switching behavior of the annealed and un‑annealed devices. a Set and b RESET process for the un‑annealed device with the structure of Cu/Ta2O5/Ta/W. c Set and d RESET process for the annealed device with the structure of Cu/Ta2O5/TaOx/W. The filament overgrowth is suppressed by the TaOx layer formed during the annealing process By integrating a TaOx overlayer via a low‑temperature anneal, we fabricated a Ta2O5/TaOx bi‑layer CBRAM that exhibits self‑compliance, superior HRS/LRS uniformity, and markedly enhanced endurance and retention. This simple, CMOS‑compatible approach offers a cost‑effective route to meet the reliability demands of next‑generation non‑volatile memory. Conductive bridge random access memory High‑resistance states Low‑resistance states Non‑volatile memory Plasma‑enhanced chemical vapor deposition Top electrodeAbstract

Introduction

Methods

Results and Discussion

Conclusions

Abbreviations

Nanomaterials

- Comprehensive Review of Resistive Random‑Access Memory (RRAM) Modeling and Simulation Techniques

- Stochastic Oxygen Vacancy Model Explains Variability in RRAM Cells

- Dual Functionality of V/SiOx/AlOy/p++Si Devices: Selector and Memory Switching Controlled by Compliance Current

- Nanocrystal‑Embedded‑Insulator FeFETs: Ultra‑Thin Ferroelectric Gates for Low‑Voltage Logic and Robust Non‑Volatile Memory

- Enhanced Reliability of a-IGZO TFTs via Clean Etch‑Stopper Layer and Reduced Feature Size

- Ultra‑Low‑Power HfO₂/TiOₓ Bi‑Layer RRAM Achieves 1.12 µW Switching via Controlled Oxygen Vacancy Engineering

- Resistive Random‑Access Memory (RRAM): Materials, Switching, Performance, MLC Storage, Modeling, and Real‑World Applications

- Ultra‑Low‑Voltage 2D MoS2 Ferroelectric Memory Transistor with Hf₁₋ₓZrₓO₂ Gate for CMOS Compatibility

- Proactive Early-Detection Circuit Enhances Endurance of Backfilled Contact RRAM Arrays

- Understanding PLA Conductivity: Electrical Properties of 3D Printing Filament