Nanocrystal‑Embedded‑Insulator FeFETs: Ultra‑Thin Ferroelectric Gates for Low‑Voltage Logic and Robust Non‑Volatile Memory

Abstract

We introduce a novel ferroelectric field‑effect transistor (FeFET) that incorporates nanocrystal‑embedded‑insulator (NEI) technology, enabling a remarkably thin unified ferroelectric/dielectric (FE/DE) gate stack. This architecture delivers low‑voltage logic operation and a non‑volatile memory (NVM) window exceeding 1 V, even with a total FE/DE thickness of only 3.6 nm. The ferroelectric behavior of orthorhombic ZrO₂ nanocrystals dispersed within an amorphous Al₂O₃ matrix is confirmed through polarization‑voltage hysteresis, piezoresponse force microscopy, and electrical characterization. We also examine the temperature dependence and endurance of the NEI‑based negative‑capacitance FET (NCFET), demonstrating stable operation across a broad temperature range and robust endurance over 1,000 DC cycles.

Background

FeFETs have emerged as promising candidates for next‑generation integrated circuits due to their inherent negative‑capacitance (NC) effect, which enables sub‑60 mV/decade subthreshold swing (SS) and lower supply voltages. Recent progress has focused on doped HfO₂, offering good CMOS compatibility and thickness scalability. However, further scaling of the ferroelectric layer is limited by leakage currents, which constrain FinFET designs. Inspired by nanocrystal MOS concepts, we embed ferroelectric nanocrystals within a high‑bandgap dielectric to form the NEI FeFET. This design achieves an ultra‑thin FE/DE stack that meets stringent leakage requirements while preserving strong ferroelectric coupling.

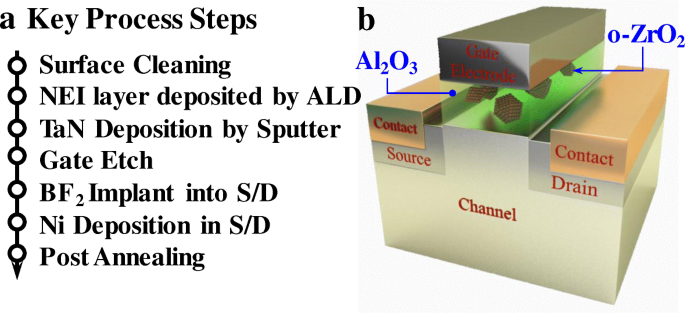

a Key process steps for fabricating the NEI FeFET. b 3‑D schematic of the completed device.

In this work, we report NEI FeFETs, detail the physical properties of the NEI layers at various thicknesses, and evaluate their electrical performance for both low‑voltage logic and NVM applications.

Methods

The fabrication sequence begins with four‑inch n‑type Ge(001) wafers (0.088–0.14 Ω cm). After HF dip cleaning, the wafers are transferred to an ALD chamber where ZrO₂ nanocrystals are incorporated into an amorphous Al₂O₃ matrix, forming the NEI layer. NEI films of 2.1 nm and 3.6 nm thickness are produced. TaN gates are deposited by reactive sputtering, followed by gate patterning, source/drain implantation (BF₂⁺, 20 keV, 1 × 10¹⁵ cm⁻²), Ni contact deposition, and final rapid thermal annealing (RTA). Reference MOSFETs with pure Al₂O₃ gates are also fabricated for comparison.

Figure 1b shows the device cross‑section: the ferroelectric nanocrystals are fully encapsulated within the dielectric, providing both high permittivity (κ) and a large coercive field (E_c). The small volume fraction of ZrO₂ (< 0.5 %) is sufficient to induce ferroelectricity while keeping leakage low.

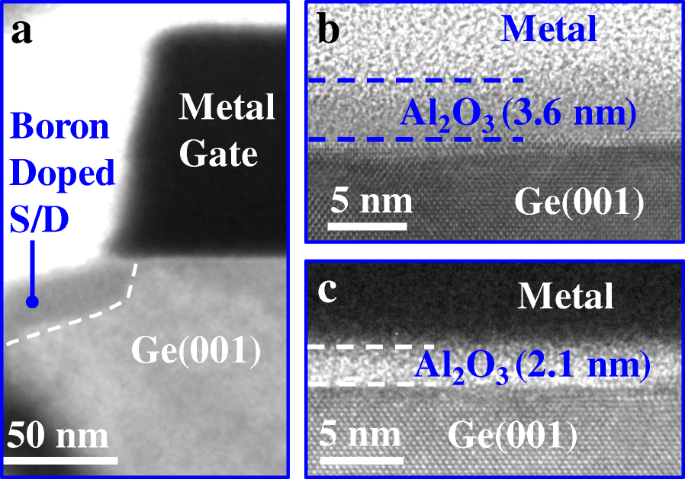

a XTEM image of the NEI‑FeFET stack. b & c Cross‑sectional views for 3.6‑nm and 2.1‑nm NEI layers.

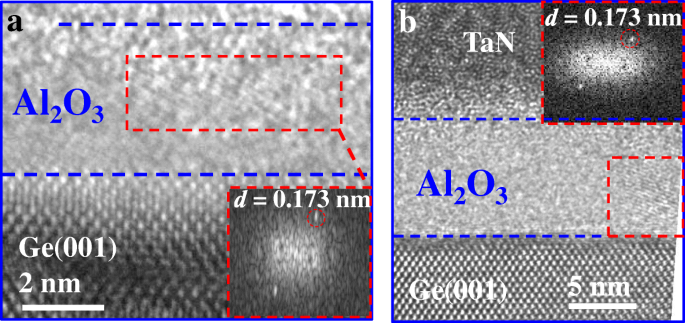

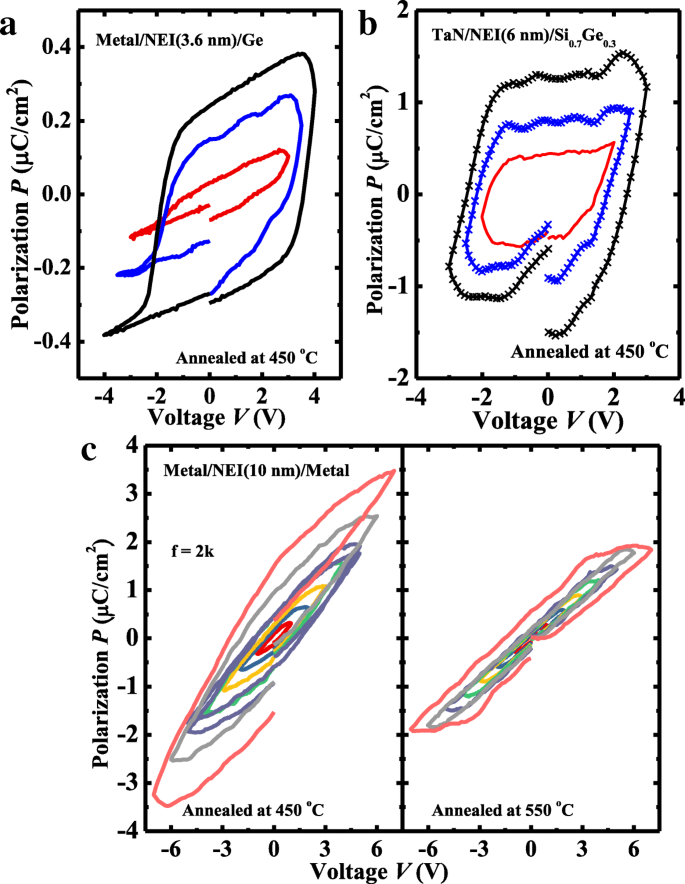

High‑resolution TEM (HRTEM) confirms orthorhombic ZrO₂ (111) nanocrystals with an interplanar spacing of 0.173 nm. Polarization‑voltage (P‑V) measurements and piezoresponse force microscopy (PFM) reveal ferroelectric switching, with remnant polarization (P_r) increasing with film thickness and degrading above 550 °C due to thermal relaxation.

HRTEM images of 3.6‑nm and 6‑nm NEI layers. Inset shows d = 0.173 nm, confirming o‑ZrO₂(111) phase.

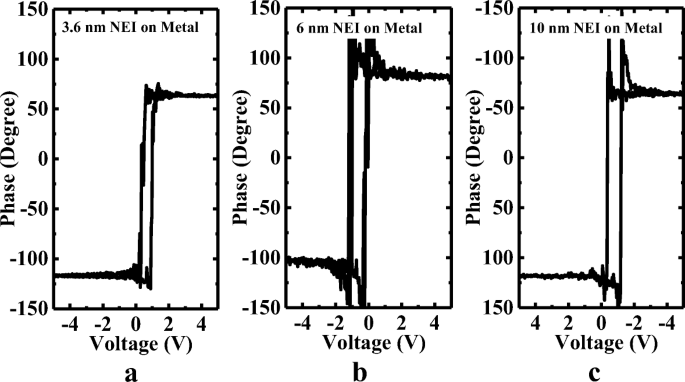

a–c P‑V loops for 3.6‑nm, 6‑nm, and 10‑nm NEI capacitors. The loops are less pronounced for thinner films, and annealing above 550 °C reduces ferroelectricity.

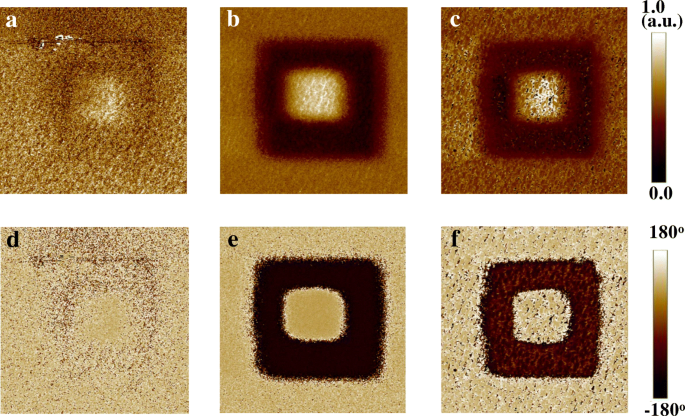

a–c PFM amplitude and phase images for 3.6‑nm, 6‑nm, and 10‑nm NEI films.

a–c Phase‑contrast PFM showing reversible polarization states in the NEI films.

Results and Discussion

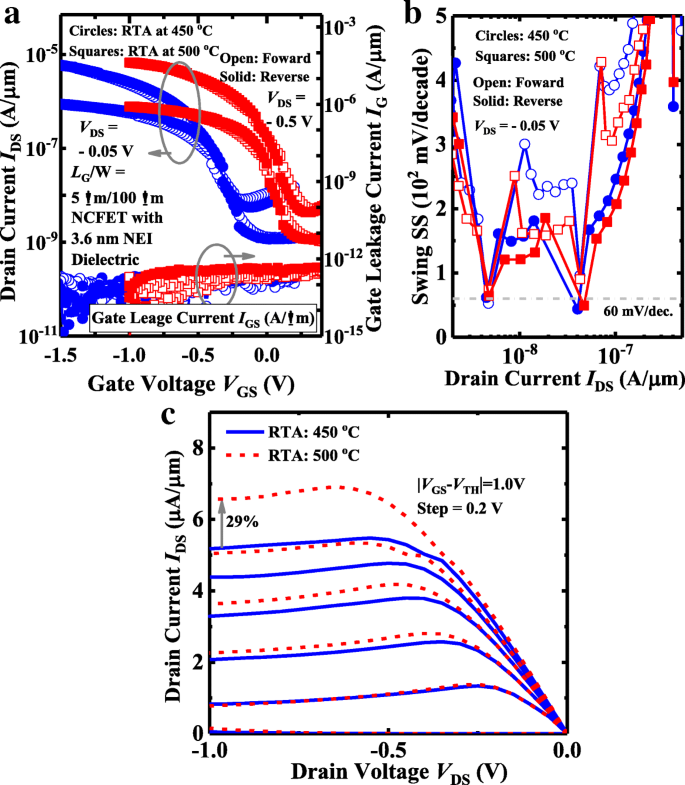

NEI NCFET Performance

Figure 7a presents the I_DS–V_GS characteristics of 3.6‑nm NEI NCFETs annealed at 450 °C and 500 °C. Both devices exhibit minimal hysteresis, confirming a well‑matched ferroelectric and MOS capacitance. The clockwise I‑V loops confirm the negative‑capacitance effect rather than charge trapping. Gate‑leakage remains low, indicating that the embedded nanocrystals do not introduce additional leakage pathways.

a I_DS–V_GS and I_G–V_GS curves for NEI NCFETs at 450 °C and 500 °C. b Sub‑60 mV/decade SS achieved at V_DS = −0.05 V. c I_DS–V_DS traces reveal negative differential resistance (NDR) associated with ferroelectric switching; the 500 °C device shows a 29 % higher I_DS at 1 V versus the 450 °C device.

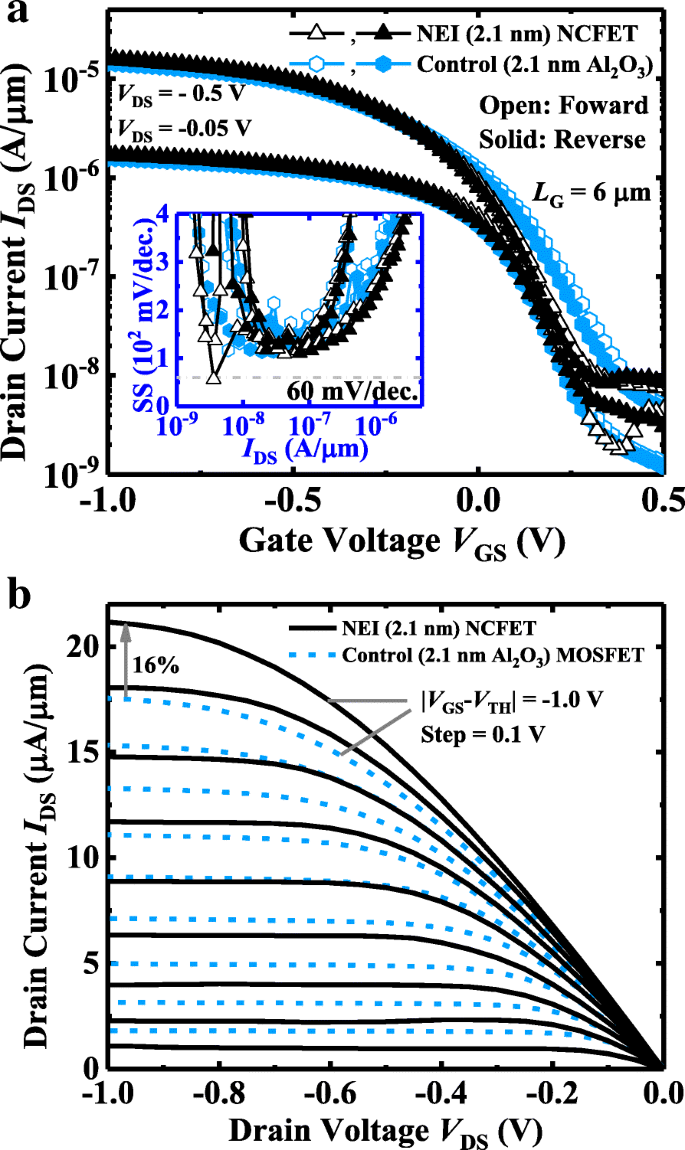

Comparing a 3.6‑nm NEI NCFET with a reference MOSFET of identical gate insulator thickness (2.1 nm), the NCFET demonstrates a sharper SS and a 16 % higher I_DS at V_DS = 1 V. The NDR effect is more pronounced in the thicker 3.6‑nm device, consistent with the stronger ferroelectric coupling.

a I_DS–V_GS curves for a 2.1‑nm NEI NCFET and a pure Al₂O₃ MOSFET. Inset shows steeper SS up to threshold. b I_DS–V_DS traces highlighting NDR in the NCFET; the 2.1‑nm device improves I_DS by 16 % compared to the MOSFET.

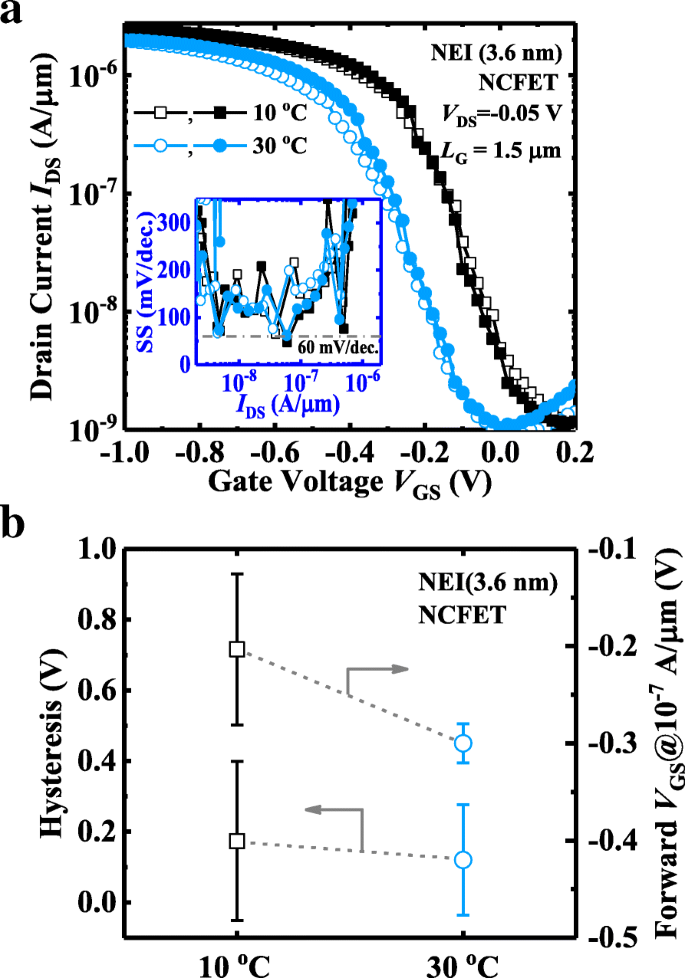

Temperature‑dependent tests (10 °C–30 °C) reveal that the NCFET’s SS remains unchanged, while the I_DS–V_GS curve shifts to more negative gate voltages with rising temperature—a signature of enhanced ferroelectric activity. Forward V_GS also moves negative with temperature, likely reflecting an increase in E_c.

a I_DS–V_GS curves at 10 °C and 30 °C, with inset showing SS peak. b Statistics of hysteresis and forward V_GS at I_DS = 10⁻⁷ A/μm, illustrating the negative shift with temperature.

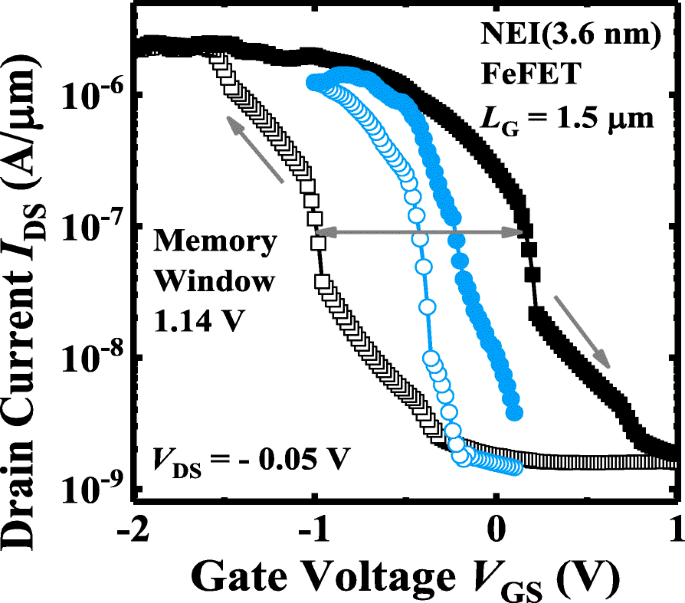

NEI FeFET as Non‑Volatile Memory

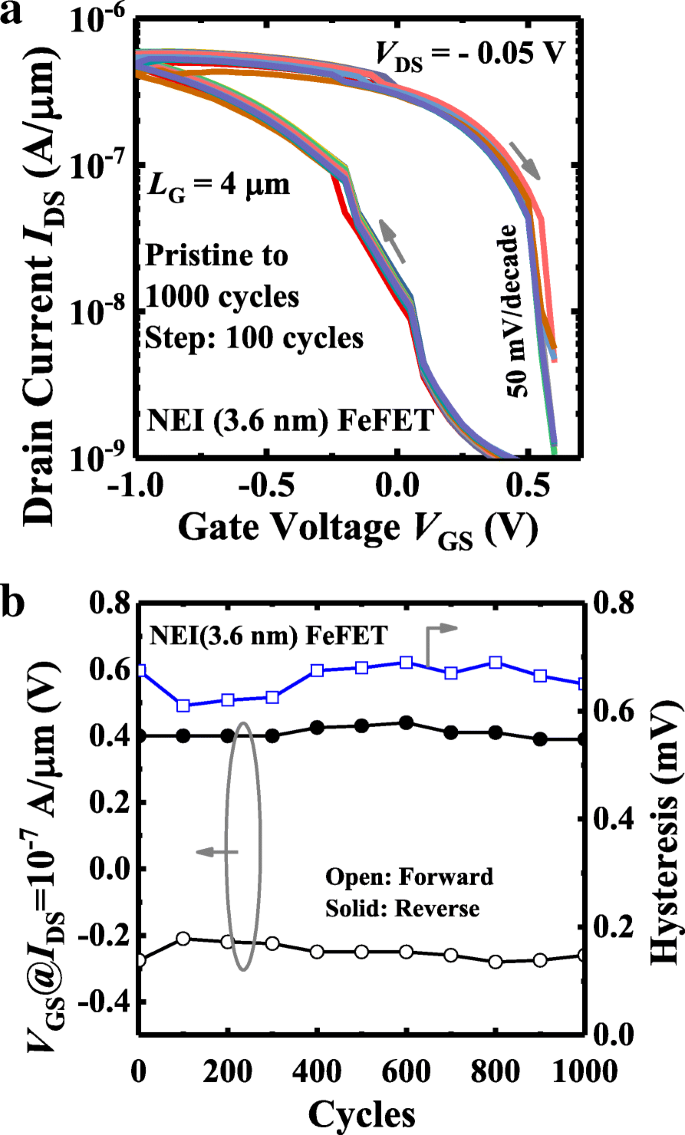

Extending the V_GS sweep range increases the memory window (MW). A 3.6‑nm NEI FeFET delivers a MW of 1.14 V when sweeping between +1 V and –2 V, a substantial improvement over the 0.2 V window at a ±0.1 V sweep. Endurance tests over 1,000 DC cycles show a stable hysteresis window of ~0.65 V, underscoring the reliability of the ferroelectric layer.

Large MW (1.14 V) observed for a 3.6‑nm NEI FeFET under a ±1 V/–2 V sweep.

a I_DS–V_GS curves after 1,000 DC sweeps. b Endurance plot showing a stable MW throughout the cycle count.

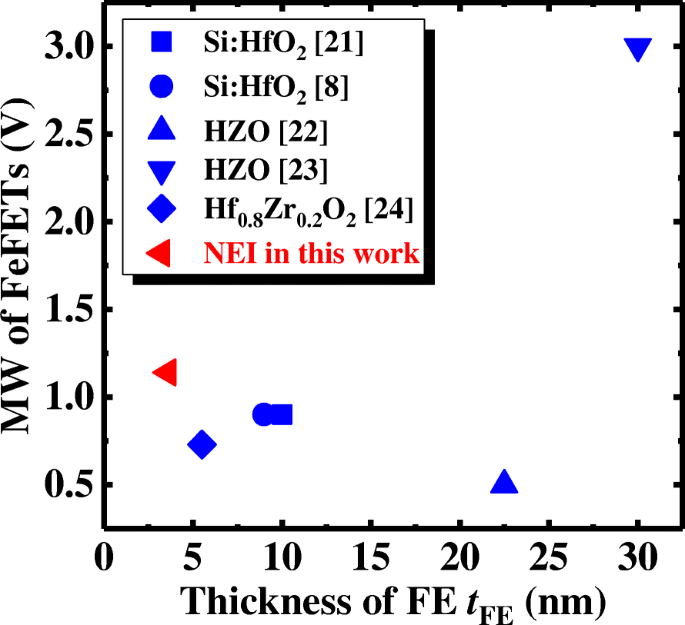

Benchmarking against published FeFETs (MW vs. FE thickness) demonstrates that the NEI device achieves a >1 V window with the thinnest reported ferroelectric layer (3.6 nm). This superior performance likely arises from the stable orthorhombic phase in the nanocrystals, which remains robust at reduced thicknesses.

Comparison of MW and FE thickness across reported FeFETs; the NEI device sets a new record with the thinnest FE layer.

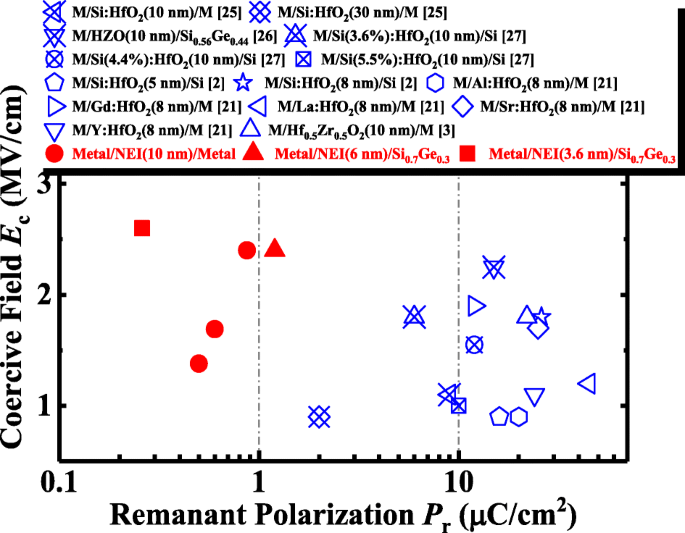

Finally, the NEI architecture offers tunability: P_r can be adjusted by varying the nanocrystal volume, while κ can be enhanced by incorporating high‑κ elements into the amorphous matrix (e.g., LaAlO₃). Compared with doped HfO₂, NEI achieves comparable coercive fields with markedly lower remnant polarization, mitigating depolarization losses and improving retention.

Benchmark of NEI versus doped HfO₂ films: NEI shows lower P_r while maintaining similar E_c.

Conclusions

We have demonstrated that embedding sub‑nanometer ZrO₂ nanocrystals within an amorphous Al₂O₃ matrix yields a ferroelectric gate stack that supports both negative‑capacitance logic and stable non‑volatile memory. The 3.6‑nm NEI FeFET delivers a memory window exceeding 1 V and maintains robust NC behavior over a wide temperature range. The architecture’s scalability and low leakage make it a promising path toward fully CMOS‑compatible FinFETs with ultra‑thin ferroelectric layers.

Nanomaterials

- Fluorescent Nanomaterials: Advances, Synthesis, and Biomedical Applications

- Harnessing Atomic Layer Deposition for Next‑Generation Micro‑LEDs and VCSELs

- Graphene‑Polymer Composites for High‑Performance Supercapacitors: A Comprehensive Review

- Dual Functionality of V/SiOx/AlOy/p++Si Devices: Selector and Memory Switching Controlled by Compliance Current

- Impact of Etching Parameters on Ge/Si FinFET Channel Fabrication and Device Performance

- Biomedical Applications of Gold Nanoclusters: Recent Advances and Future Directions

- Large-Scale Dendritic Silver Nanostructures: Controlled Morphology for Enhanced Catalysis and SERS Performance

- Hydrothermal Phosphorus‑Doped ZnO Nanorods: Structural, Electrical, and Optical Characterization for Optoelectronic Devices

- Magnetic Core‑Shell Nanoparticles: Advancing Targeted Drug Delivery, Imaging, and Antimicrobial Therapies

- Advances in Carbon Nanotube Assembly and Integration for Next‑Generation Applications