Sub‑10 nm InSe Field‑Effect Transistors Enabled by Novel Sandwiched Indium Ohmic Contacts: A Theoretical Study

Abstract

Two‑dimensional indium selenide (InSe) has emerged as a promising channel material for future CMOS nodes, offering carrier mobilities around 2 000 cm2/V·s and on/off ratios exceeding 108 in experimental devices. Theoretical work has predicted that InSe field‑effect transistors (FETs) can maintain high performance down to sub‑10 nm gate lengths in the ballistic limit, yet achieving low‑resistance ohmic contacts remains the primary bottleneck. Here we introduce a novel sandwiched indium contact architecture—indium/ InSe / indium—that simultaneously eliminates the tunneling barrier, suppresses the Schottky barrier, and provides effective n‑type doping. First‑principles calculations show that the contact resistance drops to 0.032 ± 0.002 Ω·mm, a reduction of more than 50 % relative to conventional top contacts. Device simulations for gate lengths of 7, 5 and 3 nm demonstrate that the sandwiched contacts boost the drive current by 69.4 %, 50 % and 49 % respectively, while reducing the intrinsic delay by 20.4 %, 16.7 % and 18.9 %. Energy‑delay product (EDP) benchmarks reveal that InSe FETs with sandwiched contacts outperform MoS2 devices and meet the International Technology Roadmap for Semiconductors (ITRS) 2024 specifications, approaching the upper limit of ideal black‑phosphorus FETs. These findings establish the sandwiched structure as a compelling route to high‑performance InSe transistors in the next generation of logic technology.

Introduction

Two‑dimensional (2D) semiconductors are attracting intense interest for next‑generation complementary metal‑oxide‑semiconductor (CMOS) devices due to their atomically thin body, excellent electrostatic control, and superior carrier mobilities compared to bulk counterparts. Besides graphene, the family of 2D materials—including transition‑metal dichalcogenides (TMDs), black phosphorus (BP), and indium selenide (InSe)—offer band gaps that enable high on/off ratios in field‑effect transistors (FETs). TMD‑based FETs exhibit on/off ratios as high as 108 thanks to their heavy effective mass, while BP devices benefit from mobilities near 1 000 cm2/V·s and pronounced anisotropy. InSe has recently been shown to achieve mobilities up to 2 000 cm2/V·s at room temperature and on/off ratios above 108, making it a strong candidate for sub‑10 nm scaling. However, realizing the theoretical potential of InSe FETs is hindered by the lack of reliable doping methods and high‑quality ohmic contacts. Most 2D‑based devices operate as Schottky‑barrier FETs (SBFETs), where the metal/semiconductor interface imposes a significant contact resistance and limits current density. Achieving low‑resistance, heavily doped contacts is therefore a central challenge for high‑performance 2D transistors. To address this bottleneck, we propose a novel sandwiched ohmic contact geometry that employs indium electrodes on both sides of the InSe channel. Recent experimental and theoretical studies have identified indium as a promising metal for InSe, providing good band alignment and strong orbital overlap. In this work, we systematically evaluate the electronic structure and contact resistance of the sandwiched design using first‑principles calculations, and benchmark the resulting transistor performance (gate lengths 7, 5, and 3 nm) against ITRS 2013/IRDS 2024 specifications and other state‑of‑the‑art 2D FETs.

Methods

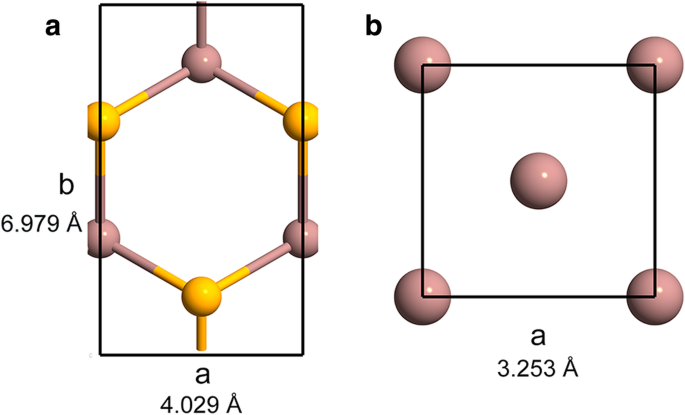

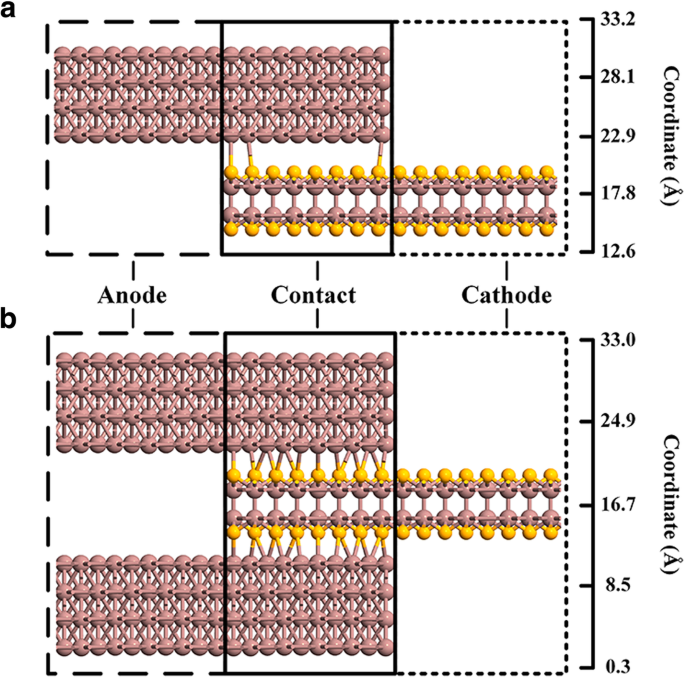

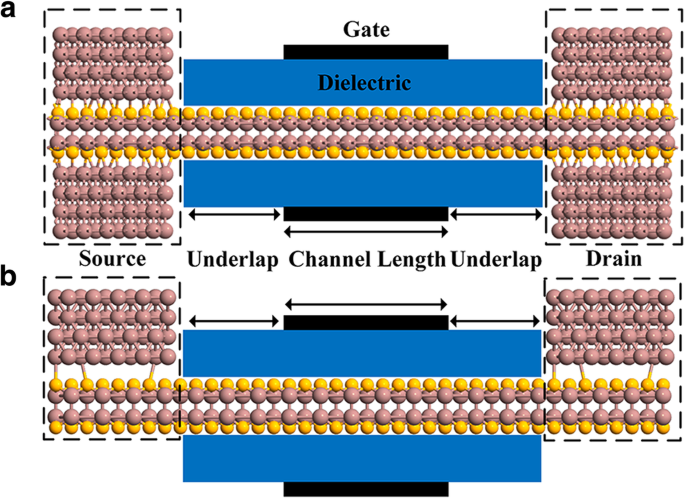

All atomic structures were optimized with the Vienna Ab‑Initio Simulation Package (VASP) using a plane‑wave cutoff of 335 eV. The InSe lattice constant converged to 4.029 Å, in excellent agreement with experiment. Indium metal parameters were taken from the CRC Handbook. The initial indium/InSe interface was constructed using 4×1×1 InSe and 5×2×1 indium (001) slabs, yielding an average strain of 1.32 %. Both the top‑contacted and sandwiched geometries were relaxed with the optB88 van der Waals functional, achieving forces below 0.02 eV/Å. The contact area for the two‑probe calculations was 16.19 Å × 6.41 Å. To extract contact resistance, we employed a two‑probe model in which the InSe channel under the contact was heavily doped (1×1014 e/cm2) to suppress extrinsic series resistance. The current–voltage characteristics were calculated using the Landauer–Büttiker formalism. Device simulations were carried out with the Non‑Equilibrium Green’s Function (NEGF) formalism in QuantumATK. The channel, source, and drain were constructed along the transport direction, with a 1 nm gate underlap for the 3 nm gate length device to mitigate band‑to‑band tunneling. A double‑zeta polarized basis set and a 90 Rydberg energy cutoff were used, and the Brillouin zone was sampled with an 8/Å−1 × 11/Å−1 × 180/Å−1 k‑point grid. All calculations were fully self‑consistent.

Top view of unit cells for InSe (a) and indium (b).

Atomic structures of top (a) and sandwiched (b) contacts used in the two‑probe contact‑resistance calculation. The coordinates indicate out‑of‑plane positions.

Device geometries for InSe FETs with sandwiched (a) and top (b) contacts. All nodes follow ITRS/IRDS nomenclature. Device parameters are listed in Table 1.

Intrinsic delay (τ) was calculated as τ = (QON − QOFF)/ION, with QON and QOFF extracted from the capacitance–voltage characteristics at |VDS| = 0.68 V (2019 nm), 0.64 V (2021 nm), and 0.64 V (2024 nm). The power‑delay product (PDP) was defined as PDP = (QON − QOFF) VDS.

Results and discussion

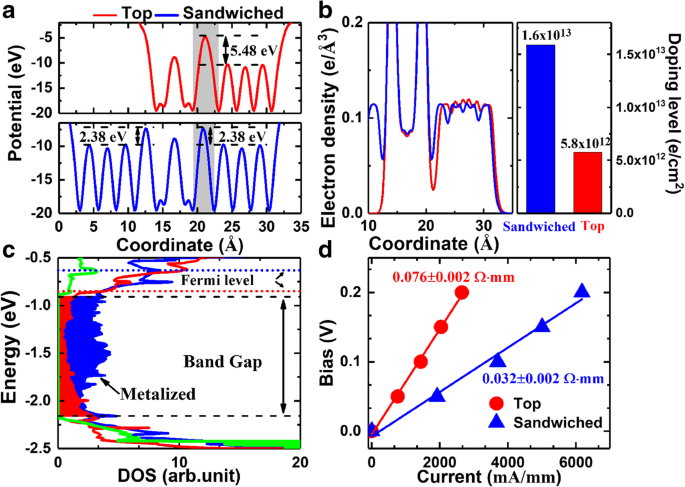

Three key factors determine the quality of ohmic contacts in 2D materials: the tunneling barrier, the Schottky‑barrier (SB) height, and the interfacial orbital overlap. Figure 4a shows that the sandwiched contact reduces the effective tunneling barrier from 5.48 eV (top contact) to 2.38 eV—a 56.6 % reduction—while also shortening the van der Waals gap by 0.66 Å. The enhanced orbital overlap is evident in the plane‑averaged charge density (Fig. 4b), where the sandwiched structure delivers a higher electron density at the interface. Mulliken population analysis yields an n‑type doping level of 1.6 × 1013 e/cm2 for the sandwiched contact, nearly 2.8 times that of the top contact, approaching the heavy doping levels used in 2D tunneling FET simulations.

The density of states (DOS) plots (Fig. 4c) reveal that the indium–InSe interaction metallizes the InSe band gap in both contact schemes, but the sandwiched contact achieves a larger metal‑induced gap state density. Consequently, the Fermi level pinning lies 0.07 eV (top) and 0.27 eV (sandwiched) above the conduction‑band minimum, effectively eliminating the SB.

Contact resistance extracted from the two‑probe simulations (Fig. 4d) shows a linear I–V characteristic for both contact types, confirming ohmic behavior. The sandwiched design yields a resistance of 0.032 ± 0.002 Ω·mm—over 50 % lower than the top contact—highlighting the advantage of doubling the contact area.

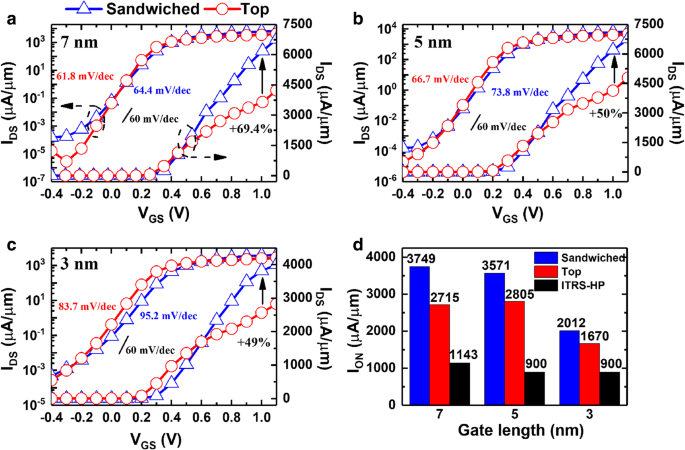

Device performance metrics are presented in Figure 5. The subthreshold swing (SS) remains below 100 mV/dec for all nodes, with the 2019 nm device achieving 61.8 mV/dec (top) and 64.4 mV/dec (sandwiched). The sandwiched contacts increase the drain‑current (IDS) by 69.4 % (2019 nm), 50 % (2021 nm), and 49 % (2024 nm) compared to their top‑contacted counterparts. The on‑state current (ION) surpasses the ITRS high‑performance (HP) requirement in all nodes, with additional gains of 38.2 % (2019 nm), 27.3 % (2021 nm), and 20.5 % (2024 nm) for the sandwiched devices.

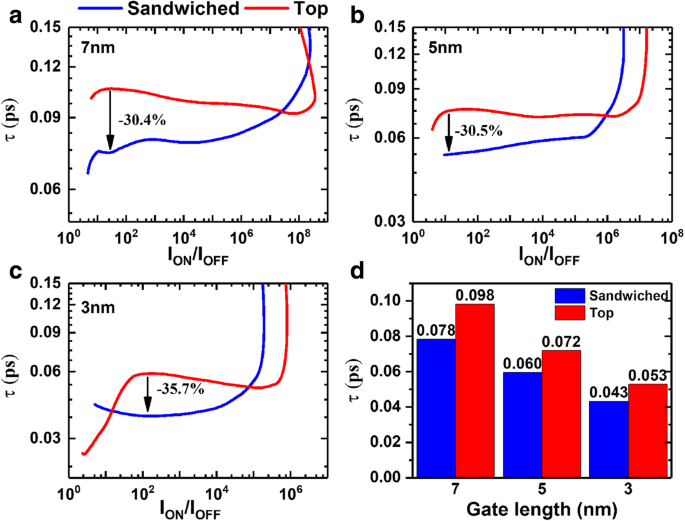

Intrinsic delay (τ) is plotted against the on/off ratio in Figure 6. All devices exhibit τ < 0.15 ps, well below the ITRS 2013 target of 0.44–0.46 ps. The sandwiched contacts reduce τ by 20.4 % (2019 nm), 16.7 % (2021 nm), and 18.9 % (2024 nm) at high on/off ratios. These improvements translate to faster switching speeds without sacrificing current drive.

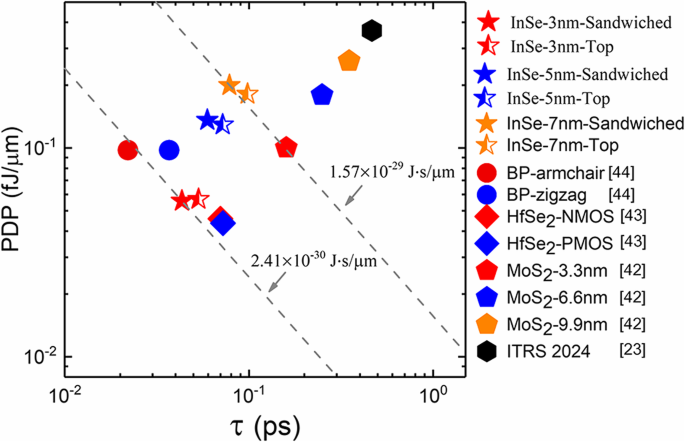

Finally, the energy‑delay product (EDP) is benchmarked in Figure 7 against other 2D FETs that meet experimental validation. All InSe devices with sandwiched contacts fall below the ITRS 2024 EDP requirement, outperforming MoS2 FETs and approaching the performance ceiling of BP FETs. The best EDP occurs for the 3 nm gate device (2024 nm node), underscoring the scalability advantage of the sandwiched architecture.

Collectively, these results demonstrate that the sandwiched indium contact not only mitigates the key obstacles to high‑performance InSe transistors—tunneling barrier, SB, and doping—but also delivers device metrics that exceed industry road‑map targets and rival the best 2D FETs.

Key figures for contact analysis: (a) effective potential, (b) plane‑averaged charge density and doping level, (c) density of states, (d) two‑probe I–V characteristics for top (red) and sandwiched (blue) contacts. Transfer characteristics of InSe FETs at 2019 (a), 2021 (b), and 2024 (c) nm nodes, and comparison of ION against the ITRS HP requirement (d). Intrinsic delay as a function of on/off ratio at 2019 (a), 2021 (b), and 2024 (c) nm nodes, and comparison with the ITRS HP requirement (d). Energy‑delay product (EDP) versus intrinsic delay for InSe FETs and selected 2D FETs. The gray dashed lines indicate ITRS 2024 EDP targets.

Conclusions

We have introduced a sandwiched indium ohmic contact for InSe FETs that effectively eliminates the tunneling barrier, removes the Schottky barrier, and induces substantial n‑type doping. The contact resistance is reduced to 0.032 ± 0.002 Ω·mm, a > 50 % improvement over conventional top contacts. Device simulations at 7, 5, and 3 nm gate lengths demonstrate universal performance gains: on‑state current increases by 20.5–38.2 % and intrinsic delay decreases by 16.7–20.4 % relative to the ITRS HP benchmarks. Energy‑delay product analysis shows that the sandwiched devices surpass MoS2 FETs and meet the 2024 ITRS requirements, approaching the theoretical limit of BP FETs. These results establish the sandwiched architecture as a viable path toward high‑performance InSe transistors for next‑generation CMOS technology.

Availability of data and materials

The datasets used in this study are available from the corresponding author upon reasonable request.

Abbreviations

- 2D

Two‑dimensional

- CMOS

Complementary metal‑oxide‑semiconductor

- TMDs

Transition metal dichalcogenides

- BP

Black phosphorus

- InSe

Indium selenide

- FET

Field‑effect transistor

- SB

Schottky barrier

- 2D FET

2D‑material‑based FET

- ITRS

International Technology Roadmap for Semiconductors

- vdW

van der Waals

- UL

Underlap

- NEGF

Non‑equilibrium Green’s function

- DOS

Density of states

- SS

Subthreshold swing

- HP

High performance

- τ

Intrinsic delay

- PDP

Power‑delay product

- EDP

Energy‑delay product

Nanomaterials

- High‑Performance SnSe Nanoflake Field‑Effect Transistors Featuring Low‑Resistance Gold Ohmic Contacts

- Mesoporous 2‑D VO₂ Microarrays Deliver 265 F/g Capacitance, 66 % Retention at 10 A/g, and 3000‑Cycle Stability for High‑Performance Supercapacitors

- Cost‑Effective PDMS Nanocone Cluster for Ultra‑Low Solar‑Cell Reflectance and Superhydrophobic Self‑Cleaning

- Room‑Temperature ALD Al₂O₃ Enables Ultra‑Low‑Thermal‑Budget, High‑Mobility a‑IGZO Thin‑Film Transistors

- Comparative Analysis of Negative‑Capacitance FETs Across MOS Capacitances

- Penta‑Siligraphene: A Thermally Stable, High‑Capacity Anode for Li‑Ion Batteries – A First‑Principles Study

- High-Performance Supercapacitor Electrodes from Hierarchically Porous Carbon Derived from Lignosulfonate Biowaste

- Step-Thickness Design Boosts DG TFET Efficiency: A Simulation Study

- Enhancing 2D Perovskite Solar Cell Performance Through Water-Assisted Crystallization

- Engineered Nickel‑Cobalt Layered Double Hydroxides: Tunable Thin‑Layer Nanosheets for Superior Supercapacitor Performance