Interrupts Explained: Types, Mechanisms, and Applications in Modern Computing

Modern PCs rely on interrupt requests to coordinate hardware functions. The concept dates back to the UNIVAC 1103 in 1953, with the IBM 650 introducing interrupt masking in 1954. Assigning distinct IRQ lines to individual devices is essential for efficient operation. When peripherals such as keyboards or mice need CPU attention, they generate interrupts that trigger the corresponding Interrupt Service Routine (ISR). ISRs are indispensable for time‑sensitive tasks, data transfers, error handling, watchdog timers, and traps.

What is an Interrupt?

Definition: An interrupt is an input signal that demands the processor’s immediate attention, having the highest priority among hardware and software events. In early computing, processors had to poll every peripheral and program for signals, wasting clock cycles and degrading performance. The interrupt mechanism inverted this model: a peripheral or software module signals the CPU, which suspends its current task, saves its state, and executes the appropriate ISR. After the ISR completes, the CPU restores its previous state and continues execution.

Types of Interrupt

Interrupts are broadly classified into two categories.

Hardware Interrupts

These are electronic signals sent from external devices to the CPU, indicating that they require immediate service. Keyboard keystrokes, mouse movements, and sensor alerts are typical examples. Hardware interrupts are asynchronous, arriving at any point during instruction execution.

Hardware interrupts are further subdivided:

- Maskable Interrupts – The processor’s interrupt mask register controls whether a particular interrupt source is enabled or disabled. Each bit in the register corresponds to a specific IRQ line; a set bit allows the interrupt to be serviced, while a cleared bit blocks it.

- Non‑Maskable Interrupts (NMI) – NMIs have the highest priority and cannot be disabled by the processor. They are typically used for critical events such as watchdog timer expirations or hardware failures.

Software Interrupts

The CPU itself can generate an interrupt by executing a special instruction or when an exceptional condition arises during program execution. Software interrupts enable system calls, exception handling, and trap routines.

Triggering Methods

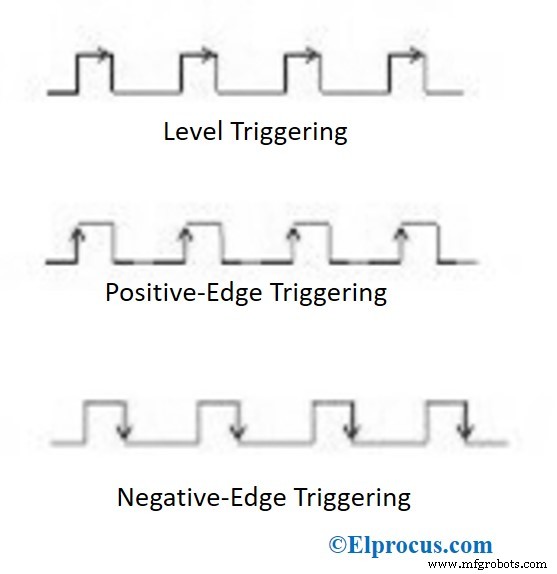

Interrupt lines can be triggered by a logic level or a signal edge. These two approaches differ in how the source signals the CPU.

Level‑Triggered Interrupt

In this mode, the interrupt line remains asserted as long as the source requires service. If the source stays active while the ISR is running, the CPU re‑invokes the handler after completion. Level‑triggered inputs can be problematic if the signal remains asserted for an extended period.

Edge‑Triggered Interrupt

An edge‑triggered interrupt fires immediately when the signal transitions from low to high or high to low. The CPU does not depend on the signal’s level, only on the transition, making this mode suitable for fast, one‑shot events.

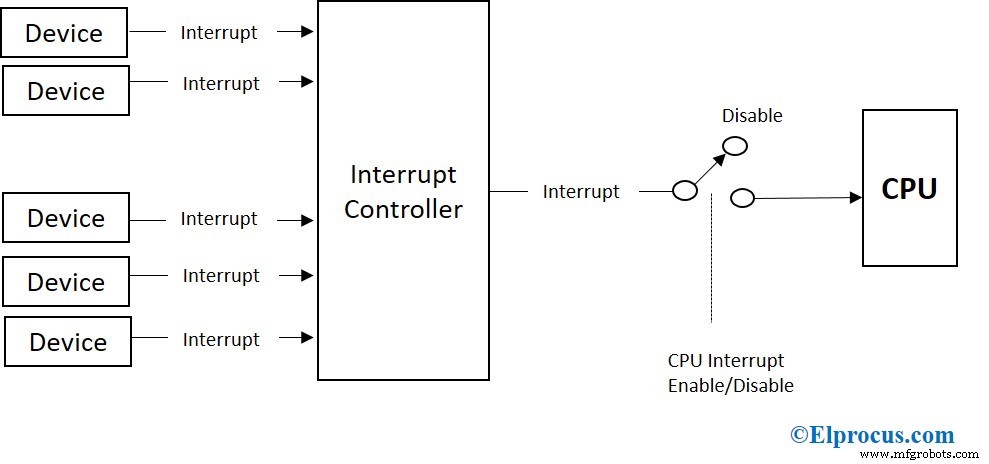

System Implementation

Interrupts are wired into the hardware as dedicated control lines or embedded within memory subsystems. When implemented via a Programmable Interrupt Controller (PIC), multiple sources share a single CPU pin, simplifying wiring and enabling priority arbitration.

Shared Interrupt Requests (IRQs)

With edge‑triggered interrupts, a pull‑up or pull‑down resistor maintains the line in a known state. Each device’s pulse propagates along the shared line, and the CPU samples the line on the trailing edge to ensure no pulse is missed. Older ISA boards relied on shared IRQs, which could cause contention; modern PCI architectures mitigate this through dedicated controllers and dynamic allocation.

Hybrid

Hybrid systems combine edge‑triggering with level verification, ensuring that an active signal is not ignored. This approach is common for non‑maskable inputs, reducing false positives.

Message‑Signaled Interrupt

Instead of a dedicated line, the device sends a message over a bus such as PCI Express to notify the CPU. This eliminates physical pins and supports higher throughput.

Doorbell

A doorbell interrupt is a software‑driven signal where the device writes data to a shared memory region and then triggers the interrupt, allowing the CPU to process the ready data.

Multiprocessor IPI

In multi‑core systems, one processor can send an inter‑processor interrupt (IPI) to another, coordinating tasks or signaling events across cores.

Typical Uses/Applications

- Handling hardware timers and processing keyboard/mouse input.

- Responding to time‑sensitive or real‑time events.

- Managing data transfer to and from peripheral devices.

- Handling high‑priority signals such as power‑down requests, traps, and watchdog timers.

- Reporting abnormal CPU events.

- Facilitating orderly power‑off when external power is lost.

- Generating periodic interrupts for absolute timekeeping.

FAQs

1. Why are interrupts used?

Interrupts bring the CPU’s focus to urgent hardware or software tasks, enabling timely responses without constant polling.

2. What is NMI?

NMI stands for Non‑Maskable Interrupt, a signal that cannot be disabled by the processor and is reserved for critical events.

3. What is the function of the interrupt acknowledge line?

It signals to the device that the CPU is ready to receive an interrupt, allowing the device to place the ISR address on the bus.

4. Describe a hardware interrupt. Give examples.

Hardware interrupts are generated by external devices—keyboard presses, mouse clicks, or sensor outputs—that require immediate CPU service.

5. Describe a software interrupt.

Software interrupts are invoked by the processor through special instructions, such as system calls or exception handling routines.

6. Which interrupt has the highest priority?

- Non‑maskable interrupts (NMIs) and traps have the highest priority.

7. Give some uses of interrupts.

- Rapid response to real‑time events.

- Data transfer with peripheral devices.

- Handling critical tasks such as power‑down and watchdog timers.

- Reporting abnormal CPU events.

8. What is a hybrid type of system implementation?

A hybrid system uses both edge‑triggered and level‑verified signaling, ensuring that genuine events are captured while reducing spurious triggers.

This article explores interrupts’ significance, detailing their types, system integration, and practical applications.

Embedded

- How Distance Sensors Work and Their Key Applications

- Understanding the AD8232 ECG Sensor: Functionality and Applications

- Embedded Systems: Definition, Architecture, and Real‑World Applications

- What Is Destructive Testing and Its Critical Applications

- 3D Printing Explained: Types, Processes, and How It Works

- Honing: Process, Parameters, Types, and Key Advantages for Superior Surface Finish

- Reamer Tools: Types, Terminology, and Practical Uses

- Understanding Casting Patterns: Types, Benefits, and Color Schemes

- Understanding PID Controllers: Types, Operation, and Industrial Applications

- Gas Welding Techniques and Their Industrial Applications