XMOS Launches Xcore.ai: Low‑Cost Crossover Processor Empowering Edge AI Inference

BRISTOL, UK — XMOS has re‑engineered its Xcore processor core for machine learning, launching the Xcore.ai, a crossover processor designed for AIoT devices. Priced from just $1, the chip promises high‑performance inference in a compact, low‑power package.

Xcore.ai represents the third generation of XMOS products built on its proprietary Xcore architecture. It is engineered for real‑time AI inference and decision‑making on edge devices, while also handling signal processing, control, and communications tasks.

Unlike previous iterations, the third‑generation chip incorporates a vector pipeline that supports machine‑learning workloads. It is the sole crossover processor of its kind to natively run binarized (1‑bit) neural networks—an emerging technology that offers order‑of‑magnitude gains in performance and memory density for ultra‑low‑power edge AI, at a modest trade‑off in accuracy. Xcore.ai also accommodates 32‑bit, 16‑bit and 8‑bit data types.

The Xcore.ai joins a new class of AI‑capable system‑on‑chips for endpoint applications, the crossover processor (Image: XMOS)

Xcore.ai is part of an emerging class of endpoint processors with AI capability, known as crossover processors. Coined by NXP, the term describes devices that blend the performance of an application processor with the low‑power, real‑time operation of a microcontroller.

“Customers often view microcontrollers as Cortex‑M0, M3 or M4 chips that cost under 75 ¢ and deliver roughly 100 MIPS. SoCs, on the other hand, may feature quad‑A53 cores running at a gigahertz. There is a significant gap between these extremes—particularly for voice‑centric workloads that demand thousands of MIPS. This middle tier deserves its own name,” said Mark Lippett, XMOS CEO, in an exclusive interview with EETimes.

Voice InterfacesXMOS’s second‑generation XVF3510, launched in July 2019, is an ASIC for voice interfaces built on the same Xcore design. Reference solutions based on the XVF3510 are already qualified for Amazon’s Alexa Voice Service.

Given XMOS’s track record in voice, the Xcore.ai chip will initially target voice‑interface applications that require AI for keyword spotting or dynamic dictionary functions.

“Voice remains the most critical AI workload at the edge, and that will likely stay true for years to come,” Lippett said. “To enhance voice experiences, devices will become increasingly multimodal, integrating additional sensors to provide context—such as detecting a person’s presence or the direction of their speech.”

Mark Lippett (Image: XMOS)

“There are many opportunities to improve user experience by listening beyond audio and leveraging multimodal data,” he added.

Privacy, security and safety requirements often dictate that processing be performed on the endpoint. Lippett illustrated this with appliances that use voice and radar to disable an oven when only children are present in the kitchen.

To support rapid development, Xcore.ai will ship with libraries for voice‑interface creation, while offering the flexibility for customers to design custom solutions. A MIPI interface is also available for camera input.

Xcore ArchitectureThe Xcore.ai chip delivers up to 3,200 MIPS, 51.2 GMACCs and 1,600 MFLOPS. It includes 1 MB of embedded SRAM and a low‑power DDR interface for expansion.

Against a comparable Cortex‑M7 device operating at a similar frequency, XMOS claims that Xcore.ai delivers 32× the AI performance and 15× the DSP performance.

“In the endpoint market, price‑performance is paramount,” Lippett emphasized. “We’ve aggressively priced Xcore.ai at $1 in volume. Roughly half the cost of a comparable Cortex‑M7, it offers a dramatic performance advantage.”

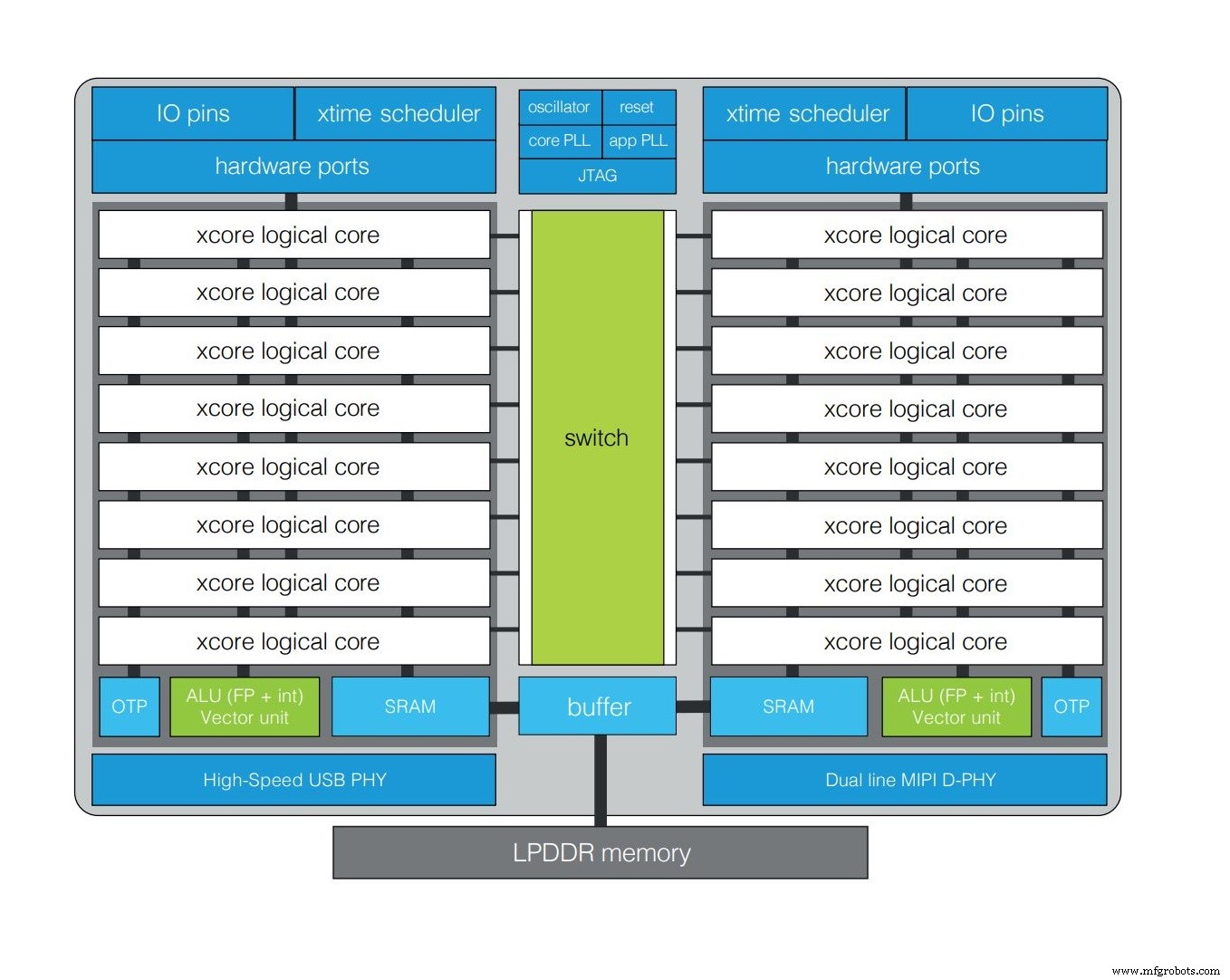

The Xcore is based on logical cores arranged in tiles with memory, ALUs and vector units (Image: XMOS)

Xcore.ai is built on XMOS’s proprietary Xcore architecture. The core comprises logical cores that can be assigned to I/O, DSP, control or AI functions. Each tile contains eight logical cores, two tiles per chip, and shared memory, ALUs and a vector unit.

“What sets Xcore apart is the predictable sharing of resources,” Lippett explained. “The architecture is multi‑core not just to accelerate workloads, but to allocate dedicated resources to critical functions, ensuring deterministic timing.”

Mapping distinct functions to logical cores in firmware enables a “virtual SoC” that is fully software‑defined. For example, one core can handle I²S, I²C and LED drivers, while others process neural networks and perform traditional software tasks. This software‑centric approach speeds development, meets the dynamic demands of IoT, and reduces cost—enabling economical solutions even in niche markets.

An example application mapped onto an Xcore.ai device (Image: XMOS)

“The market is demanding a broader range of features, and companies need to respond swiftly,” Lippett said. “Building a generic platform that may not fit any segment is risky. With Xcore.ai, manufacturers can quickly launch devices with lower CAPEX and place smaller, more targeted bets.”

How will XMOS compete against major microcontroller makers entering the crossover processor space?

“We won’t replicate ARM‑based SoCs,” Lippett said. “The only way to compete is through architectural advantage—performance and flexibility inherent to the Xcore.”

Embedded

- STPMIC1: All‑in‑One Power‑Management for STM32MP1 Processor Systems

- Boreas Launches BOS1901CW: Ultra‑Compact, Low‑Power Haptic IC for Wearables

- AImotive Launches aiWare3P Neural Network Accelerator for High-Performance Automotive Vision

- GreenWaves Unveils GAP9: Ultra‑Low‑Power AI Accelerator Achieves 50 mW Power with 50 GOPS Performance

- NXP Launches i.MX 8M Plus: A Multicore Edge Processor with Built‑In Neural Processing Unit

- ROHM Launches BD71850MWV PMIC for NXP i.MX 8M Nano Processors

- Edge AI Acceleration: Leading Specialized Processors for 2024

- iCOMOX Open‑Source Platform Drives Predictive Maintenance in Industry 4.0

- Lattice & Etron Unveil Compact, Low‑Power Memory Controller for Edge AI Workloads

- Python Overview: High-Level, Readable, Interactive & Object-Oriented