Leveraging the LPC55S69 PowerQuad Engine for Efficient FFT Computation

Leveraging the LPC55S69 PowerQuad Engine for Efficient FFT Computation

The NXP LPC55S69 microcontroller is engineered for high‑performance signal processing. Its PowerQuad coprocessor houses two specialized engines: the Biquad filter and the Transform Engine. While the Biquad handles time‑domain filtering, the Transform Engine executes Fast Fourier Transforms (FFT) with minimal CPU involvement, freeing the Cortex‑M33 cores for other tasks.

Understanding Discrete Fourier Transforms

Signals captured in the time domain are often best interpreted in the frequency domain. The Discrete Fourier Transform (DFT) quantifies how a sampled signal aligns with a set of sine and cosine basis functions of varying frequencies.

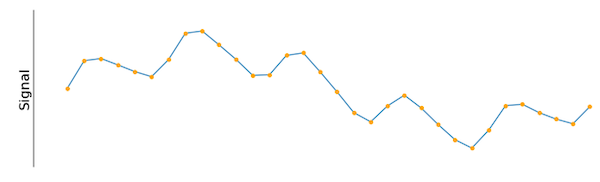

Consider a sampled input signal displayed in Figure 1:

Illustrating Correlation with a Reference Cosine

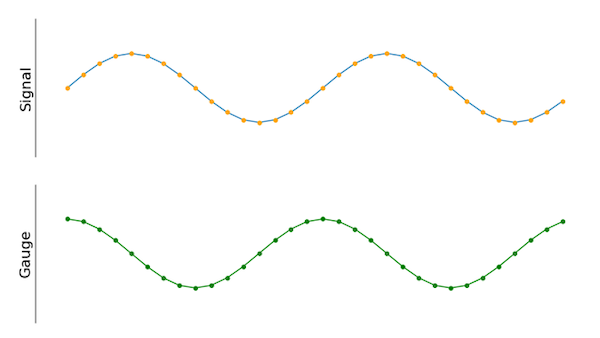

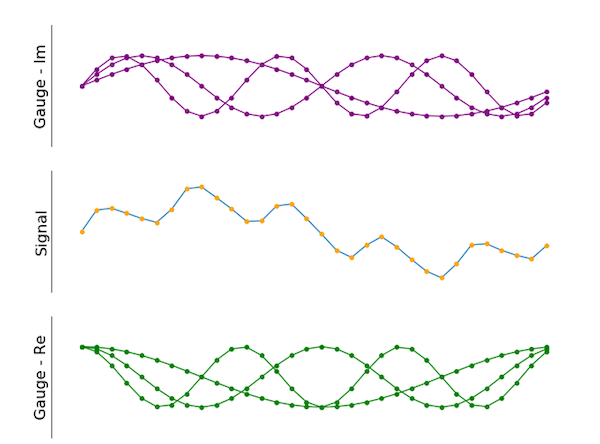

By comparing the input to a reference cosine wave (shown in Figure 2), the dot‑product yields a scalar that represents the correlation strength. However, a phase shift of 90° between the input and the reference causes the dot‑product to vanish, even though the signals are clearly related.

To capture both in‑phase and quadrature components, a second reference shifted by 90° is used, producing two correlation values that together form a complex number:

output = B + i·A

Extending this approach across a range of frequencies results in the full DFT spectrum.

Mathematical Formulation

DFT is defined as:

X(k)=\sum_{n=0}^{N-1} x(n)·e^{-j2πkn/N}

where N is the sample count and k indexes the output frequency bins.

Fast Fourier Transform (FFT) Limitations

- Input length must be a power of two.

- Frequency bins are uniformly spaced at

fs/N(e.g., 48 kHz with 256 samples yields 187 Hz spacing). - Real‑valued inputs produce symmetric output; the second half contains conjugates of the first half.

Using the PowerQuad FFT Engine

The PowerQuad’s Transform Engine implements the FFT algorithm using fixed‑point multiply‑accumulate operations, making it ideal for low‑power, real‑time applications. The NXP SDK provides ready‑to‑run examples; the powerquad_transform project demonstrates a fixed‑16 FFT workflow.

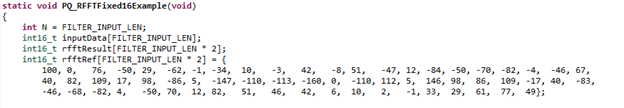

The core routine, PQ_RFFTFixed16Example, initializes the engine for 16‑bit integer data. Floating‑point samples must be scaled to fixed‑point beforehand.

Key configuration parameters:

FILTER_INPUT_LEN– Number of input samples.- Output array length – Twice the input length to store real and imaginary parts.

FILTER_INPUTA_PRESCALER– Scales input to prevent overflow (e.g., set to 5 for 32 samples).

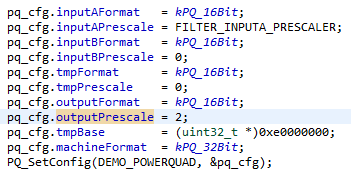

Example code snippets are illustrated in Figure 6 and Figure 7 below.

After configuration, PQ_transformRFFT launches the computation. The CPU can poll for completion or proceed with other tasks, enabling true asynchronous processing.

Takeaways

- The LPC55S69’s PowerQuad offers a highly efficient, low‑latency FFT path for embedded DSP.

- Fixed‑point operation requires careful scaling; the SDK’s example projects handle this automatically.

- Asynchronous execution frees the main cores, boosting overall system performance.

For deeper dives, consult the NXP LPC55S69 SDK and the community discussions on the PowerQuad forums.

Embedded

- Understanding the Buffer Gate: Amplification and Signal Integrity in Digital Circuits

- Gated SR Latch: Enhancing Logic Control with an Enable Input

- Mastering the D Latch: A Clean 1‑Bit Memory Circuit

- Understanding the J‑K Flip‑Flop: Design, Logic, and Applications

- Input & Output Coupling Techniques for Amplifiers: Capacitive, Direct, and Transformer Methods

- Defining the Edge: Where Edge Computing Truly Happens

- Neuromorphic Chips: The Next Frontier for AI Performance

- Understanding the Fourier Transform: Fundamentals, Applications, and Signal Decomposition

- Cloud Maintenance: Unlocking Efficiency, Reliability, and Cost Savings

- Edge Computing: The Architecture Driving Tomorrow’s Intelligent Networks