Gated SR Latch: Enhancing Logic Control with an Enable Input

In digital logic design, a gated SR latch is a versatile memory element that updates its state only when a dedicated enable input allows it. This feature is invaluable for preventing unintended state changes and adding an extra layer of control in complex circuits.

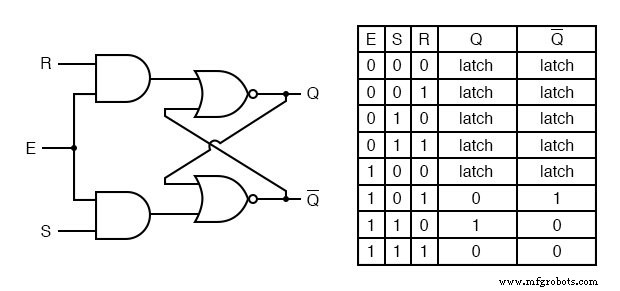

The enable pin, often labeled E or EN, acts as a master switch. When it is low (0), the internal AND gates force their outputs to zero regardless of the Set (S) or Reset (R) signals. Consequently, the latch retains its previous state, effectively “locking” the outputs until the enable is asserted.

Gated SR Latch Truth Table

Only when E = 1 does the latch respond to the S and R inputs, behaving exactly like a standard SR latch. This conditional behavior is crucial in applications such as motor control, where a master lockout input can temporarily disable start/stop pushbuttons.

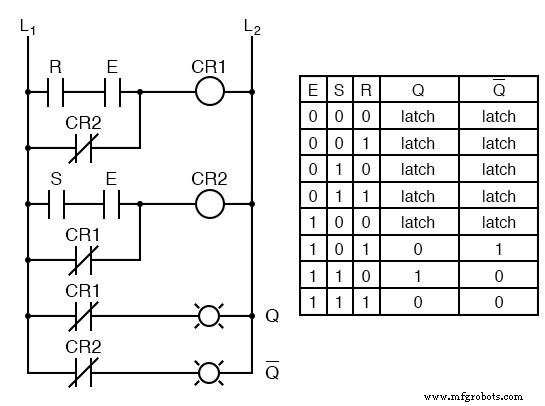

Gated S-R Latch Ladder Logic

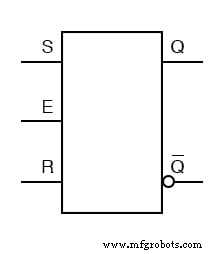

Commercially available semiconductor packages provide pre‑designed gated SR latches, typically represented by a symbol that includes the enable pin. In schematics, the enable line is sometimes written as EN rather than just E.

S-R Gated Latch Symbol

Key Takeaways

- The enable input must be active for the S or R signals to affect the latch output.

- Enable is commonly labeled as E or EN depending on the manufacturer’s convention.

Related Worksheets

Industrial Technology

- NOR Gate SR Latch: Building and Understanding Digital Memory

- Building an Enabled NAND‑Gate SR Latch: Parts, Design, and Operation

- Building a NAND‑Based Set‑Reset Flip‑Flop Circuit

- The 555 Integrated Circuit: A Timeless Benchmark in Analog Design

- Understanding the Buffer Gate: Amplification and Signal Integrity in Digital Circuits

- The S‑R Latch: Fundamentals, Race Conditions, and Practical Applications

- Mastering the D Latch: A Clean 1‑Bit Memory Circuit

- Understanding the J‑K Flip‑Flop: Design, Logic, and Applications

- Mastering D Latches: Design, Operation, and Key Differences

- 74LS47 IC Explained: BCD to 7-Segment Decoder Details