Optimizing Spacer Engineering for Dual‑Gate Tunneling‑Field‑Effect‑Transistor DRAM: Enhancing Retention and Reducing Static Power

Abstract

The dual‑gate tunneling FET (DGTFET) DRAM provides a capacitor‑free design and markedly long retention. Using the Silvaco‑Atlas simulator, we systematically optimize the spacer dielectric stack to suppress reading‑zero leakage and extend the holding window. Simulation results reveal that a low‑k spacer at the source and a high‑k spacer at the drain yield the best trade‑off, achieving a sub‑picoampere reading‑zero current (1×10−14A/μm) and a 10‑second retention time. This configuration reduces static power consumption and refresh overhead while delivering a read‑one/read‑zero current ratio of 107. Scalability analysis highlights the remaining bottleneck and outlines future improvement directions.

Background

As device geometries shrink, the conventional 1T‑1C DRAM struggles to scale because the capacitor cannot be reduced beyond a certain limit[1–3]. The memory industry therefore explores new materials and device architectures to boost density[4,5]. One promising approach is the 1T DRAM with a capacitor‑less structure, first reported in the early 1990s[6,7]. In this architecture, a logical ‘1’ is stored by one of four mechanisms: impact ionization[8], bipolar junction transistor[9], band‑to‑band tunneling (BTBT)[10], or gate tunneling[11]. The tunneling field‑effect transistor (TFET) based on BTBT is regarded as a potential MOSFET alternative because it offers a high on/off ratio and an ultra‑low off‑state current[12–14]. These attributes are especially advantageous for DRAM, where low off‑state leakage translates into minimal reading‑zero current and reduced static power. Several groups have investigated TFET‑based DRAM[15–20], demonstrating low reading‑zero currents and long retention times. Among them, the dual‑gate TFET (DGTFET) DRAM stands out[19,20]. In a DGTFET DRAM, both write and read operations rely on BTBT. Experiments report a reading‑zero current as low as 1 nA/μm—well below that of traditional 1T‑1C DRAM—and a retention time of 2 s, far exceeding the typical 64 ms refresh interval in computing systems[21]. Even at 85 °C, the retention remains above 300 ms, indicating robustness under harsh conditions. The capacitor‑free design further enhances packing density, making DGTFET DRAM a compelling candidate for next‑generation memory. Despite these strengths, reported retention times and reading‑zero currents are not yet optimal because the DGTFET geometry has not been fully optimized. In this work, we focus on spacer engineering—the choice of dielectric material in the three spacers (source, gate‑gap, and drain)—to enhance DGTFET performance. Spacers are positioned close to the tunneling junctions and therefore exert a strong influence on BTBT[22,23]. By systematically studying the impact of low‑k (SiO2) versus high‑k (HfO2) dielectrics in each spacer, we propose an optimized configuration that dramatically reduces reading‑zero leakage and extends retention time.

Device Structure and Simulation Method

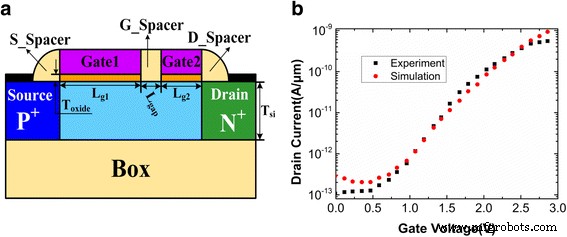

The DGTFET adopts a P‑I‑N configuration, as shown in Fig. 1a. The source and drain are heavily doped P+ (1020/cm3) and N+ (1020/cm3) regions, respectively. The intrinsic channel is split into two gate sections: Gate1, an N+ polysilicon, and Gate2, a P+ polysilicon, separated by a narrow gap. The P+ Gate2 forms a deep charge‑storage well, while the N+ Gate1 controls tunneling during read. Source and drain spacers (S_Spacer and D_Spacer) and the gate‑gap spacer (G_Spacer) default to SiO2. Device dimensions are: silicon film thickness Tsi = 20 nm, Gate1 length Lg1 = 400 nm, Gate2 length Lg2 = 200 nm, gate‑gap length Lgap = 50 nm, and gate‑oxide thickness Toxide = 3 nm (HfO2). Simulations were performed in Silvaco‑Atlas using a non‑local BTBT model that accounts for spatial band‑edge variations and carrier generation/recombination[24]. Model parameters were calibrated against experimental data for SOI TFETs[25], yielding electron and hole effective masses of 0.22 m0 and 0.52 m0, respectively. Heavy doping necessitates band‑gap narrowing, Fermi–Dirac statistics, Shockley–Read–Hall recombination, and doping/temperature‑dependent mobility models. Carrier lifetime—critical for retention—was set to 100 ns, guided by literature ranges of 1 µs to 10 ns[26–28]. Scharfetter and Schenk models were used to capture lifetime dependencies on doping and temperature.

a Schematic of a dual‑gate TFET (DGTFET) DRAM cell. b Comparison between simulated transfer characteristics and experimental results for an SOI TFET[25].

Results and Discussion

Operating Mechanism

Write and read operations in a DGTFET DRAM are governed by BTBT at the drain (write) and source (read) junctions. Figure 2 illustrates the band diagrams during these operations. During a write‑‘1’, a negative bias on Gate2 lowers the channel band under Gate2, creating a thin barrier at the drain side and allowing electrons to tunnel toward the drain while holes accumulate in the deep potential well (~1.2 V). Conversely, a positive Gate2 bias during a write‑‘0’ expels holes from the well, restoring the off state. Read‑‘1’ (Fig. 2b) reveals a channel barrier between Gate1 and Gate2 but not at the channel bottom, enabling an inclined conduction path from the front of Gate1 to the back of Gate2. Read‑‘0’ (Fig. 2c) shows a pronounced channel barrier that blocks electrons, suppressing leakage. The inset of Fig. 2d confirms that electrons cannot cross this barrier during read‑‘0’. Optimal programming conditions are critical: a more negative Gate2 bias enhances saturated BTBT during write‑‘1’; a small negative bias during hold maintains the hole population; and a higher Gate1 bias during read strengthens BTBT for read‑‘1’ but increases read‑‘0’ leakage. Table 1 lists the bias values used, and Fig. 3b demonstrates the resulting transient currents with a 50 ns write/read and a 100 ns hold. The current ratio I1/I0 ≈ 104, matching prior reports[17,19,20].

Impact of Spacer Dielectrics

In DGTFET DRAM, each spacer can be fabricated from either low‑k SiO2 or high‑k HfO2, leading to eight possible dielectric combinations. Table 2 summarizes the read‑1 (I1), read‑0 (I0), and I1/I0 ratio for each configuration, as well as retention at a 2 s hold time. The notation “S” and “H” denote SiO2 and HfO2, respectively, and the three‑letter code lists the S_Spacer, G_Spacer, and D_Spacer in that order. The data reveal that the source spacer dominates I1: using SiO2 at S_Spacer boosts I1 by two orders of magnitude relative to HfO2. The drain spacer chiefly controls I0: an HfO2 D_Spacer suppresses read‑zero leakage to ~10−14A/μm. Thus, the optimal configuration is low‑k at the source and high‑k at the drain, while the gate‑gap spacer has negligible influence when the other two are fixed.

Influence of the Source Spacer

Comparing H/S/S and S/S/S (Fig. 4) shows that SiO2 at the source increases read‑1 current by ~100×. Figure 5 illustrates that HfO2 at the source extends the surface depletion region at the source junction, widening the tunneling barrier. Consequently, the tunneling distance (Fig. 6a) is larger for H/S/S, and the fringe electric field (Fig. 6b) is higher, which reduces the peak field and suppresses BTBT. The exponential BTBT dependence on electric field explains why I1 is significantly higher for S/S/S. Therefore, a low‑k source spacer is essential for maximizing read‑1 current.

Influence of the Drain Spacer

With S_Spacer and G_Spacer fixed to SiO2, changing D_Spacer from SiO2 to HfO2 (Fig. 7) dramatically alters write, hold, and read currents. A high‑k D_Spacer deepens the potential well during write‑1, enhancing the BTBT drive and increasing I1. During hold‑0, the high‑k spacer suppresses BTBT at the drain, reducing the recombination‑induced hold‑0 current. In read‑0, the difference in I0 stems mainly from recombination: a SiO2 D_Spacer allows more holes to accumulate during hold‑0, raising the recombination rate and thus read‑0 leakage (Fig. 9). Therefore, a high‑k D_Spacer is critical for minimizing read‑zero leakage.

Retention Time

Retention is limited by hole recombination during hold. Table 2 shows that even after 2 s, devices with the optimal spacer (S/S/H or S/H/H) maintain I1/I0 > 104. We define the retention time (RT) as the longest hold duration for which I1/I0 remains above 103. Figure 10 demonstrates that the optimized spacer yields an RT of 10 s, far exceeding the conventional 64 ms refresh interval. Compared to earlier studies[17–20], the optimized DGTFET DRAM achieves two orders of magnitude lower read‑zero current and a tenfold longer RT, confirming its suitability for low‑power, high‑density memory.

Scalability

Scalability was assessed by reducing Lg1, Lg2, and Lgap while preserving RT > 2 s. Table 4 lists the performance of the S/S/H configuration across these dimensions. Reducing Lg1 below 200 nm severely degrades I1 due to diminished gate control over the n‑type barrier, while shorter Lg2 narrows the Gate1–Gate2 barrier and increases I0. Lgap has minimal impact on I1 but slightly elevates I0 when reduced below 20 nm. Consequently, the smallest viable dimensions are Lg1 = 200 nm, Lg2 = 150 nm, and Lgap = 20 nm, which still exceed the 20 nm/18 nm node 1T‑1C DRAM. Nevertheless, the benefits of a capacitor‑free, low‑power, high‑RT architecture justify the larger footprint. Future work will target sub‑100 nm scaling of DGTFET DRAM.

Conclusions

We have demonstrated that spacer engineering profoundly influences DGTFET DRAM performance. A low‑k spacer at the source expands the surface depletion region, boosting read‑1 current, while a high‑k spacer at the drain suppresses read‑zero leakage by deepening the potential well and limiting BTBT during hold. Optimizing the dielectric stack yields a sub‑picoampere read‑zero current and a 10‑second retention time, surpassing prior TFET DRAMs and delivering a 107 read‑ratio. Scalability analysis indicates that the minimum viable dimensions remain larger than state‑of‑the‑art 1T‑1C DRAM, but the capacitor‑free, low‑power, and long‑retention advantages make DGTFET DRAM a compelling path forward. Future efforts will focus on sub‑100 nm scaling and integration into high‑density memory arrays.

Abbreviations

- DGTFET:

Dual‑gate tunneling field‑effect transistor

- DRAM:

Dynamic random access memory

Nanomaterials

- Sensor‑Based Project Ideas for Final‑Year Engineering Students

- Reliability Engineering Fundamentals for Plant Engineers

- Optimizing Dip‑Coating Parameters for High‑Performance Three‑State Electrochromic Devices

- Optimizing Programming for Capacitorless 1T DRAM Using Dual‑Gate TFET Technology

- Optimizing Sol–Gel Electrospinning for High‑Performance Polyamide 6/66 Nanofiber Bundles

- Enhancing Broadband Photodetection with Self‑Assembled Dielectric Microcavity Arrays

- Rapid Optical Mapping of Defect Formation in Monolayer WSe₂: Guiding Optimal CVD Growth

- Tailoring Side Facets of Vertical [100] InP Nanowires for Innovative Radial Heterostructures

- Optimizing Ceramic Geometry in High Chromium Cast Iron/Zirconia‑Toughened Alumina Composites via Particle‑Scale Numerical Modeling

- Optimizing Sapphire Light‑Guide Layer Thickness to Boost UV‑LED Light Extraction Efficiency