Optimizing Programming for Capacitorless 1T DRAM Using Dual‑Gate TFET Technology

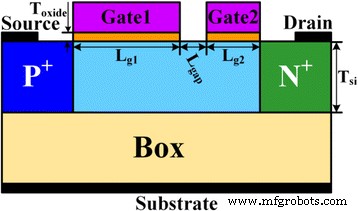

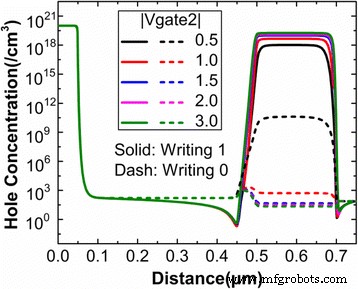

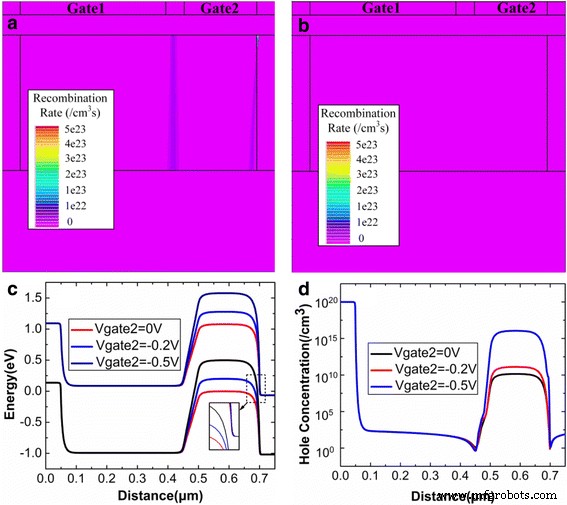

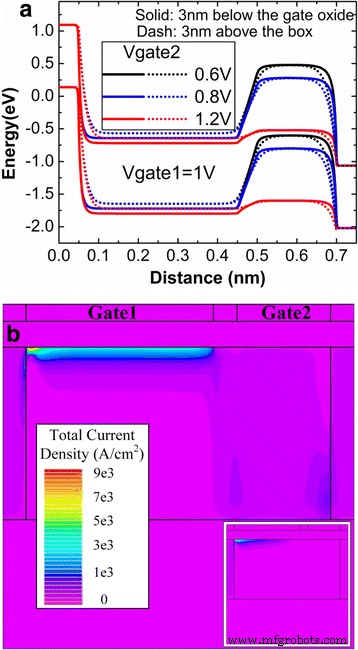

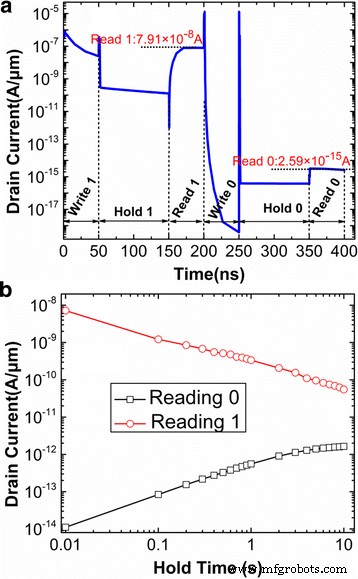

Large capacitor volumes and elevated leakage currents in conventional one‑transistor‑one‑capacitor (1T‑1C) DRAM cells impede further scaling. The tunneling field‑effect transistor (TFET), with its ultra‑low off‑state leakage and steep sub‑threshold slope, is a promising alternative. This study introduces a capacitor‑less 1T DRAM architecture that employs a dual‑gate TFET (DG‑TFET). The dual‑gate design separates write and read functions, enabling superior performance: a retention time (RT) exceeding 2 s and minimal temperature sensitivity. Using Silvaco‑Atlas simulations, we develop a systematic programming‑optimization strategy that maximizes the read‑1/read‑0 current ratio (up to 10⁷) while preserving long retention, thereby reducing refresh rate and dynamic power consumption. Dynamic random‑access memory (DRAM) has become an essential component in mobile and computing systems [1–3]. However, as device geometries shrink, the capacitors in conventional 1T‑1C DRAM cells occupy a large fraction of the device area, hindering further scaling. A promising alternative is the capacitor‑less 1T DRAM that relies on a floating‑gate transistor. This approach can deliver higher density packaging [4] but suffers from temperature‑dependent read currents because charge transport during readout relies on thermionic emission, leading to a sub‑threshold swing exceeding 60 mV/dec and increased leakage [5–9]. TFETs, which conduct via band‑to‑band tunneling (BTBT), offer sub‑60 mV/dec SS, ultra‑low off‑state leakage, and weak temperature dependence [10–14]. Their high I_on/I_off ratio makes them attractive as the core transistor in a DRAM cell [15]. A dual‑gate TFET (DG‑TFET) DRAM has been proposed, where the write operation stores charge through BTBT at the drain side under Gate 2, while the read operation extracts current via BTBT at the source side under Gate 1 [16–18]. Although previous studies have demonstrated RT values above 64 ms and reduced temperature sensitivity, the read‑1/read‑0 current ratio remains sub‑optimal due to non‑ideal programming conditions. We therefore present a detailed programming‑optimization guideline for the DG‑TFET DRAM, leveraging Silvaco‑Atlas simulations to identify optimal biasing for write, hold, and read stages. The optimized conditions yield a read‑1/read‑0 current ratio of 10⁷ and an RT exceeding 2 s, while significantly lowering the read‑0 current and overall power consumption. The investigated DG‑TFET structure is illustrated in Fig. 1. The source (P⁺) and drain (N⁺) doping concentrations are 1 × 10²⁰ cm⁻³. The intrinsic channel is split into Gate 1 (N⁺ polysilicon) and Gate 2 (P⁺ polysilicon) with a 50 nm gap. Gate 2 forms a deep physical well that stores holes, while Gate 1 ensures a low‑hole‑concentration underlap region to facilitate readout. Device parameters: bulk Si thickness 20 nm; Gate 1 length 400 nm; Gate 2 length 200 nm; gate‑oxide thickness 3 nm. Schematic of DG‑TFET DRAM cell. The source is P⁺, the drain is N⁺, Gate 1 is N⁺ polysilicon, and Gate 2 is P⁺ polysilicon. The simulation employs Silvaco‑Atlas with the Non‑Local BTBT model [19] and parameters calibrated to experimental data [20]. Shockley‑Read‑Hall recombination, Fermi statistics, and field‑dependent mobility are also included. Electron and hole lifetimes are set to 100 ns, and the default temperature is 300 K. During a write‑1 operation, a negative bias on Gate 2 raises the channel bands beneath the gate, narrowing the BTBT barrier between channel and drain. This promotes electron tunneling to the drain, fully depleting the channel under Gate 2 and leaving a deep potential well that captures the generated holes. A subsequent write‑0 operation applies a positive bias on Gate 2, allowing the stored holes to recombine at the drain side. The optimal negative bias magnitude is –1.3 V for write‑1 and +1.3 V for write‑0, as higher absolute voltages saturate BTBT and yield no further improvement in hole accumulation. Hole concentrations on the channel surface after writing. Solid line: write‑1; dashed line: write‑0. After writing, the cell is held at a small negative bias on Gate 2 (–0.2 V) to deepen the potential well and suppress hole recombination during a hold‑1 interval. A negative bias during hold‑0 would inadvertently lower the tunneling barrier near the drain, accelerating recombination and degrading the 0 state. Thus, –0.2 V is the optimal holding bias for both states. Recombination rate after holding. (a) 0 V; (b) –0.5 V. (c) Energy band diagram; (d) Hole concentration after hold‑0. Reading is performed with a drain bias of 1 V. Gate 1 is fixed at +1 V to maximize BTBT at the source, enhancing the read‑1 current. Gate 2 is tuned to +0.8 V: this voltage keeps the channel under Gate 2 sufficiently depleted during a read‑0 operation, thereby suppressing electron flow to the drain and reducing the read‑0 current, while still allowing efficient tunneling during read‑1. The resulting read‑1/read‑0 current ratio reaches 10⁷. Energy band diagram (a) and total current density (b) after read‑0. The optimal Gate 2 voltage is +0.8 V. With the optimized biases (write‑1: –1.3 V, write‑0: +1.3 V, hold: –0.2 V, read‑1: Gate 1 = +1 V, Gate 2 = +0.8 V), transient simulations (write/hold/read: 50 ns/100 ns/50 ns) show a read‑1/read‑0 current ratio of 10⁷ (Fig. 9a). Even after a holding time of 10 s, the ratio remains above 10 (Fig. 9b). The RT exceeds 2 s, surpassing earlier reports, and the read‑0 current is markedly lower than in prior studies, translating into reduced dynamic power. (a) Transient drain currents during write/hold/read. (b) Read‑1 and read‑0 currents versus holding time. We have established a comprehensive programming‑optimization protocol for the dual‑gate TFET capacitor‑less 1T DRAM, validated by Silvaco‑Atlas simulations. The optimized biasing scheme—write‑1: –1.3 V, write‑0: +1.3 V, hold: –0.2 V, read‑1: Gate 1 = +1 V, Gate 2 = +0.8 V—yields a read‑1/read‑0 current ratio of 10⁷ and an RT exceeding 2 s. The ultra‑low read‑0 current dramatically cuts power consumption and refresh overhead, positioning DG‑TFET DRAM as a strong candidate for next‑generation low‑power, high‑density memory.Abstract

Background

Methods

Results and Discussion

Writing Operation

Holding Operation

Reading Operation

Transient Response

Conclusions

Nanomaterials

- Optimizing Spacer Engineering for Dual‑Gate Tunneling‑Field‑Effect‑Transistor DRAM: Enhancing Retention and Reducing Static Power

- Hybrid In‑Plane and Out‑of‑Plane Coupled Plasmonic Metasurfaces for Enhanced Optical Activity

- Enhancing Energetic Performance by Integrating Al/PTFE Nanolaminates into Copper Exploding Foils

- Rapid Optical Mapping of Defect Formation in Monolayer WSe₂: Guiding Optimal CVD Growth

- Optimizing Ceramic Geometry in High Chromium Cast Iron/Zirconia‑Toughened Alumina Composites via Particle‑Scale Numerical Modeling

- High-Performance Photodetectors Using Lateral Monolayer MoS2/WS2 Heterojunctions

- Mastering G and M Codes: A Comprehensive Guide to CNC Programming

- Understanding Robot Programming: Methods Explained

- Top 11 Robot Programming Essentials Every Beginner Should Master

- Beginner CNC Lathe Programming: Fill-in-the-Blank Exercise