Ultra‑Smooth Copper Substrates Enhance Graphene Quality: Annealing + Electro‑Polishing

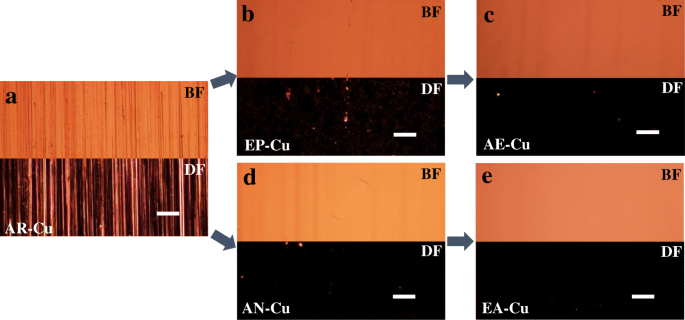

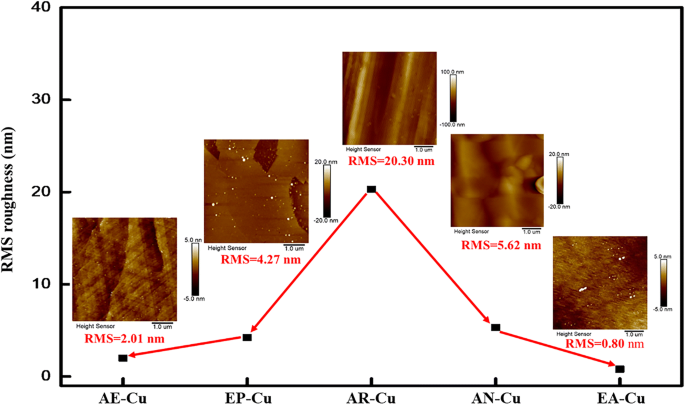

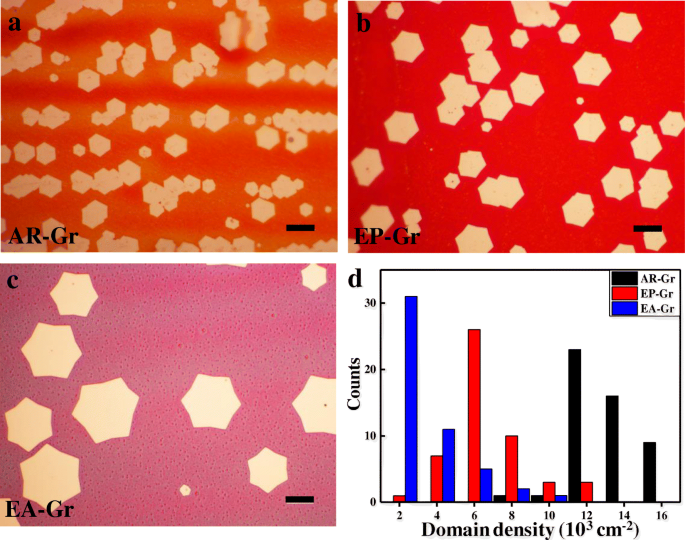

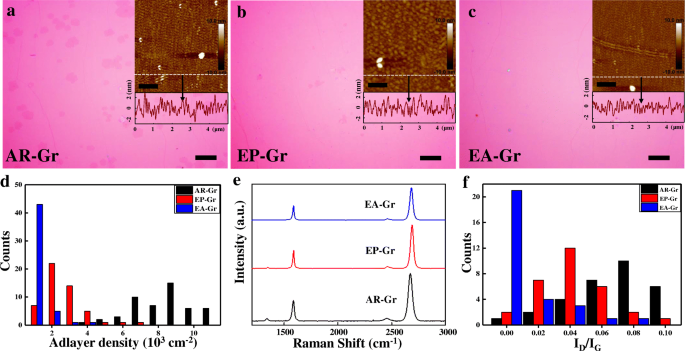

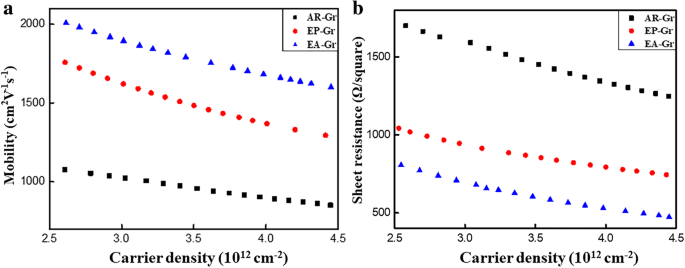

Graphene synthesized by chemical vapor deposition (CVD) often suffers from high defect density due to grain boundaries, limiting its exceptional electronic properties and hindering integration into advanced devices. This study demonstrates a clear link between copper (Cu) substrate morphology and the resulting graphene domain density. By combining thermal annealing with electro‑polishing, we achieve ultra‑smooth Cu surfaces that remain stable at elevated temperatures. Electro‑polishing performed after pre‑annealing proves more effective than either treatment alone, as residual dislocations and point defects are released during heating. Graphene grown on these engineered substrates shows markedly lower domain density and improved layer uniformity compared to samples processed with only annealing or only electro‑polishing. Graphene, a monolayer of sp2‑hybridized carbon atoms arranged in a honeycomb lattice, has attracted intense academic and industrial interest because of its extraordinary mechanical, thermal, and electronic properties [1,2,3,4]. Among various growth techniques, CVD on metal catalysts—especially Cu—remains the most scalable method for producing large‑area, high‑quality films [5,6]. However, CVD‑grown graphene is typically polycrystalline, with grain boundaries that degrade carrier mobility and other functional properties [7,8,9]. Therefore, minimizing crystalline defects and domain density is essential for realizing the full potential of graphene in next‑generation devices [11]. Extensive work has shown that the nucleation density of graphene correlates strongly with the morphology of the Cu substrate [12,13,14]. Commercial Cu foils produced by cold‑rolling exhibit rolling lines, strain fields, surface impurities, and native oxides that act as nucleation sites and compromise film uniformity [12,15,16]. To address these issues, a variety of pretreatments have been explored, including annealing, physical polishing, etching, electro‑polishing, liquefaction, and melt‑solidification [17–32]. Among them, thermal annealing and electro‑polishing are most commonly employed due to their effectiveness and operational simplicity. Annealing relieves internal stress and promotes grain growth, while electro‑polishing reduces surface roughness and removes surface defects [13,27,34]. Nevertheless, both approaches have limitations: annealed Cu can develop step bunching and atom evaporation, whereas conventional electro‑polishing may leave etching pits and spikes. Consequently, a robust method that yields ultra‑smooth, defect‑free Cu surfaces is still needed. In this work, we integrate annealing and electro‑polishing to produce ultra‑smooth Cu foils. By first annealing to release internal strain and dislocations, then applying electro‑polishing, we preserve the smooth surface even at the high temperatures required for CVD. This sequence minimizes surface reconstruction and allows us to demonstrate a substantial reduction in graphene domain density and defect density, thereby improving electrical transport performance. As‑received Cu (AR‑Cu) foils (25 µm, 99.8 % purity, Alfa Aesar #46365) served as the baseline material. For annealed Cu (AN‑Cu), foils were heated to 1050 °C in H2 at 6.8 Pa for 1 h. Electro‑polished Cu (EP‑Cu) involved an anode–cathode setup with the test foil as anode, using an electrolyte of 500 ml phosphoric acid, 250 ml acetic acid, and 250 ml isopropyl alcohol at a current density of ~47 A m–2 for 30 min. Electro‑polished annealed Cu (EA‑Cu) was prepared by annealing followed by electro‑polishing, while annealed electro‑polished Cu (AE‑Cu) was the reverse sequence. Graphene was grown in an atmospheric‑pressure CVD system (Chengdu Hao‑Shi Technology Ltd.) on 2 × 1 cm² Cu substrates. The foils were heated to 1050 °C at 17.5 °C min–1, then annealed for 30 min under 200 sccm Ar and 4 sccm H2. Subsequent growth employed 1 sccm CH4/Ar (1 % CH4) for a controlled period to yield either isolated domains or continuous films. Parallel placement of substrates minimized gas transport variations. Transfer to 285 nm SiO2/Si wafers followed a PMMA‑wet method [5]. Optical microscopy (Nikon ECLIPSE LV100D), atomic force microscopy (AFM, Veeco D5000), Raman spectroscopy (Renishaw Invia, λ = 532 nm), and van der Pauw‑Hall measurements (Copia HMS‑5000) were performed. For electrical testing, transferred graphene (~1 × 1 cm²) was annealed at 200 °C under vacuum to desorb ambient adsorbates before measurement. Figure 1 illustrates the optical micrographs of the Cu foils after each treatment. The as‑received surface (Fig. 1a) displays pronounced corrugations in both bright and dark fields. Post‑treatments (Fig. 1b–e) show progressively smoother surfaces. Optical micrographs of Cu foils with different pre‑treatments: a AR‑Cu, b EP‑Cu, c AE‑Cu, d AN‑Cu, e EA‑Cu. Scale bars, 20 µm. AFM analysis (Fig. 2) quantifies surface roughness. AR‑Cu exhibits an RMS roughness of 20.30 nm, while annealing and electro‑polishing reduce it to 5.62 nm and 4.27 nm, respectively. Combining the two methods—particularly EA‑Cu—further lowers the RMS to 0.80 nm, the smoothest among all samples. The superiority of EA‑Cu stems from strain release during annealing, which permits a more uniform electro‑polished finish. In contrast, AE‑Cu shows increased roughness because dislocations migrate to the surface during the subsequent annealing step. Average RMS roughness evolution after each processing step (black squares). Consistent with prior reports [12,23,34,38], graphene domain density decreases as Cu surface roughness diminishes. AR‑Gr (grown on AR‑Cu) shows a high domain density of 1.16 × 10⁴ cm⁻² (Fig. 3a). EP‑Gr (on EP‑Cu) reduces this by 2.25× to 5.2 × 10³ cm⁻² (Fig. 3b). EA‑Gr (on EA‑Cu) achieves a remarkable 1.7 × 10³ cm⁻²—seven times lower than AR‑Gr and 3.2 times lower than EP‑Gr (Fig. 3c). The histogram (Fig. 3d) quantitatively confirms the correlation between smoother Cu and reduced nucleation density, while also indicating an enhanced growth rate for EA‑Gr. Optical micrographs of graphene domains: a AR‑Cu, b EP‑Cu, c EA‑Cu (scale bars, 10 µm). d Histogram of domain density for the three substrates (120 × 90 µm² sampling). Transferred films further reveal adlayer distribution (Fig. 4). AR‑Gr contains abundant adlayers (7.3 × 10³ cm⁻²), EP‑Gr reduces this by fourfold to 1.8 × 10³ cm⁻², while EA‑Gr achieves a minimal adlayer density of 2 × 10² cm⁻²—36× lower than AR‑Gr. AFM images confirm that EA‑Gr possesses the smoothest morphology, with RMS amplitudes of 245.2 pm (AR‑Gr), 175.7 pm (EP‑Gr), and 94.2 pm (EA‑Gr). Transferred graphene films: a AR‑Cu, b EP‑Cu, c EA‑Cu (scale bars, 10 µm). AFM inset (1 µm). d Adlayer density histogram. e Raman spectra. f ID/IG histogram. Raman analysis (Fig. 4e,f) further substantiates the superior crystallinity of EA‑Gr, exhibiting an ID/IG ratio of ~1 % versus ~10 % (AR‑Gr) and ~5 % (EP‑Gr). This reflects a drastic reduction in defect density and validates the link between substrate smoothness and graphene quality. Van der Pauw‑Hall measurements (Fig. 5) demonstrate that EA‑Gr delivers the highest carrier mobility and lowest sheet resistance across a range of carrier densities. These improvements directly result from the reduced defect landscape introduced by the ultra‑smooth Cu substrate. Carrier mobility (a) and sheet resistance (b) versus carrier density at room temperature. We have established a simple, scalable protocol that combines annealing and electro‑polishing to fabricate ultra‑smooth Cu substrates. This sequential treatment outperforms either step alone by preventing surface reconstruction during high‑temperature CVD, thereby reducing graphene domain density, adlayer formation, and defect density. The resulting films exhibit superior electrical transport properties, underscoring the critical role of substrate engineering in high‑performance graphene synthesis. The method is readily applicable to other two‑dimensional materials and thin‑film technologies. Annealed electro‑polished Cu Atomic force microscopy Annealed Cu As‑received Cu Graphene grown on AR‑Cu Bright field Chemical vapor deposition Dark field Electro‑polished annealed Cu Graphene grown on EA‑Cu Electro‑polished Cu Graphene grown on EP‑Cu Optical microscopy Root mean squareAbstract

Background

Methods

Cu Foil Preparation

Graphene Growth and Transfer

Characterization

Results and Discussion

Cu Foil Morphology

Graphene Growth Quality

Electrical Transport

Conclusions

Abbreviations

Nanomaterials

- Fluorescent Nanomaterials: Advances, Synthesis, and Biomedical Applications

- Hybrid Graphene/WO₃ and Graphene/CeOx Electrodes for High‑Performance Supercapacitors

- Infrared Electromagnetic Field Redistribution on Graphene by Silver Nanoparticle Dimers

- Secondary Transfer of Graphene Electrodes for Highly Stable Flexible OLEDs

- Predicting Surface Impedance of Metasurface–Graphene Hybrid Structures in the Terahertz Regime

- Choosing the Right Surface Finish for Custom Molded Products

- Essential Strategies for Effective Weld Preparation

- Launching Our Advanced Waterjet Cutting Service: A Commitment to Speed and Precision

- Taiwan CNC Coordinate Measuring Machines – Precision for High‑Quality Production

- From Factories to Labs: The Versatile Power of Industrial Robots