Optimizing Ohmic Contacts on p‑GaAs Nanowires for Low‑Resistance, High‑Reliability Devices

Abstract

The performance of Ohmic contacts on semiconductor nanowires (NWs) is pivotal for integrating them into electronic and optoelectronic systems. Because NWs have nanometric dimensions and unique surface orientations, conventional planar processing techniques are inadequate. In this study, we present the fabrication and systematic optimization of Pt/Ti/Pt/Au Ohmic contacts on Be‑doped p‑GaAs NWs grown by molecular beam epitaxy (MBE). Current–voltage (IV) measurements reveal that linear IV characteristics are achieved by carefully tuning the metal stack geometry, pre‑metal surface treatment, and post‑deposition annealing. Notably, a thin Pt interlayer deposited directly on the GaAs NWs prior to the Ti/Pt/Au multilayer reduces contact resistance by 95 %, attributable to the superior crystallinity of Pt compared to Ti on the GaAs (110) sidewalls, as confirmed by grazing‑incidence X‑ray diffraction (GIXRD). These results provide clear guidelines for engineering low‑resistance Ohmic contacts on p‑GaAs NWs, enhancing device reliability and performance.

Introduction

Creating robust, low‑resistance Ohmic contacts is a cornerstone of high‑performance semiconductor devices. GaAs remains a key material for lasers, solar cells, and photodetectors, driving extensive research into both p‑type and n‑type contact schemes. Conventional contact fabrication follows a four‑step workflow: removal of the native oxide, surface passivation, metal deposition, and thermal annealing. Au‑based alloys, especially Au/Zn/Au and Ti/Pt/Au, dominate the literature for p‑GaAs contacts due to their low resistivity and thermal stability.

III–V nanowires (NWs) such as GaAs are emerging as versatile nanoscale platforms for LEDs, photovoltaics, and photodetectors, demanding tailored processing approaches. Self‑catalyzed GaAs NWs exhibit (110) sidewall facets, a crystallographic orientation distinct from the (100) planes of bulk films. This orientation influences surface states, Schottky barrier heights, and metal crystallization dynamics, thereby affecting contact quality.

Previous work on p‑GaAs NWs has explored a range of surface treatments and metal stacks, yet a systematic comparison on identical NWs is lacking. In this work, we examine the influence of Pt‑ and Ti‑based contacts and surface pre‑treatments on the IV behavior of self‑catalyzed Be‑doped GaAs NWs. Structural insights are gained through GIXRD of Ti, Pt, and Pt/Ti thin films deposited on GaAs (110) substrates, linking crystallinity to electrical performance.

Materials and Methods

Nanowire Growth

Be‑doped p‑GaAs NWs were grown via solid‑source MBE on lithography‑free oxide patterns on p‑Si (111) substrates prepared by droplet epitaxy and spontaneous oxidation. The growth temperature was 640 °C, with a Ga flux equivalent to a 0.3 µm/h planar rate on GaAs (100). After a 60 s Ga wetting step, growth commenced with an As₂ flux (V/III ratio = 9) and a Be flux corresponding to 2.0 × 10¹⁹ cm⁻³, confirmed by Hall measurements on planar calibrants. A 60‑min growth yielded NWs with a hexagonal cross‑section, pure zinc‑blende GaAs lattice, and (110) sidewalls, as established in prior studies.

Contacts Fabrication and Characterization

The NWs were transferred to a p‑GaAs (100) substrate covered by 200 nm SiO₂, pre‑patterned with Ti/Au pads for transport. NW positions were identified by low‑magnification SEM. A positive e‑beam resist was spin‑coated, exposed, and developed in MIBK:IPA, followed by optional oxygen plasma cleaning to remove residual resist from sidewalls. Metal stacks were deposited by e‑beam evaporation: Ti/Pt/Au (20/20/200 nm) or Pt/Ti/Pt/Au (5/10/10/200 nm). Rapid thermal annealing (RTA) at 400 °C for 30 s was applied to the Pt/Ti/Pt/Au samples. Five distinct processes (P1–P5) combined different oxide‑removal (2.8 % NH₄OH or 3.7 % HCl) and passivation (15 % (NH₄)₂Sₓ) steps, as detailed in Table 1. Four equally spaced contacts were fabricated along each NW; IV data were recorded at room temperature using a Keysight probe station.

Structural Investigation by Grazing Incidence X‑ray Diffraction

To probe the microstructure of the contact layers, GIXRD was performed on reference Ti, Pt, and Pt/Ti films (thicknesses matching those in the NW devices) deposited on undoped GaAs (110) substrates. The same native‑oxide removal and (NH₄)₂Sₓ passivation were applied. Measurements used Cu Kα radiation (λ = 1.54 Å) at an incidence angle ω = 0.75°, ensuring a shallow penetration depth suitable for the thin films. Diffraction peaks were indexed against ICDD files #00‑044‑1294 (HCP Ti) and #00‑004‑0802 (FCC Pt), with refraction corrections applied.

Results and Discussion

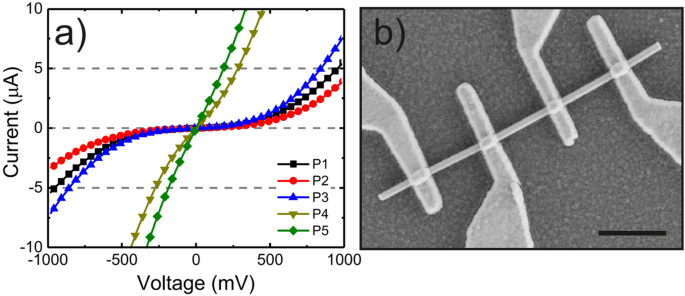

Figure 1a displays the IV curves for samples P1–P5, while Figure 1b shows an SEM image of a representative Be‑doped GaAs NW with four contacts. The symmetric, nonlinear IVs of P1–P4 indicate Schottky behavior with comparable barrier heights. P1, which follows the standard planar process, fails to yield Ohmic behavior, underscoring the inadequacy of planar protocols for NWs. Typically, HCl‑based oxide removal followed by (NH₄)₂Sₓ passivation is employed for NW contacts; oxygen plasma cleaning is sometimes used to remove resist residues but can introduce As vacancies that increase the depletion width.

a IV from Be‑doped GaAs NWs with contacts fabricated using processes P1–P5 as described in Table 1. b SEM image of a representative Be‑doped GaAs NW with four evenly spaced contacts. The scale bar is 1 µm

Comparing P2 (with oxygen plasma) and P3 (without) reveals that oxygen plasma degrades contact performance, while HCl removal combined with (NH₄)₂Sₓ passivation improves the Schottky barrier height relative to P1.

Adding a 5‑nm Pt interlayer (P4) significantly enhances IV linearity and reduces contact resistance. Subsequent RTA (P5) further lowers resistance, achieving a fully Ohmic IV profile.

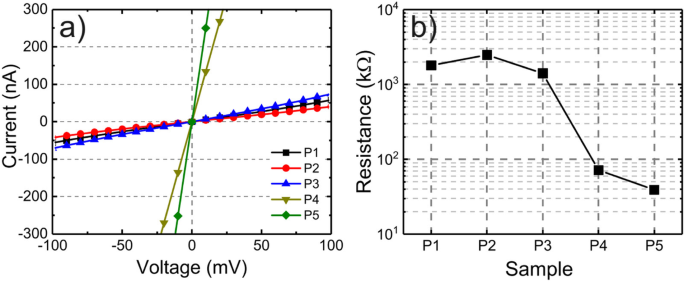

Figure 2a shows IVs within ±100 mV, emphasizing the linear regime dominated by contact resistance. Figure 2b presents the extracted total channel resistance (contacts + NW) from linear fits. P4 reduces resistance from 1.4 MΩ (P3) to 72 kΩ, and P5 achieves 40 kΩ, a 95 % drop attributed to the Pt interlayer.

a IV from P1 to P5 in the 100 mV applied voltage range. b Total channel resistance of P1–P5 obtained from linear fit of the IVs in a

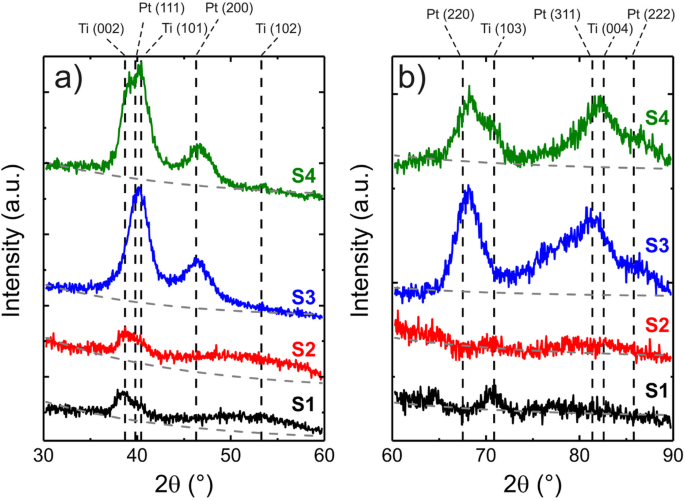

GIXRD analysis of reference films (S1–S4) elucidates the role of crystallinity. Ti films deposited directly on GaAs (110) (S1, S2) exhibit broad, low‑intensity peaks, indicating poor crystallinity regardless of (NH₄)₂Sₓ passivation. In contrast, Pt films (S3, S4) show sharp, well‑defined peaks (111, 200, 220, 311, 222), confirming high crystallinity. When Pt is introduced beneath Ti (S4), Ti crystallinity improves relative to S1/S2, suggesting that Pt promotes better film growth on GaAs (110). These structural findings correlate with the electrical data: the Pt/Ti/Pt/Au stack in P4 and P5 yields markedly lower resistance due to the superior interface quality.

a GIXRD patterns from samples S1–S4 in the 30–60° range and b in the 60–90° range. Dashed gray lines indicate the diffuse background. Black dashed lines mark Ti and Pt diffraction planes.

Overall, the data demonstrate that a thin Pt interlayer prior to Ti/Pt/Au drastically reduces contact resistance by promoting a highly crystalline metal–GaAs interface. Thermal annealing further refines the contact without inducing deleterious reactions, as confirmed by literature on Pt stability up to 500 °C.

Conclusions

By correlating single‑NW IV measurements with GIXRD of reference thin films, we established that Ti films on GaAs (110) suffer from poor crystallinity, directly inflating contact resistance. Introducing a 5‑nm Pt layer before Ti/Pt/Au reduces total resistance by 95 %, attributable to the superior crystallinity of Pt on the (110) sidewalls. Rapid thermal annealing further improves Ohmic behavior. These insights provide a clear pathway for designing low‑resistance Ohmic contacts on Be‑doped p‑GaAs NWs, emphasizing the critical role of the metal–semiconductor interface and guiding future studies on crystallization across different III‑V orientations.

Availability of Data and Materials

The datasets supporting the conclusions of this study are included within the article.

Abbreviations

- FCC:

Face‑centered cubic

- GIXRD:

Grazing incidence X‑ray diffraction

- HCP:

Hexagonal‑closed packed

- IV:

Current–voltage

- NW:

Nanowire

- RTA:

Rapid thermal annealing

- SEM:

Scanning electron microscopy

Nanomaterials

- Why Tungsten Contacts Power Reliable Electrical Appliances

- Designing Reliable Switch Contacts: Materials, Types, and Protection Strategies

- Understanding Digital Logic Functions: OR, AND, NOT, and Beyond

- High‑Performance SnSe Nanoflake Field‑Effect Transistors Featuring Low‑Resistance Gold Ohmic Contacts

- High-Performance Ohmic Contacts: Two-Step Al‑Doped ZnO Deposition on p‑GaN

- Enhancing GaAs Nanowire Pin Junction Solar Cells via AlGaAs/GaAs Heterojunctions

- Innovations in Beta-Gallium Oxide Metal Contacts for Advanced Power Electronics

- Heterostructure ReS₂/GaAs Saturable Absorber Enables Ultra‑Fast Passively Q‑Switched Nd:YVO₄ Laser

- Sub‑10 nm InSe Field‑Effect Transistors Enabled by Novel Sandwiched Indium Ohmic Contacts: A Theoretical Study

- Key Factors in Designing Contactor Contacts