Hardware behavior cannot be implemented without conditional statements and other ways to control the flow of logic. Verilog has a set of control flow blocks and mechanisms to achieve the same.if-else-ifThis conditional statement is used to make a decision about whether certain statements should be e

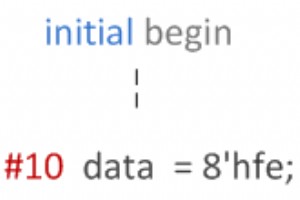

BlockingBlocking assignment statements are assigned using = and are executed one after the other in a procedural block. However, this will not prevent execution of statments that run in a parallel block. module tb; reg [7:0] a, b, c, d, e; initial begin a = 8hDA; $display ([%0t] a

Placing values onto nets and variables are called assignments. There are three basic forms: Procedural Continuous Procedural continuous Legal LHS valuesAn assignment has two parts - right-hand side (RHS) and left-hand side (LHS) with an equal symbol (=) or a less than-equal symbol (<=) in between.

There are ways to group a set of statements together that are syntactically equivalent to a single statement and are known as block statements. There are two kinds of block statements: sequential and parallel.SequentialStatements are wrapped using begin and end keywords and will be executed sequenti

A previous example explored a simple sequence detector. Here is another example for a pattern detector which detects a slightly longer pattern.Design module det_110101 ( input clk, input rstn, input in, output out ); parameter IDLE

A very common example of an FSM is that of a sequence detector where the hardware design is expected to detect when a fixed pattern is seen in a stream of binary bits that are input to it.Example module det_1011 ( input clk, input rstn, input in,

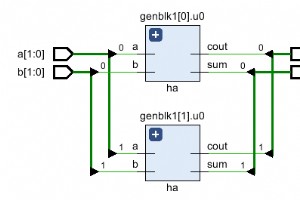

A generate block allows to multiply module instances or perform conditional instantiation of any module. It provides the ability for the design to be built based on Verilog parameters. These statements are particularly convenient when the same operation or module instance needs to be repeated multip

All behavioral code is written inside module and endmodule. So, whatever digital design that you intend to create, itll go inside a module block. It may or may not have ports defined - allow signals to enter the block as input or escape the block as output.ModuleThe empty module in the example below

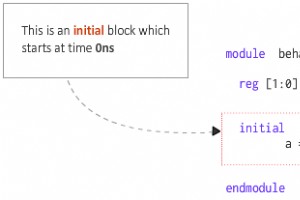

A set of Verilog statements are usually executed sequentially in a simulation. These statements are placed inside a procedural block. There are mainly two types of procedural blocks in Verilog - initial and alwaysSyntax initial [single statement] initial begin [multiple statements] end

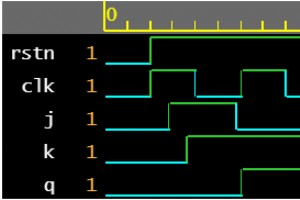

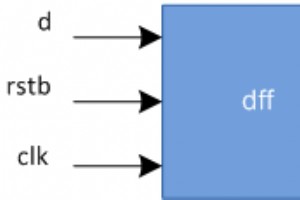

A previous article showed different examples of using an always block to implement combinational logic. An always block is also mainly used to implement sequential logic which has memory elements like flip flops that can hold values.JK Flip FlopA JK flip flop is one of the many types of flops used t

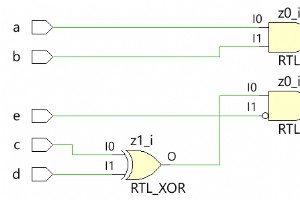

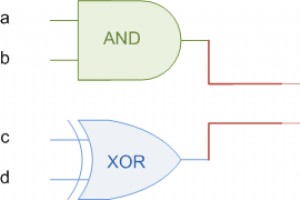

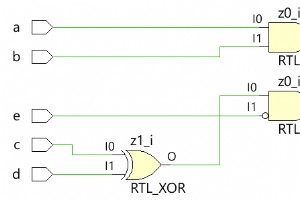

The verilog always block can be used for both sequential and combinational logic. A few design examples were shown using an assign statement in a previous article. The same set of designs will be explored next using an always block.Example #1 : Simple combinational logicThe code shown below implemen

An always block is one of the procedural blocks in Verilog. Statements inside an always block are executed sequentially.Syntax always @ (event) [statement] always @ (event) begin [multiple statements] end The always block is executed at some particular event. The event is defined by a sens

Multi-bit Verilog wires and variables can be clubbed together to form a bigger multi-net wire or variable using concatenation operators { and } separated by commas. Concatenation is also allowed to have expressions and sized constants as operands in addition to wires and variables.Size of each opera

Data that cannot be processed is quite useless, therell always be some form of calculation required in digital circuits and computer systems. Lets look at some of the operators in Verilog that would enable synthesis tools realize appropriate hardware elements.Verilog Arithmetic OperatorsIf the secon

The verilog assign statement is typically used to continuously drive a signal of wire datatype and gets synthesized as combinational logic. Here are some more design examples using the assign statement.Example #1 : Simple combinational logicThe code shown below implements a simple digital combinatio

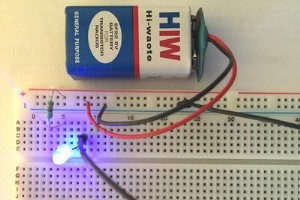

Signals of type wire or a similar wire like data type requires the continuous assignment of a value. For example, consider an electrical wire used to connect pieces on a breadboard. As long as the +5V battery is applied to one end of the wire, the component connected to the other end of the wire wil

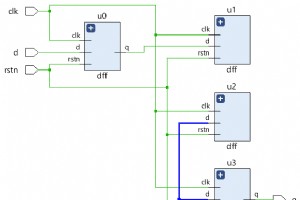

As we saw in a previous article, bigger and complex designs are built by integrating multiple modules in a hierarchical manner. Modules can be instantiated within other modules and ports of these instances can be connected with other signals inside the parent module.These port connections can be don

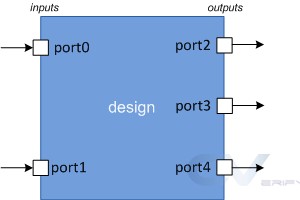

Ports are a set of signals that act as inputs and outputs to a particular module and are the primary way of communicating with it. Think of a module as a fabricated chip placed on a PCB and it becomes quite obvious that the only way to communicate with the chip is through its pins. Ports are like pi

A module is a block of Verilog code that implements a certain functionality. Modules can be embedded within other modules and a higher level module can communicate with its lower level modules using their input and output ports.SyntaxA module should be enclosed within module and endmodule keywords.

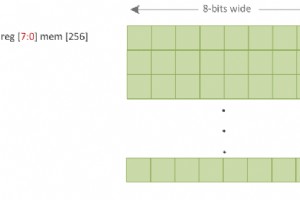

An array declaration of a net or variable can be either scalar or vector. Any number of dimensions can be created by specifying an address range after the identifier name and is called a multi-dimensional array. Arrays are allowed in Verilog for reg, wire, integer and real data types. reg

Verilog