Verilog math functions can be used in place of constant expressions and supports both integer and real maths.Integer Math FunctionsThe function $clog2 returns the ceiling of log2 of the given argument. This is typically used to calculate the minimum width required to address a memory of given size.F

Display system tasks are mainly used to display informational and debug messages to track the flow of simulation from log files and also helps to debug faster. There are different groups of display tasks and formats in which they can print values. Display/Write TasksSyntaxBoth $display and $write di

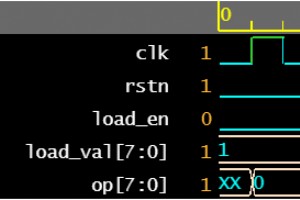

Clocks are fundamental to building digital circuits as it allows different blocks to be in sync with each other.Properties of a clockThe key properties of a digital clock are its frequency which determines the clock period, its duty cycle and the clock phase in relation to other clocks.Clock PeriodT

Verilog design and testbench typically have many lines of code comprising of always or initial blocks, continuous assignments and other procedural statements which become active at different times in the course of a simulation.Every change in value of a signal in the Verilog model is considered an u

Verilog simulation depends on how time is defined because the simulator needs to know what a #1 means in terms of time. The `timescale compiler directive specifies the time unit and precision for the modules that follow it.Syntax `timescale <time_unit>/<time_precision> // Example `t

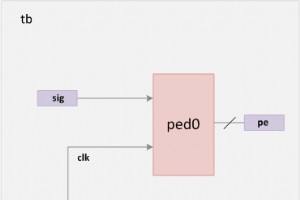

Verilog is a hardware description language and there is no requirement for designers to simulate their RTL designs to be able to convert them into logic gates. So what is the need to simulate? Simulation is a technique of applying different input stimulus to the design at different times to check

Standard Verilog primitives like nand and not may not always be easy or sufficient to represent complex logic. New primitive elements called UDP or user-defined primitives can be defined to model combinational or sequential logic.All UDPs have exactly one output that can be either 0, 1 or X and neve

Verilog also provides support for transistor level modeling although it is rarely used by designers these days as the complexity of circuits have required them to move to higher levels of abstractions rather than use switch level modeling.NMOS/PMOS module des (input d, ctrl, output outn, outp

Digital elements are binary entities and can only hold either of the two values - 0 and 1. However the transition from 0 to 1 and 1 to 0 have a transitional delay and so does each gate element to propagate the value from input to its output.For example, a two input AND gate has to switch the output

Some of the main built-in primitives were discussed in the previous article and it would be good to see some practical examples of using simple and, nor and not gates.Note that in order to write the Verilog code using gates, it is necessary for you to know how to connect the elements. This is very d

Most digital designs are done at a higher level of abstraction like RTL, although at times it becomes intuitive to build smaller deterministic circuits at a lower level by using combinational elements like and and or. Modeling done at this level is usually called gate level modeling as it involves g

Most programming languages have a characteristic feature called scope which defines the visibility of certain sections of code to variables and methods. The scope defines a namespace to avoid collision between different object names within the same namespace.Verilog defines a new scope for modules,

Verilog delay statements can have delays specified either on the left hand side or the right hand side of the assignment operator.Inter-assignment Delays // Delay is specified on the left side #<delay> <LHS> = <RHS> An inter-assignment delay statement has delay value on the LH

There are two types of timing controls in Verilog - delay and event expressions. The delay control is just a way of adding a delay between the time the simulator encounters the statement and when it actually executes it. The event expression allows the statement to be delayed until the occurrence of

Verilog supports a few compiler directives that essentially direct the compiler to treat the code in a certain way. For example, a portion of the code may represent an implementation of a certain feature and there should be some way to not include the code in the design if the feature is not used.Th

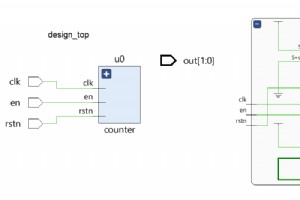

Parameters are Verilog constructs that allow a module to be reused with a different specification. For example, a 4-bit adder can be parameterized to accept a value for the number of bits and new parameter values can be passed in during module instantiation. So, an N-bit adder can become a 4-bit, 8-

A function is meant to do some processing on the input and return a single value, whereas a task is more general and can calculate multiple result values and return them using output and inout type arguments. Tasks can contain simulation time consuming elements such as @, posedge and others. SyntaxA

Often times we find certain pieces of code to be repetitive and called multiple times within the RTL. They mostly do not consume simulation time and might involve complex calculations that need to be done with different data values. In such cases, we can declare a function and place the repetitive c

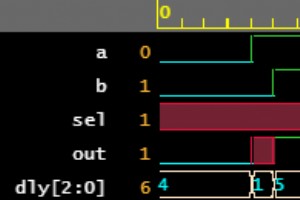

The case statement checks if the given expression matches one of the other expressions in the list and branches accordingly. It is typically used to implement a multiplexer. The if-else construct may not be suitable if there are many conditions to be checked and would synthesize into a priority enco

A for loop is the most widely used loop in software, but it is primarily used to replicate hardware logic in Verilog. The idea behind a for loop is to iterate a set of statements given within the loop as long as the given condition is true. This is very similar to the while loop, but is used more in

Verilog