All behavioral code is written inside module and endmodule. So, whatever digital design that you intend to create, itll go inside a module block. It may or may not have ports defined - allow signals to enter the block as input or escape the block as output.ModuleThe empty module in the example below

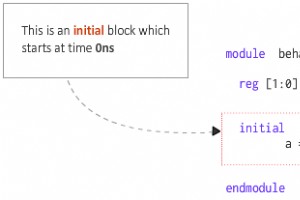

A set of Verilog statements are usually executed sequentially in a simulation. These statements are placed inside a procedural block. There are mainly two types of procedural blocks in Verilog - initial and alwaysSyntax initial [single statement] initial begin [multiple statements] end

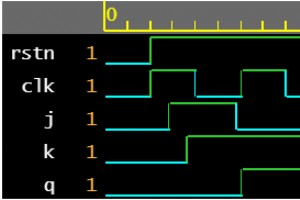

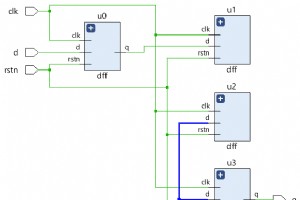

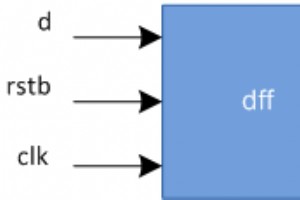

A previous article showed different examples of using an always block to implement combinational logic. An always block is also mainly used to implement sequential logic which has memory elements like flip flops that can hold values.JK Flip FlopA JK flip flop is one of the many types of flops used t

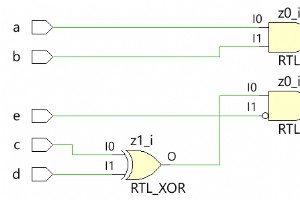

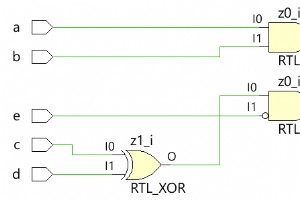

The verilog always block can be used for both sequential and combinational logic. A few design examples were shown using an assign statement in a previous article. The same set of designs will be explored next using an always block.Example #1 : Simple combinational logicThe code shown below implemen

An always block is one of the procedural blocks in Verilog. Statements inside an always block are executed sequentially.Syntax always @ (event) [statement] always @ (event) begin [multiple statements] end The always block is executed at some particular event. The event is defined by a sens

Multi-bit Verilog wires and variables can be clubbed together to form a bigger multi-net wire or variable using concatenation operators { and } separated by commas. Concatenation is also allowed to have expressions and sized constants as operands in addition to wires and variables.Size of each opera

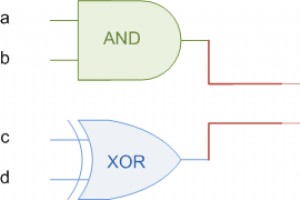

Data that cannot be processed is quite useless, therell always be some form of calculation required in digital circuits and computer systems. Lets look at some of the operators in Verilog that would enable synthesis tools realize appropriate hardware elements.Verilog Arithmetic OperatorsIf the secon

The verilog assign statement is typically used to continuously drive a signal of wire datatype and gets synthesized as combinational logic. Here are some more design examples using the assign statement.Example #1 : Simple combinational logicThe code shown below implements a simple digital combinatio

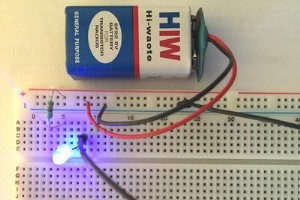

Signals of type wire or a similar wire like data type requires the continuous assignment of a value. For example, consider an electrical wire used to connect pieces on a breadboard. As long as the +5V battery is applied to one end of the wire, the component connected to the other end of the wire wil

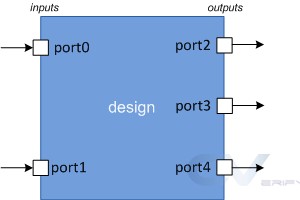

As we saw in a previous article, bigger and complex designs are built by integrating multiple modules in a hierarchical manner. Modules can be instantiated within other modules and ports of these instances can be connected with other signals inside the parent module.These port connections can be don

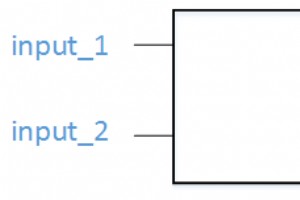

Ports are a set of signals that act as inputs and outputs to a particular module and are the primary way of communicating with it. Think of a module as a fabricated chip placed on a PCB and it becomes quite obvious that the only way to communicate with the chip is through its pins. Ports are like pi

A module is a block of Verilog code that implements a certain functionality. Modules can be embedded within other modules and a higher level module can communicate with its lower level modules using their input and output ports.SyntaxA module should be enclosed within module and endmodule keywords.

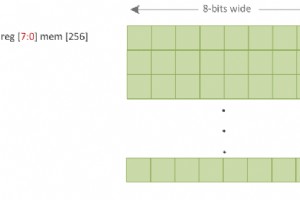

An array declaration of a net or variable can be either scalar or vector. Any number of dimensions can be created by specifying an address range after the identifier name and is called a multi-dimensional array. Arrays are allowed in Verilog for reg, wire, integer and real data types. reg

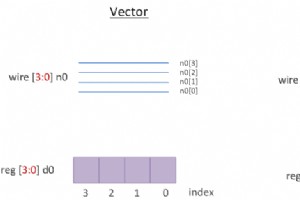

Verilog needs to represent individual bits as well as groups of bits. For example, a single bit sequential element is a flip-flop. However a 16-bit sequential element is a register that can hold 16 bits. For this purpose, Verilog has scalar and vector nets and variables.Scalar and VectorA net or reg

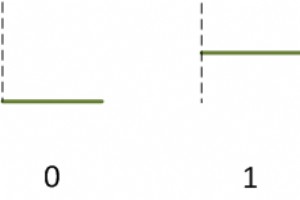

The primary intent of data-types in the Verilog language is to represent data storage elements like bits in a flip-flop and transmission elements like wires that connect between logic gates and sequential structures. What values do variables hold ?Almost all data-types can only have one of the four

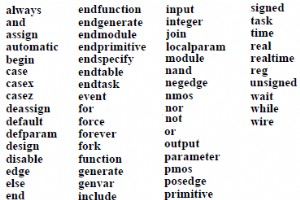

Lexical conventions in Verilog are similar to C in the sense that it contains a stream of tokens. A lexical token may consist of one or more characters and tokens can be comments, keywords, numbers, strings or white space. All lines should be terminated by a semi-colon ;.Verilog is case-sensitive, s

Before we look at more details of the Verilog language, it would be good to understand the different layers of abstraction in chip design.The top layer is the system level architecture that defines the various sub-blocks and groups them based on functionality. For example, a processor cluster would

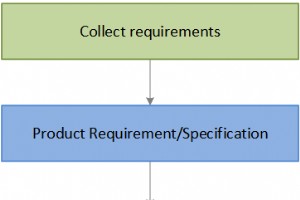

A typical design flow follows a structure shown below and can be broken down into multiple steps. Some of these phases happen in parallel and some sequentially. Well take a look at how a typical project design cycle looks like in the industry today. RequirementsA customer of a semiconductor firm i

In the early days of integrated circuits, engineers had to sit down and physically draw transistors and their connections on paper to design them such that it can be fabricated on silicon. Bigger and complex circuits demanded more engineers, time and other resources and soon enough there was a need

Verilog is a hardware description language (HDL) that empowers engineers to model, simulate, and synthesize digital logic for FPGAs and ASICs. Alongside its close cousin VHDL, Verilog is the industry‑standard language for both academic curricula and commercial product development. If you’re new to t

Verilog