High‑Performance Analog/RF T‑Shaped Gate Dual‑Source Tunnel Field‑Effect Transistor

Abstract

In this study, we introduce a silicon‑based T‑shaped gate dual‑source tunnel field‑effect transistor (TGTFET) and evaluate its performance using detailed TCAD simulations. A comparative analysis with the conventional L‑shaped (LTFET) and U‑shaped (UTFET) TFETs is performed, highlighting the advantages of the TGTFET’s design. The T‑shaped gate introduces a gate overlap that enhances the electric field at the tunneling junction, while the dual‑source architecture doubles the effective tunneling area. By incorporating an n⁺ pocket, the band‑to‑band tunneling (BTBT) rate is further increased. Simulation results demonstrate that the TGTFET achieves an on‑state current of 81 µA/µm and an on/off ratio of 6.7 × 10¹⁰ at a 1 V gate‑to‑source bias. The average sub‑threshold swing (SS_avg) over 0–0.5 V is 51.5 mV/dec, with a minimum swing (SS_min) of 24.4 mV/dec at 0.1 V. The device exhibits strong resilience against drain‑induced barrier lowering (DIBL). Key analog/RF metrics—transconductance (gₘ) of 232 µS/µm, output conductance (g_ds) of 214 µS/µm, gate‑to‑source capacitance (C_gs) of 0.7 fF/µm, gate‑to‑drain capacitance (C_gd) of 3.7 fF/µm, cutoff frequency (f_T) of 11.9 GHz, and gain bandwidth product (GBW) of 2.3 GHz—are all achieved at a drain‑to‑source voltage of 0.5 V. Compared to UTFET and LTFET, the TGTFET delivers superior DC and AC characteristics, positioning it as a compelling candidate for next‑generation low‑power and analog/RF applications.

Background

Continued scaling of metal‑oxide‑semiconductor field‑effect transistors (MOSFETs) has historically driven improvements in power efficiency, switching speed, and device density. However, the inevitable trade‑off between supply‑voltage reduction and leakage currents (I_OFF) leads to rising standby power, while short‑channel effects (SCEs) degrade reliability. To counter these challenges, researchers have focused on reducing sub‑threshold swing (SS) and operating voltage. Tunnel field‑effect transistors (TFETs), leveraging band‑to‑band tunneling, can achieve SS < 60 mV/dec, enabling sub‑0.2 V operation and markedly lower I_OFF.

TFETs are particularly attractive for low‑power digital logic and emerging analog/RF circuits. Yet, conventional P‑I‑N TFETs suffer from limited tunneling area, which caps the on‑state current (I_ON). Recent structural innovations—such as the L‑shaped (LTFET) and U‑shaped (UTFET) gates—have expanded the tunneling interface, boosting I_ON while preserving compactness. Nonetheless, further performance gains and detailed analog/RF characterizations remain essential.

We propose a T‑shaped gate dual‑source TFET (TGTFET) that doubles the tunneling area relative to LTFET and UTFET and introduces gate overlap to sharpen the electric field. Our TCAD study demonstrates that this design delivers higher I_ON, sub‑60 mV/dec SS, and superior analog/RF figures of merit.

Methods

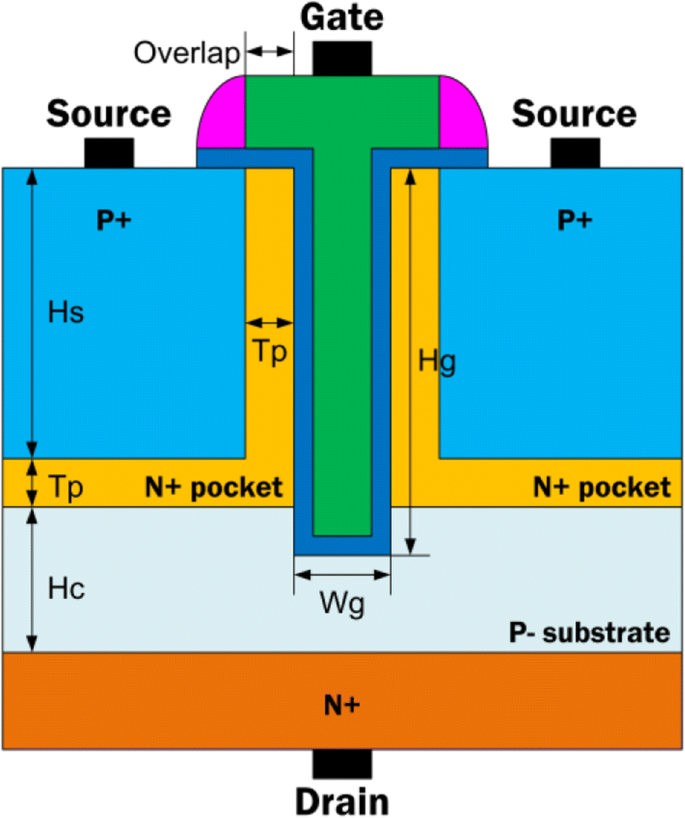

The TGTFET structure is illustrated in Fig. 1. The gate forms a “T” shape (green region), overlapping both vertical and lateral n⁺ pockets (yellow) to amplify the electric field at the tunneling interface. Dual source regions flank the gate (sapphire), while an n⁺ drain resides beneath the channel. This configuration increases the effective tunneling area and steepens the band bending, thus enhancing the BTBT rate.

Schematic of the proposed T‑shaped gate dual‑source tunnel field‑effect transistor (TGTFET)

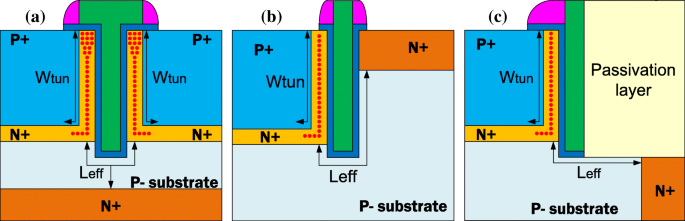

Figure 2 compares the TGTFET, UTFET, and LTFET structures. The gate overlap in TGTFET boosts tunneling efficiency, and the dual‑source arrangement doubles the junction area relative to the other designs.

Comparison of a the proposed TGTFET, b UTFET, and c LTFET

Key simulation parameters are: H_s = 30 nm, H_g = 40 nm, W_g = 6 nm, H_c = 15 nm, T_p = 5 nm, φ = 4.33 eV, T_ox = 2 nm (HfO₂), N_S = 1 × 10²⁰ cm⁻³, N_D = 1 × 10¹⁹ cm⁻³, N_sub = 1 × 10¹⁷ cm⁻³, N_P = 5 × 10¹⁸ cm⁻³. All devices share a 1 µm width in simulation.

Simulations were performed with Silvaco Atlas using a non‑local BTBT model, Lombardi mobility, Fermi statistics, band‑gap narrowing, and Shockley‑Read‑Hall recombination to capture the physics accurately.

Results and Discussion

Device Mechanism and DC Characteristics with Different Parameters

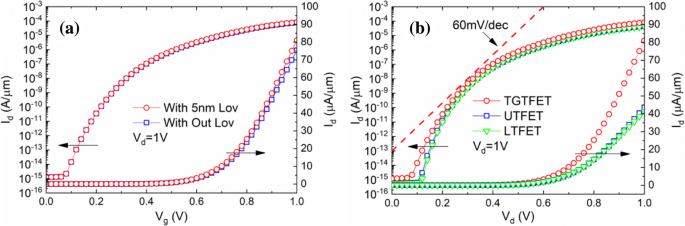

Figure 3a shows the transfer curves of TGTFET with and without gate overlap. The overlap boosts I_ON from 7.5 × 10⁻⁵ to 8.1 × 10⁻⁵ A/µm at V_g = V_d = 1 V. Figure 3b compares TGTFET, UTFET, and LTFET under identical geometry. TGTFET delivers a two‑fold I_ON advantage, with SS_min = 24.4 mV/dec at V_g = 0.1 V and SS_avg = 51.5 mV/dec over 0–0.5 V. On/off ratios reach 6.7 × 10¹⁰ (V_g = V_d = 1 V) and 6.5 × 10⁸ (V_g = V_d = 0.5 V).

Simulated a transfer characteristics of TGTFET with/without gate overlap and b transfer characteristics of TGTFET, UTFET, and LTFET

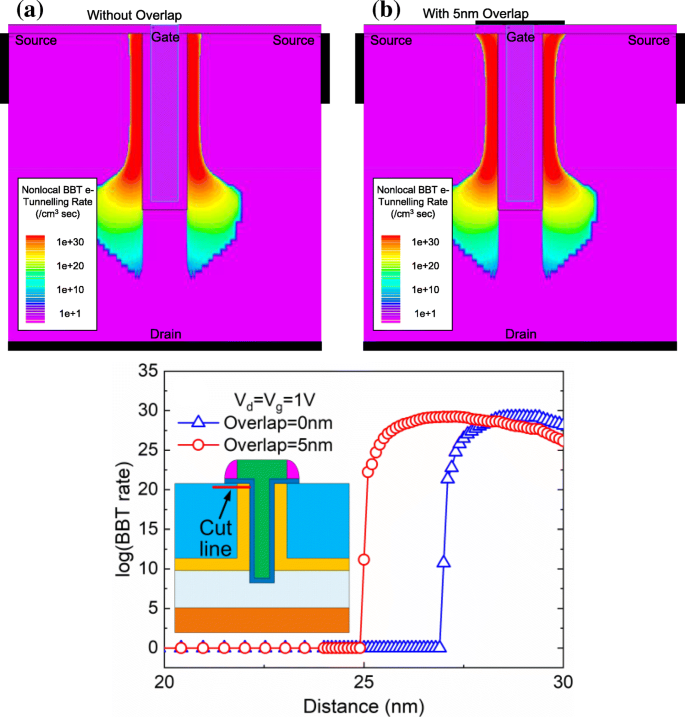

Figure 4 illustrates the BTBT rate for TGTFET with and without a 5‑nm gate overlap. The overlap expands the tunneling area, directly translating to higher I_ON.

Simulated BBT electron tunneling rate diagrams of a device without gate overlap, b device with 5‑nm gate overlap, and c the BBT electron tunneling rate of two devices, at 1 nm below the device surface; V_g = V_d = 1 V

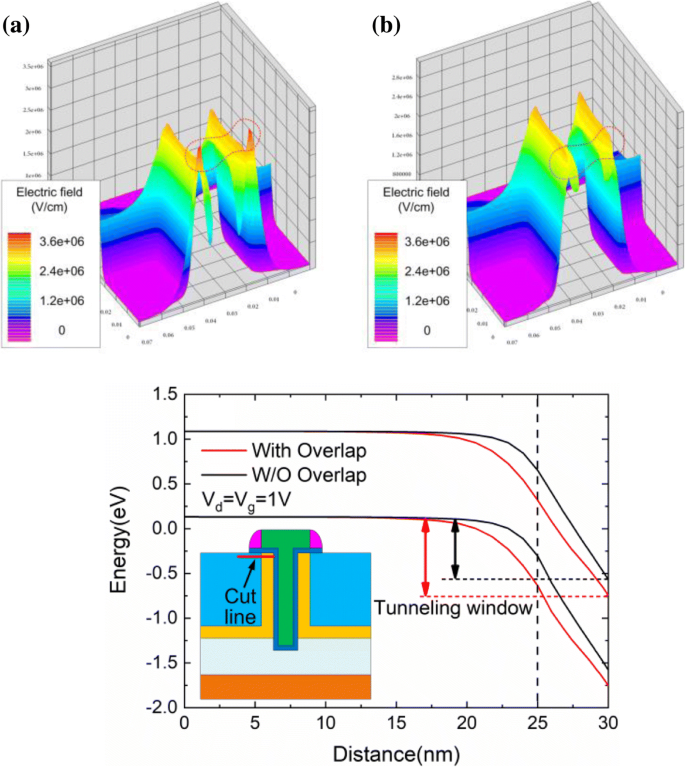

Figure 5 presents 3D electric‑field maps. With a 5‑nm overlap, two pronounced field peaks appear, absent in the overlap‑free case. The associated band‑structure, shown in Fig. 5c, reveals a larger tunneling window, explaining the increased BTBT rate and I_ON.

3D schematic diagram of electric fields of the device a with overlap and b without overlap; simulated c energy band diagrams from source to pocket region (1 nm below the oxide interface)

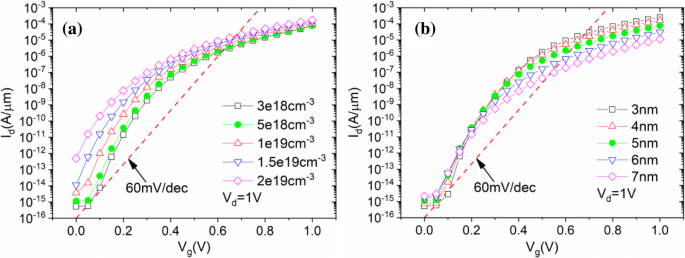

Figure 6 explores the influence of the n⁺ pocket. Increasing pocket doping sharply raises I_OFF (Fig. 6a). Reducing pocket thickness from 7 to 3 nm at a fixed doping of 5 × 10¹⁸ cm⁻³ improves SS and I_ON (Fig. 6b) without significant sub‑threshold leakage, indicating that a lighter pocket doping suppresses off‑state BTBT.

Simulated drain currents with different n⁺ pocket a concentrations and b thicknesses at V_d = 1 V

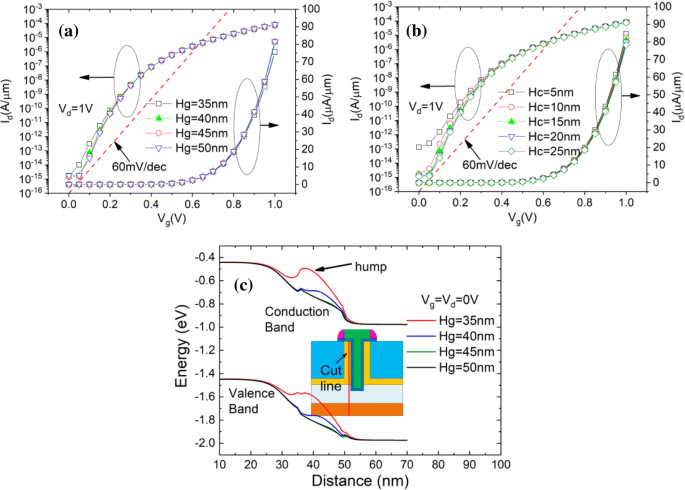

Figure 7 examines gate height (H_g) and channel thickness (H_c). A modest increase in H_g mitigates an energy‑band hump that impedes electron transport (Fig. 7c), enhancing I_ON and SS. Decreasing H_c slightly improves I_ON (Fig. 7b), but further reduction to 5 nm triggers severe sub‑threshold leakage (Fig. 8), as the corner BTBT current dominates.

Simulated transfer characteristics of TGTFET with a different H_g, b different H_c, and c the conduction band hump on the current path

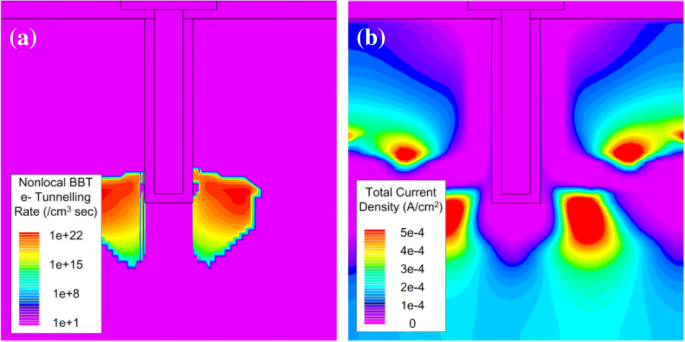

Simulated diagrams of off‑state a BTBT electron tunneling rate and b current density when H_c = 5 nm

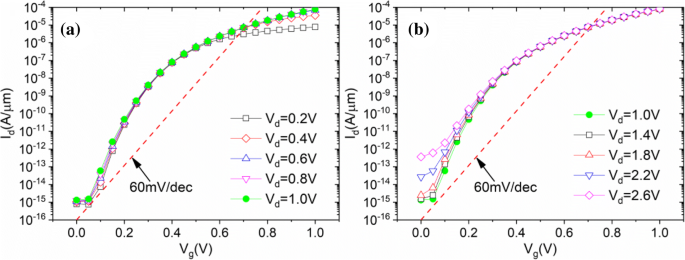

Figure 9 investigates drain‑to‑source voltage (V_d). For V_d < 0.6 V, I_ON rises sharply with V_d due to reduced channel resistance. Above 1.8 V, I_ON saturates while I_OFF escalates because corner BTBT is intensified. In the intermediate range (0.6–1.8 V), the TGTFET demonstrates robust, stable performance and strong DIBL immunity.

Simulated drain currents for a V_d ≤ 1 V and b V_d ≥ 1 V

Analog/RF Performance of TGTFET, UTFET, and LTFET

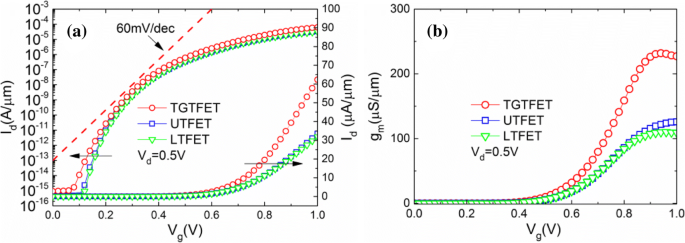

Figure 10 displays the transfer curves and transconductance (gₘ) of the three devices at V_d = 0.5 V. TGTFET achieves a peak gₘ of 232 µS/µm—nearly double that of UTFET (120 µS/µm) and LTFET (110 µS/µm)—thanks to the dual‑source and gate overlap.

a Transfer characteristics and b transconductance curves of TGTFET, UTFET, and LTFET at V_d = 0.5 V

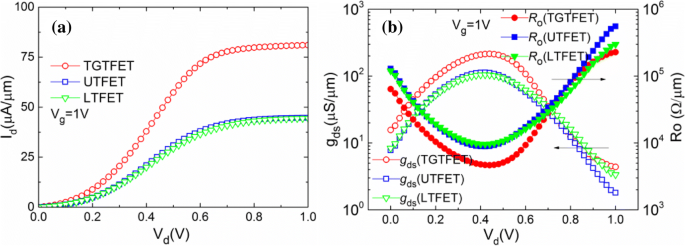

Figure 11 illustrates output characteristics, output conductance (g_ds), and output impedance (R_o). TGTFET’s output current doubles that of UTFET and LTFET, and its g_ds peaks at 214 µS/µm with R_o = 4.6 kΩ/µm at V_d = 0.45 V. The non‑linear R_o vs. V_d behavior arises from the interplay between thermal‑excitation across the drain barrier and tunneling‑limited conduction, a phenomenon previously reported in TFET literature.

a Output characteristics, b output conductance (g_ds), and c output impedance (R_o) curves of TGTFET, UTFET, and LTFET

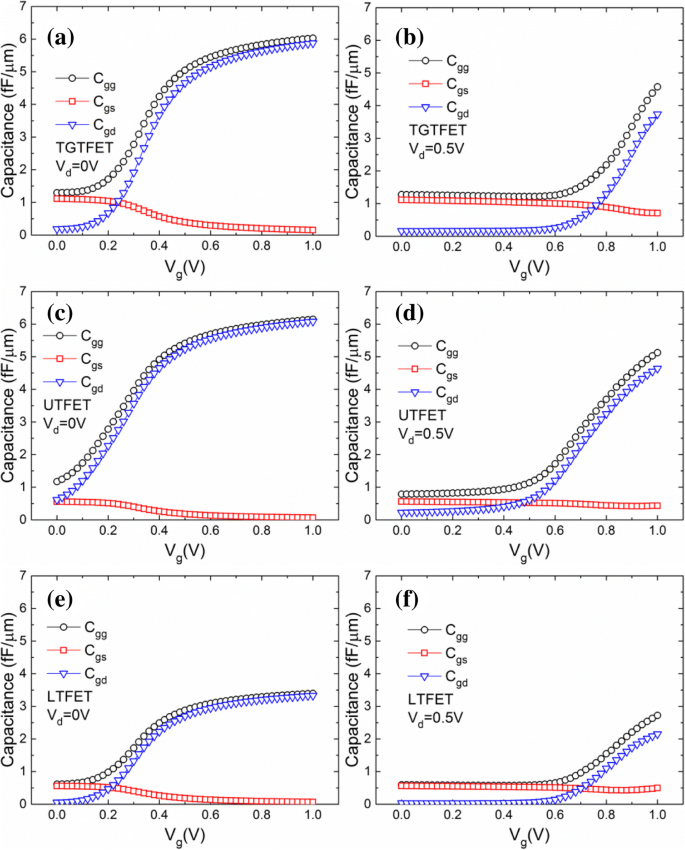

Capacitance analysis (Fig. 14) shows that C_gs remains negligible compared to C_gd; thus, the total gate capacitance (C_gg) is dominated by C_gd. Under V_d = 0 V, C_gg rises sharply with V_g due to electron accumulation in the channel. With V_d = 0.5 V, C_gd remains flat until V_g exceeds 0.6 V, reflecting limited electron capture in the channel at low gate bias.

Capacitance of TGTFET versus V_g under a V_d = 0 V and b V_d = 0.5 V. Capacitance of UTFET versus V_g under c V_d = 0 V and d V_d = 0.5 V. Capacitance of LTFET versus V_g under e V_d = 0 V and f V_d = 0.5 V

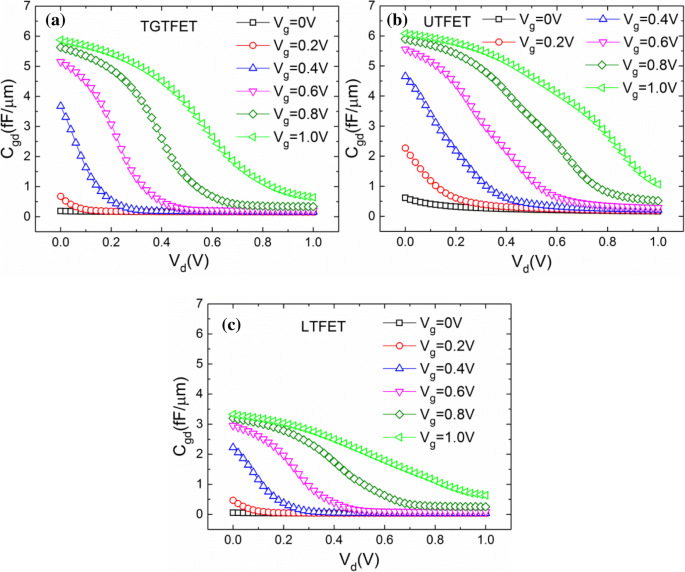

Figure 15 confirms that C_gd for all three devices decreases with increasing V_d at a fixed V_g, while rising with V_g at a fixed V_d.

C_gd characteristics of a TGTFET, b UTFET, and c LTFET versus V_d under different V_g

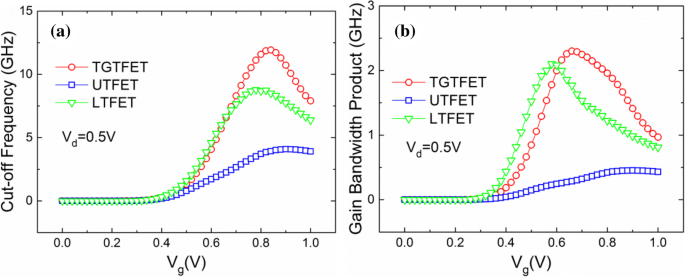

Cut‑off frequency (f_T) and gain bandwidth product (GBW) are computed via f_T = gₘ/(2πC_gg) and GBW = gₘ/(2π10C_gd). Figure 16 shows that TGTFET achieves f_T = 11.9 GHz and GBW = 2.3 GHz at V_d = 0.5 V—outperforming UTFET (4.1 GHz, 0.5 GHz) and LTFET (8.7 GHz, 2.1 GHz). The superior frequency response stems from the dual‑source architecture and reduced C_gg.

The characteristic curves of a f_T and b GBW of TGTFET, UTFET, and LTFET versus V_g at V_d = 0.5 V

Conclusions

We have introduced a silicon‑based TGTFET featuring a T‑shaped gate and dual‑source architecture. This configuration doubles the tunneling junction area and, via gate overlap, sharpens the electric field, yielding I_ON = 8.1 × 10⁻⁵ A/µm, I_ON/I_OFF = 6.7 × 10¹⁰, and SS_min = 24.4 mV/dec. The device demonstrates strong DIBL resilience and maintains performance across a broad V_d range. Analog/RF analysis shows gₘ = 232 µS/µm, g_ds = 214 µS/µm, C_gg ≈ 3.7 fF/µm, f_T = 11.9 GHz, and GBW = 2.3 GHz—outperforming both UTFET and LTFET. These results confirm that the TGTFET is a promising candidate for future low‑power and high‑frequency applications.

Abbreviations

- C gd :

Gate to drain capacitance

- C gs :

Gate to source capacitance

- f T :

Cut‑off frequency

- GBW:

Gain bandwidth

- g ds :

Output conductance

- g m :

Transconductance

- Hc:

Height of the channel layer

- Hg:

Height of the gate electrode

- Hs:

Height of the source layer

- LTFET:

L‑shaped gate tunnel field‑effect transistor

- N D :

Doping concentration of n⁺ drain

- N P :

Doping concentration of n⁺ pocket

- N S :

Doping concentration of p⁺ source

- N sub :

Doping concentration of p⁻ substrate

- R o :

Output impedance

- TGTFET:

T‑shaped gate dual‑source tunnel field‑effect transistor

- Tox:

Thickness of the HfO₂ gate dielectric

- Tp:

Thickness of n⁺ pocket

- UTFET:

U‑shaped gate tunnel field‑effect transistor

- V d :

Drain to source voltage

- V g :

Gate to source voltage

- Wg:

Width of the gate electrode

Nanomaterials

- Understanding Junction Field-Effect Transistors (JFETs): Gate Current Direction & N‑Channel vs P‑Channel

- Transistors: IGFET (MOSFET) – Depletion & Enhancement Modes Explained

- Junction Field‑Effect Transistors (JFET): Design, Operation, and Advanced Variants

- Insulated‑Gate Field‑Effect Transistors (MOSFETs) – Design, Operation, and Power Variants

- Using a Junction Field‑Effect Transistor (JFET) as a Low‑Power On/Off Switch

- SnSe₂ Field‑Effect Transistor Achieves 10⁴ On/Off Ratio and Polarity‑Switchable Photoconductivity

- Magnetic Graphene Field‑Effect Transistor Biosensor for Ultra‑Sensitive Single‑Strand DNA Detection

- Ultra‑Low‑Voltage 2D MoS2 Ferroelectric Memory Transistor with Hf₁₋ₓZrₓO₂ Gate for CMOS Compatibility

- Step-Thickness Design Boosts DG TFET Efficiency: A Simulation Study

- ZrOx-Based Negative Capacitance FET Delivers Sub‑60 mV/dec Subthreshold Swing