Asynchronous Flip‑Flop Inputs: Preset and Clear Functionality

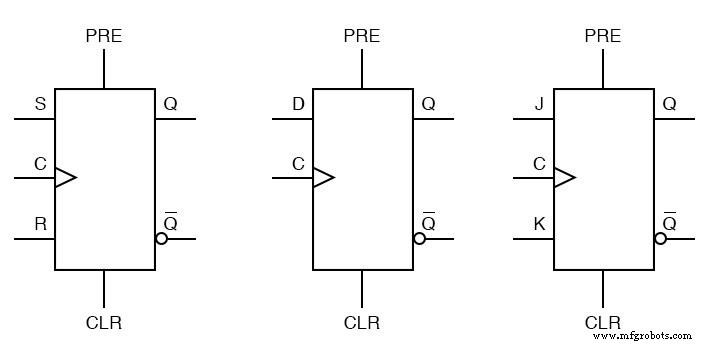

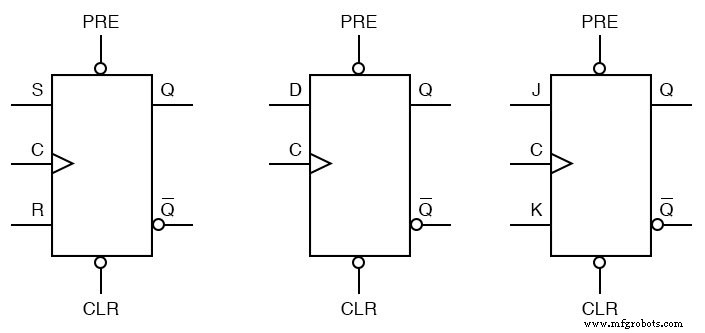

In digital design, the primary data inputs of a flip‑flop—whether D, SR, or JK—are termed synchronous because their influence on the outputs (Q and ΔQ) manifests only on a clock edge.

In contrast, the additional inputs we call asynchronous—preset (PRE) and clear (CLR)—can force the flip‑flop to a known state regardless of the clock or any synchronous inputs.

When the preset input is asserted, the flip‑flop immediately sets (Q = 1, ΔQ = 0), bypassing both the clock and any other data inputs. Conversely, asserting clear resets the device (Q = 0, ΔQ = 1). Both operations occur instantaneously, providing a rapid way to initialize or recover a circuit.

If both preset and clear are active simultaneously, the flip‑flop enters an undefined state where Q and ΔQ conflict. This mirrors the classic SR‑latch condition and should be avoided in reliable designs.

These asynchronous controls are invaluable when multiple flip‑flops must be driven in unison—for example, clearing or presetting an entire register file with a single line. They enable rapid, global state changes without waiting for clock transitions.

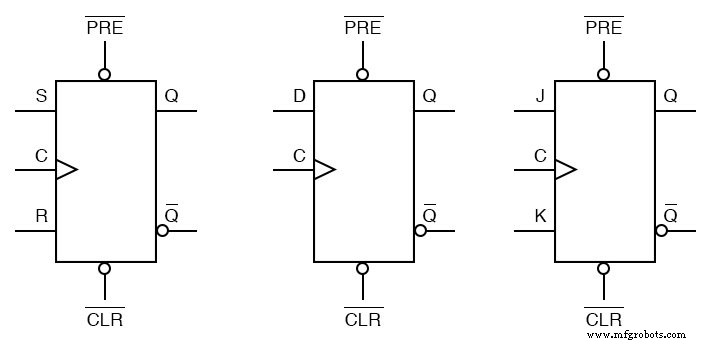

Like their synchronous counterparts, preset and clear can be configured as active‑high or active‑low. An active‑low input is indicated by an inversion bubble on the block diagram, and designers may also see a bar over the PRE or CLR symbols to denote negative logic:

Key Take‑aways

- Asynchronous inputs (PRE and CLR) override the clock and synchronous data to set or reset the flip‑flop instantly.

- When both PRE and CLR are asserted, the device enters an invalid state; careful design must avoid this condition.

- Preset and clear can be implemented as either active‑high or active‑low, with inversion bubbles or bars indicating negative logic.

Related Worksheets

Industrial Technology

- Building a NAND‑Based Set‑Reset Flip‑Flop Circuit

- Understanding the J‑K Flip‑Flop: Design, Logic, and Applications

- Designing an Asynchronous Four‑Bit Up Counter with J‑K Flip‑Flops

- Mastering Asynchronous Reset Synchronization in ASICs and FPGAs

- Synchronizing Asynchronous Resets in ASICs and FPGAs: Challenges, Best Practices, and Advanced Solutions

- Lanner Unveils NCR‑1510: Fanless, Wide‑Temperature SD‑WAN Appliance with Six Antenna Inputs

- Measure Analog Sensors on Raspberry Pi Without Native ADC

- Designing a D Flip-Flop with Asynchronous Active-Low Reset

- Mastering Arduino Analog Inputs: A Step‑by‑Step Video Guide

- The 74LS74 Dual Flip-Flop: Complete Reference and Pinout