Software‑Driven Power Analysis: Optimizing Semiconductor Design for Efficiency

Power is the single largest cost driver in semiconductor design. A chip that consumes more energy requires larger, more expensive batteries for portable devices, higher‑grade cooling solutions, and more robust power‑distribution systems. These additional components drive up manufacturing costs, shrink profit margins, and can impede market success. Even wall‑powered systems—servers, storage arrays, and networking gear—pay huge operational bills; in some data centers power costs surpass the hardware value over the equipment’s lifetime. At extreme power levels, liquid cooling and other sophisticated infrastructure become mandatory, further inflating capital and operational expenses. Consequently, reducing average power consumption is a universal objective, while curbing peak power is often a critical requirement to prevent thermal failure.

Challenges of Power Analysis

To meet these goals, the industry employs a spectrum of low‑power techniques, from circuit‑level optimizations to application‑aware software‑based power management. However, evaluating the real impact of these measures demands accurate estimates of both average and peak power during the design and verification stages. Relying on post‑fabrication data is unacceptable; the product may already be unviable or irreparably damaged. Therefore, robust pre‑silicon power analysis—ideally at multiple project milestones—is essential.

Traditional electronic‑design‑automation workflows use simulation for functional verification. Testbenches run a suite of checks that exercise specific features, generating switching‑activity files for power‑signoff tools. These tools combine the activity data with technology‑library power models to produce estimates of average and peak consumption. The accuracy of this approach hinges entirely on the representativeness of the simulation tests. Functional verification suites are purposely focused and rarely capture the full breadth of real‑world workloads. Constrained‑random tests may increase parallel activity but still fall short of realistic usage patterns. The only truly reliable source of switching activity comes from running production software—including operating systems and user applications—on the design.

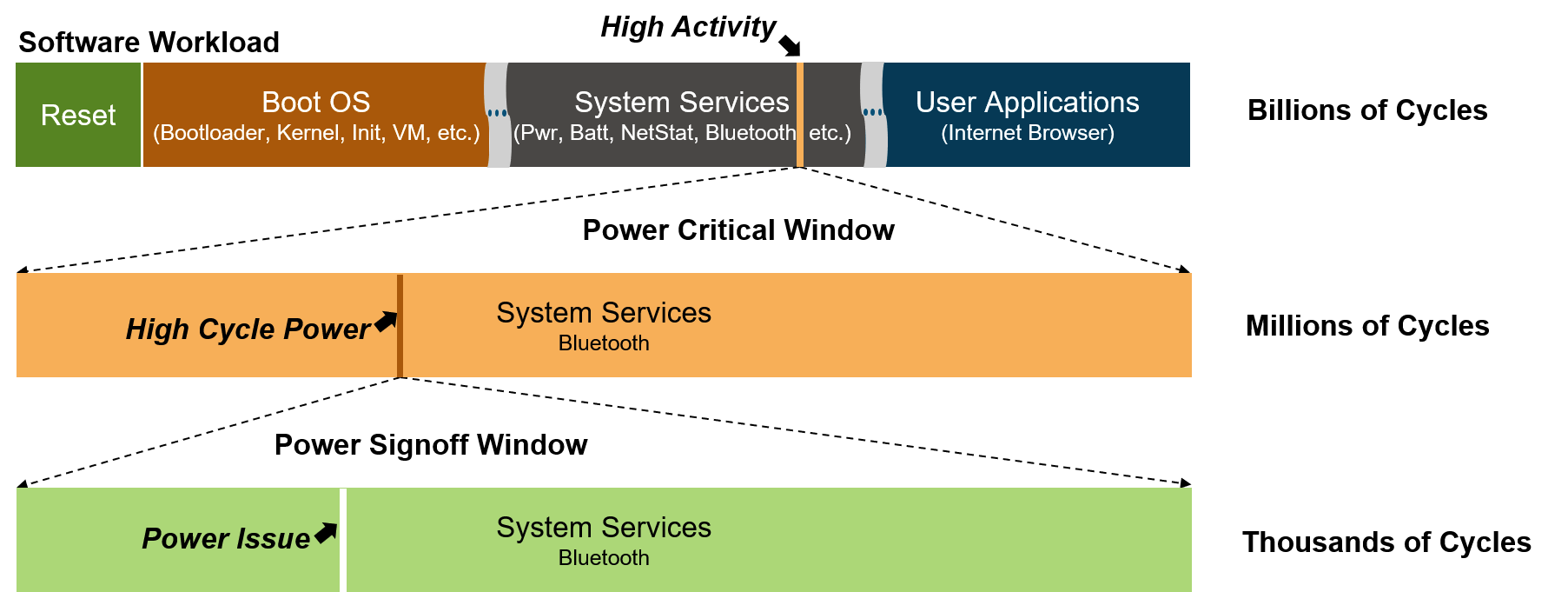

Running a full operating‑system boot and multiple applications in simulation would require billions of clock cycles, which is impractical. Emulators, on the other hand, routinely execute billions of cycles from OS boot to user workloads. Emulation delivers the necessary real‑software activity, but conventional power‑signoff tools are designed for thousands, not millions or billions, of cycles. A new methodology is required to extract meaningful windows of high activity from the emulation run and focus power analysis on those segments (see Figure 1).

click for larger image

Figure 1. Power analysis using power windows (Source: Synopsys)

Moving to Software‑Driven Power Analysis

The flow illustrated in Figure 1 begins with the emulator generating an activity profile that highlights which parts of the design are active over time. This profile can be viewed as a waveform or in any hardware debug tool. Because power‑signoff cannot be performed on billions of cycles, users must identify one or more critical windows—segments where activity, and thus power consumption, is highest. If each window spans millions of cycles, it can be used for precise power analysis. As a benchmark, the emulator should produce a one‑billion‑cycle activity profile in roughly three hours.

Embedded

- Power Sources: AC and DC Explained

- Silicon Labs Launches Power‑Efficient Wi‑Fi Modules, Halving Energy Use for IoT Devices

- Maxim Integrated Launches Three Low‑Power Analog ICs to Drive Efficiency in Edge and Cloud Applications

- AMS Launches AS621x Series: Ultra‑Low‑Power, High‑Accuracy Temperature Sensors in a Tiny Package

- Lattice CrossLink‑NX FPGA: 75% Lower Power, 10× Smaller, 100× More Reliable for Edge AI

- MAX77654 SIMO PMIC: 50% Smaller Design, 20% Longer Battery Life

- Maxim’s MAX31889 & MAX31825: Precision, Low‑Power Temperature Sensors for Cold‑Chain and Multi‑Device Systems

- Harnessing Pareto Analysis to Optimize Maintenance Efficiency

- Understanding Reactive Power: Key Insights for Power System Reliability

- Power & Energy Calculator – Precise kWh Estimation Tool