Leveraging NXP i.MX RT500 for DSP-Enabled Smart Devices: Multi-Threading, XOS, and Cadence Fusion F1 Audio DSP

Explore multi-threading, XOS RTOS, semaphore-based resource sharing, and how NXP’s i.MX RT500 MCU enables DSP‑powered smart devices.

Today’s consumer electronics demand components that can process vast amounts of data with speed and efficiency. Microcontrollers that integrate highly optimized digital signal processors are essential for security, voice, and image applications.

This article highlights the Cadence® Tensilica® Fusion F1 audio processor—an autonomous co‑processor that partners with the i.MX RT500’s Cortex‑M33 cores to deliver high‑performance signal‑processing workloads.

Core Concepts of Multi‑Threaded Programs

Modern processors give the impression of running multiple threads concurrently, yet a single CPU core executes one thread at a time. When the thread count exceeds core availability, an operating system must schedule the tasks.

The OS tracks every thread’s state, allocating CPU time slices so that applications appear to run in parallel while maintaining fairness.

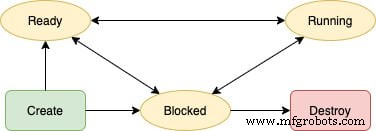

Figure 1. Thread lifecycle states

The scheduler maintains three queues: ready, blocked, and running. It considers thread priorities, blocking events (e.g., I/O, interrupts), and the need for preemption. Choosing an appropriate scheduling strategy is critical for real‑time workloads.

Conditions and Events in XOS

XOS allows developers to define conditions that block a thread until a user‑defined predicate becomes true. Events, represented as bit masks, enable multiple threads or interrupt handlers to synchronize simultaneously.

Interrupts in XOS

XOS supports fast, customizable interrupt handling, including nested interrupts—where a higher‑priority interrupt temporarily suspends a lower‑priority one. The system automatically resumes the interrupted service once the higher level completes.

Threads also benefit from timed delays and periodic callbacks. The DSP co‑processor offers up to three internal timers that developers can configure as needed.

Understanding Semaphores

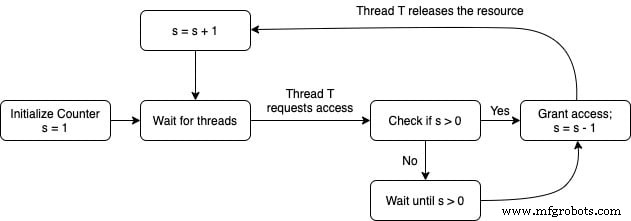

Semaphores coordinate access to shared resources. They maintain an internal counter reflecting how many threads may concurrently enter a critical section. When the counter reaches zero, waiting threads block until the resource becomes available again.

Figure 2. Semaphore workflow diagram

An Overview of the i.MX RT500 MCU and the DSP

The i.MX RT500 series features dual Cortex‑M33 cores running up to 275 MHz, with up to 5 MB of SRAM. Security is reinforced by Arm TrustZone, an MPU with eight regions, and the CASPER crypto co‑processor for hardware‑accelerated asymmetric algorithms.

Power‑management options let designers fine‑tune consumption to match application needs. Dedicated accelerators—including the Cadence® Tensilica® Fusion F1 audio DSP, a 2D GPU, and multiple display interfaces—enable secure, low‑power operation in HMI, IoT, hearables, and voice assistants.

A Look at the Audio DSP

The Fusion DSP runs up to 200 MHz and features a hardware floating‑point unit, making it ideal for always‑on voice‑triggered devices. It bundles pre‑processing and post‑processing modules for a wide range of audio codecs.

It shares the MCU’s SRAM for data exchange, respecting memory protection boundaries for secure access.

Programming with the DSP in Mind

Tensilica DSPs are compatible with FreeRTOS®, Zephyr®, Linux®, and XOS. Cadence’s XOS kernel, written in standard C, offers task scheduling, adaptive context switching, synchronization primitives, and robust interrupt handling—all tailored for Xtensa processors.

Meeting Smart Consumer Device Requirements

With its blend of core performance, security, and specialized accelerators, the i.MX RT500 empowers engineers to deliver the next generation of smart, always‑on consumer devices.

For deeper insights, consult NXP’s application note AN13159, which details supported APIs, XOS condition and event examples, and more. NXP’s website also hosts training materials—videos, webinars, and documentation—to help developers get started.

Industry Articles are a form of content that allows industry partners to share useful news, messages, and technology with All About Circuits readers in a way editorial content is not well suited to. All Industry Articles are subject to strict editorial guidelines with the intention of offering readers useful news, technical expertise, or stories. The viewpoints and opinions expressed in Industry Articles are those of the partner and not necessarily those of All About Circuits or its writers.

Embedded

- CEVA-BX: A Unified DSP/MCU Processor for Next‑Gen IoT, Automotive, and Industrial Applications

- When a DSP Outperforms a Hardware Accelerator

- Choosing Between Hardware Accelerators and DSPs: A Practical Guide

- Mastering UART: The Universal Asynchronous Receiver/Transmitter Explained

- Mastering ADC Code Error Rates: What You Need to Know

- NXP Unveils Ultra‑Low‑Power Bluetooth MCUs with Integrated NFC for Smart Connectivity

- Mastering Power Management with NXP i.MX RT500 Crossover MCUs

- Deploying Handwritten Digit Recognition on the i.MX RT1060 MCU Using TensorFlow Lite

- Mastering DSP Handle Usage: Key Guidelines for Optimal Performance

- Decoding Tooling Costs in Custom Investment Casting: A Practical Guide