Successive Approximation ADC – A Faster, Accurate Digital-to-Analog Conversion Method

One effective solution to the limitations of a digital ramp ADC is the successive‑approximation ADC. The core innovation lies in a specialized counter called the successive‑approximation register (SAR).

Rather than incrementing through a binary sequence from zero to full scale, the SAR sets each bit starting with the most‑significant bit (MSB) and moving to the least‑significant bit (LSB). During this process it continuously monitors the comparator’s output, adjusting each bit to ensure the DAC output converges on the analog input as quickly as possible.

Think of it as a trial‑and‑fit approach, similar to converting decimal to binary: you test each bit value from MSB to LSB until the resulting binary number matches the input. Because the SAR takes larger, well‑defined steps, the conversion completes in far fewer iterations than a simple 0‑to‑full count, resulting in a markedly faster and more efficient ADC.

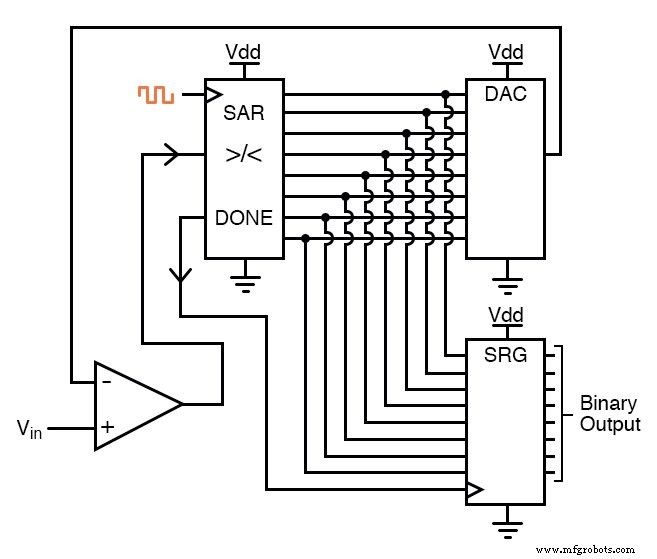

Below is a schematic of a typical SAR‑based ADC. Note that the SAR can output the binary result serially—one bit at a time—so a separate shift register is unnecessary.

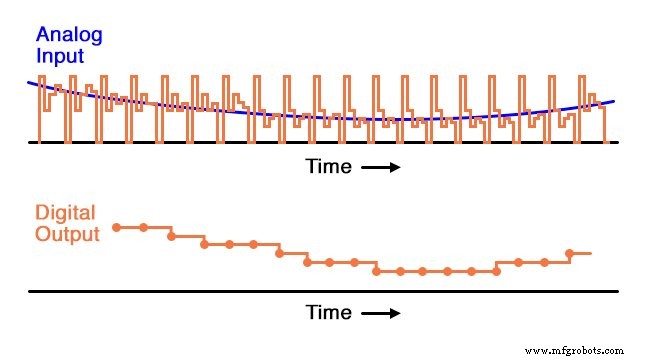

When plotted over time, the operation of a successive‑approximation ADC shows regular, predictable updates, unlike the irregular intervals seen in a digital ramp ADC.

RELATED WORKSHEET:

- Successive Approximation ADC Worksheet

Industrial Technology

- Serial‑In, Parallel‑Out Shift Registers: Converting Serial Data to Parallel for Efficient I/O Expansion

- Flash ADC (Parallel Analog‑to‑Digital Converter) – Design, Operation, and Applications

- Digital Ramp (Counter) ADC: Operation, Benefits, and Limitations

- Tracking ADC: Up/Down Counter for Fast, Continuous Signal Conversion

- Integrating (Single‑Slope) ADCs: Principles, Advantages, and Dual‑Slope Alternatives

- Delta‑Sigma ADC: Harnessing Oversampling for Precise Analog‑to‑Digital Conversion

- Key ADC Design Factors: Resolution, Sampling, and Practical Performance

- From Ritty’s Invention to Modern POS: The Evolution of Cash Registers

- Mastering ADC Code Error Rates: What You Need to Know

- Verilog N‑bit Bidirectional Shift Register – Design and Implementation