Digital Ramp (Counter) ADC: Operation, Benefits, and Limitations

Often called a stairstep‑ramp or simply a counter ADC, the digital ramp converter is conceptually straightforward but has inherent performance constraints.

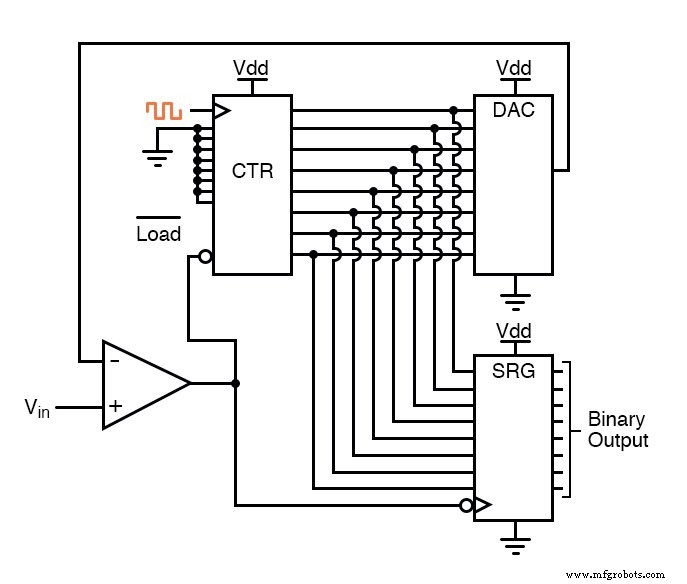

The core idea is to feed a free‑running binary counter into a digital‑to‑analog converter (DAC), then compare the DAC’s analog output with the signal to be digitized. The comparator’s output controls when the counter stops and resets, effectively “locking in” the digital value that matches the input voltage.

With each clock pulse, the counter increments and the DAC raises its voltage in discrete steps. The comparator continuously monitors whether the DAC output has surpassed the analog input.

If the input voltage is higher than the DAC’s output, the comparator remains high and the counter keeps counting. Once the DAC voltage exceeds the input, the comparator flips low.

Two events then occur: the low transition “locks” the current counter value into the shift register, providing the ADC’s digital output; and the counter receives an active‑low LOAD signal, resetting it to zero on the next clock edge.

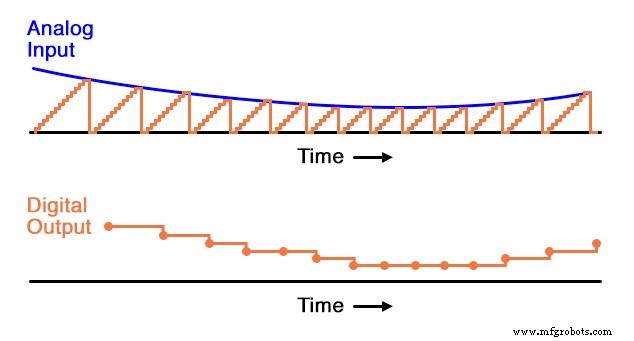

Thus the ADC produces a staircase of DAC outputs that climbs until it reaches the input level, captures the corresponding binary code, and restarts the cycle. A time‑domain illustration is shown below:

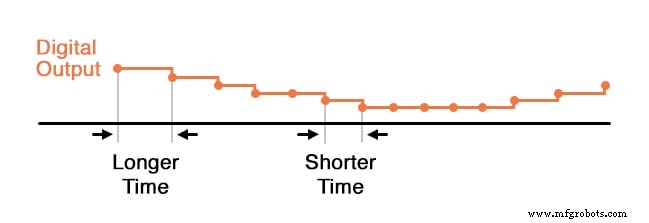

Notice how the interval between successive updates varies with the input amplitude: lower signals generate more frequent updates, while higher signals produce longer gaps.

In many real‑world applications, this variable sampling period is unacceptable. Moreover, the necessity of counting from zero for every conversion cycle imposes a fundamental speed limit, making the digital‑ramp ADC less competitive than alternative counter‑based architectures.

Despite these drawbacks, the simplicity of the digital‑ramp design keeps it useful in cost‑sensitive or educational contexts where high resolution is more critical than maximum throughput.

Industrial Technology

- Digital Logic with Feedback: From Deterministic Gates to Multivibrators

- Synchronous Binary Counters: Design, Up/Down Operation, and Encoder Applications

- Counter Modulus: Optimized Algorithms for Modern Systems

- Ring Counters and Johnson Counters: Design, Operation, and Practical Applications

- Flash ADC (Parallel Analog‑to‑Digital Converter) – Design, Operation, and Applications

- Digital Ramp (Counter) ADC: Operation, Benefits, and Limitations

- Tracking ADC: Up/Down Counter for Fast, Continuous Signal Conversion

- Integrating (Single‑Slope) ADCs: Principles, Advantages, and Dual‑Slope Alternatives

- Delta‑Sigma ADC: Harnessing Oversampling for Precise Analog‑to‑Digital Conversion

- Siemens Boosts U.S. Digital Capabilities with $175M R&D Investment