Mastering Concurrent Statements in VHDL: A Practical Guide

A concurrent statement in VHDL is a signal assignment that sits directly in an architecture, outside any process block. It’s also referred to as a concurrent assignment or concurrent process.

When you write a concurrent statement, you are effectively creating a process that is automatically sensitive to every signal that appears on the right‑hand side of the assignment. In other words, a concurrent assignment is syntactic sugar for a process with a full sensitivity list.

This shorthand is especially handy when you want to implement simple combinational logic that drives a single signal. Instead of spelling out a full process construct with a sensitivity list, you can assign directly to the target signal in the architecture body.

This tutorial is part of the Basic VHDL Tutorials series.

When used correctly, the intent of the code remains crystal clear—no need to clutter the design with a process for every single bit you want to toggle.

Exercise

In this video we learn how to create a concurrent statement:

The final code we created in this tutorial:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T13_ConcurrentProcsTb is

end entity;

architecture sim of T13_ConcurrentProcsTb is

signal Uns : unsigned(5 downto 0) := (others => '0');

signal Mul1 : unsigned(7 downto 0);

signal Mul2 : unsigned(7 downto 0);

signal Mul3 : unsigned(7 downto 0);

begin

process is

begin

Uns <= Uns + 1;

wait for 10 ns;

end process;

-- Process multiplying Uns by 4

process is

begin

Mul1 <= Uns & "00";

wait on Uns;

end process;

-- Equivalent process using sensitivity list

process(Uns) is

begin

Mul2 <= Uns & "00";

end process;

-- Equivalent process using a concurrent statement

Mul3 <= Uns & "00";

end architecture;

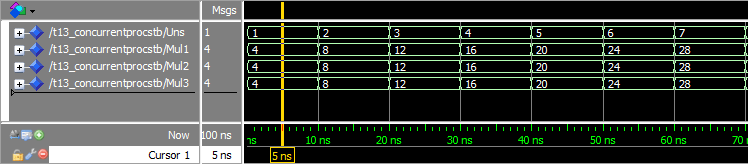

The waveform window in ModelSim after we pressed run, and zoomed in on the timeline:

We can see from the waveform that Mul1, Mul2, and Mul3 behave exactly the same. This confirms that a concurrent statement and the two processes we wrote are fully equivalent.

A concurrent statement operates just like a process: all signals that appear on the right‑hand side of the <= are implicitly added to its sensitivity list. Consequently, the signal on the left is updated whenever any of those evaluated signals change.

In this example we multiplied the Uns signal by 4 using a left bit‑shift. All our signals are of the unsigned type, so the compiler treats them as numeric values. Appending two zero bits to the right of a binary number is equivalent to multiplying it by 4.

Takeaway

- A concurrent statement is a signal assignment placed directly in the architecture.

- It is functionally identical to a process with all right‑hand‑side signals on its sensitivity list.

Proceed to the next tutorial »

VHDL

- Creating String Lists in VHDL: Best Practices & Example

- Implementing a PWM Controller in VHDL: Design, Simulation, and FPGA Demo

- Leveraging In‑Process Procedures for Cleaner VHDL FSM Design

- Designing a Finite‑State Machine in VHDL: A Practical Traffic Light Example

- Build a Reliable Timer in VHDL: Counting Clock Cycles to Hours

- Building a Clock‑Triggered Process in VHDL: A Practical Guide

- Mastering the Case-When Statement in VHDL: Efficient Multiplexer Design

- Mastering std_logic_vector: Creating Signal Vectors in VHDL

- Using Sensitivity Lists in VHDL Processes for Reliable RTL Design

- Your First VHDL Program: A Step‑by‑Step Hello World Tutorial