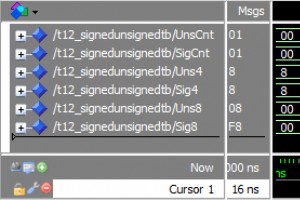

In VHDL, signed and unsigned are specialized bit vectors that let you perform arithmetic on data buses. Unlike std_logic_vector, which is ideal for routing signals but not for calculations, these types are interpreted as numeric values by the compiler. Attempting to add a std_logic_vector will trigg

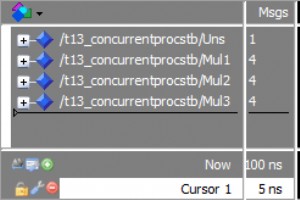

A concurrent statement in VHDL is a signal assignment that sits directly in an architecture, outside any process block. It’s also referred to as a concurrent assignment or concurrent process. When you write a concurrent statement, you are effectively creating a process that is automatically sensitiv

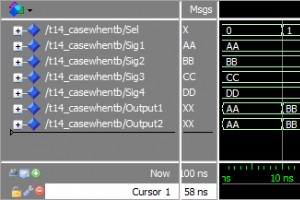

The Case-When statement directs a VHDL program along one of several paths based on a signal, variable, or expression. It offers a cleaner, more readable alternative to lengthy if-then-elsif-else chains, particularly when handling multiple discrete values. Many programming languages use constructs li

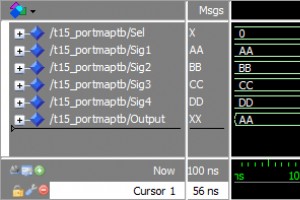

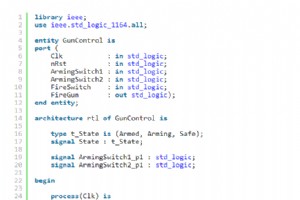

In VHDL, a module is a self‑contained unit that communicates with the external world through its entity. The port map clause of an instantiation connects the entity’s formal ports to signals in the surrounding design. Modules, Entities, and Testbenches When we develop for an FPGA or ASIC, the design

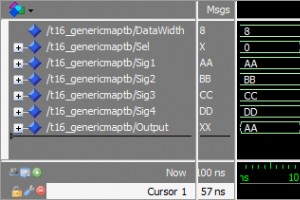

Creating reusable modules is a cornerstone of efficient VHDL design, yet minor variations often demand duplicate code. Generics and generic maps solve this by allowing you to configure a module’s parameters at compile‑time, keeping your code DRY and maintainable. Constants help avoid hard‑coding the

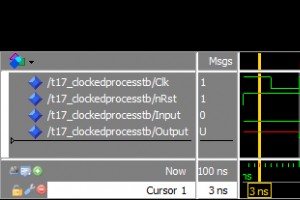

The majority of VHDL designs employ clocked logic—commonly referred to as synchronous or sequential logic. A clocked process activates solely on the master clock’s edge, regardless of changes in other input signals. The fundamental element of clocked logic is the flip‑flop. In this tutorial we focus

Complete tutorials 12‑17 of the Basic VHDL Tutorial series and test your knowledge with this targeted quiz. Which statement is true about the signed type? They can represent higher values than unsigned types If the leftmost bit is 1 the value must be negative Overflow is a runtime error - Con

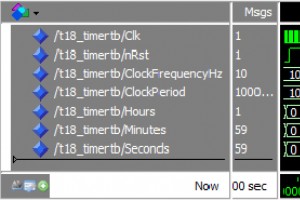

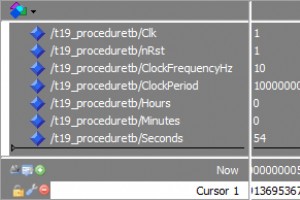

In earlier tutorials we used the wait for statement to delay time in simulation. However, wait for cannot be employed in production designs because a real circuit cannot be instructed to pause. The practical way to measure time in a VHDL module is to count clock cycles. Every digital design has acce

In VHDL, procedures are subprograms that let designers avoid repetitive code blocks. When the same operation is needed in multiple places, creating a full module can be excessive. A procedure offers a lightweight, reusable solution. Procedures may be declared in any declarative region—architecture,

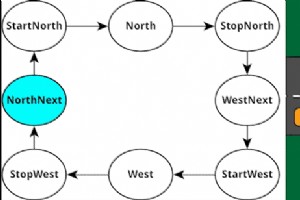

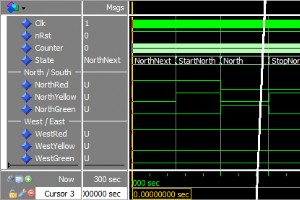

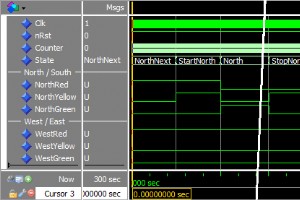

A finite‑state machine (FSM) is a deterministic logic model whose output depends not only on the current input but also on the sequence of past inputs and outputs. In FPGA design and time‑dependent VHDL algorithms, an FSM is the go‑to abstraction for capturing stateful behaviour. FSMs in VHDL are ty

Functions are subprograms in VHDL which can be used for implementing frequently used algorithms. A function takes zero or more input values, and it always returns a value. In addition to the return value, what sets a function apart from a procedure, is that it cannot cont

In VHDL, an impure function can access or modify any signal within its lexical scope, including signals that are not listed as parameters. This capability gives the function side effects—its return value may vary even when the same arguments are supplied, and it may alter external signals that are n

In VHDL, a procedure can drive external signals as long as the signal remains in its scope. While a procedure declared in an architecture has no access to external signals—because those signals are not visible at compile time—a procedure defined inside a process can freely read and write any signal

Test your progress with this VHDL quiz after completing part 4 of the Basic VHDL Tutorial series! How do we measure real-time in VHDL?

A linked list is a dynamic data structure that expands and contracts as elements are added or removed. VHDL’s object‑oriented features—access types, records, and protected types—make it possible to implement this structure cleanly and efficiently. Creating the DataStructures Package We’ll encapsulat

A self‑checking testbench is a VHDL program that verifies the correctness of a device under test (DUT) without manual inspection. Once executed, it automatically reports an OK or Failed status, making it an essential tool for reliable VHDL development. Every VHDL module should have an associated se

An interactive testbench is a simulator setup where input to the device under test (DUT) is provided by an operator while the testbench is running. Most often, this would mean you entering commands in the simulator console to provide the DUT with stimulus. While you shoul

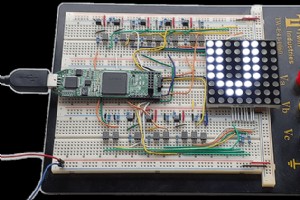

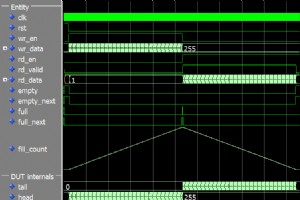

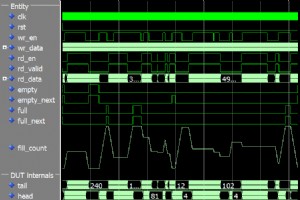

Circular buffers are popular constructs for creating queues in sequential programming languages, but they can also be implemented in hardware. In this article, we will create a ring buffer in VHDL to implement a FIFO in block RAM. There are many design decisions you will

Constrained random verification is a testbench strategy that relies on generating pseudo-random transactions for the device under test (DUT). The goal is to reach functional coverage of a number of predefined events through random interaction with the DUT. Open Source VHD

I’m excited to share that the VHDL and FPGA course I’ve been developing over the past six months is nearing completion. Currently in beta, it will officially launch this autumn. Who Is the Course For? This program is designed for developers who already know other programming languages but are new to

VHDL

Shale Producers Adopt Industry 4.0 Innovations to Enhance Efficiency Amid Price Decline

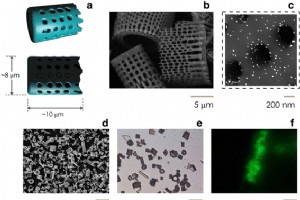

Gold-Functionalized Diatom Frustules: A Hierarchical Nanodevice for Sensitive SERS Detection of Biomolecules and Environmental Pollutants

Optimizing High-Speed PCB Routing to Minimize EMI Impact

DIY Autoranging Capacitance Meter (10 pF–10 µF) – Easy Arduino Build