When I first encountered the AXI interface while designing a module, I was surprised by its streamlined flow‑control approach. Unlike traditional protocols that rely on busy/valid, full/valid, or empty/valid pairs, AXI uses only two signals: ready and valid. What began as frustration quickly became

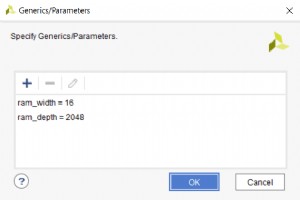

Populating block RAM with predefined values is most efficiently done by reading binary or hexadecimal literals from an ASCII file. This technique also serves to create ROMs, as FPGA ROM is simply a RAM that is only read from. For the examples below, the following constants and RAM type are declared

Reading stimulus data from an external file is a powerful way to control a Device‑Under‑Test (DUT) in VHDL. By scripting a sequence of signal values and simulation times in a plain‑text file, designers can quickly swap test patterns without modifying the testbench logic. This article, the second in

When working with VHDL testbenches, the simplest way to import an image is to use the BMP raster graphics format. BMP files are natively supported by Windows, and they expose raw pixel data without compression, making them ideal for simulation. This article explains how to read a binary BMP file, st

This video is an introductory presentation about FPGA and programmable logic technology. I delivered this 45‑minute talk at an event hosted by 7 Peaks Software in Bangkok, Thailand, on 19 November 2019.Highlights from the presentation:05:07 – Who uses FPGAs?09:06 – What is an FPGA?12:13 – Emulating

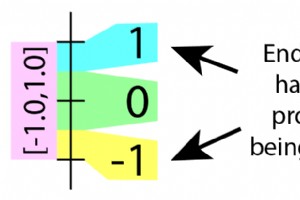

VHDL includes a built‑in pseudo‑random generator that yields floating‑point values in the [0, 1] interval. By scaling and offsetting these values, you can create random data of any type—real, integer, std_logic_vector, or time—suitable for testbenches. The following guide shows how to build these ge

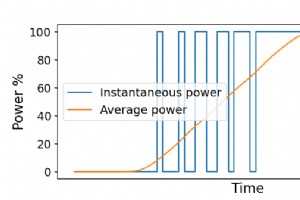

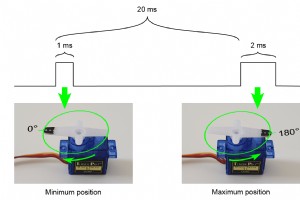

Pulse‑width modulation (PWM) turns a digital FPGA pin into a powerful analog controller. By switching the supply on and off at high speed, PWM delivers the exact average current a device needs, without ever generating a true analog voltage. Typical PWM applications include audio output for speakers,

I’ve noticed that many of the gadgets that I’ve bought the last couple of years have shifted away from LED blinking to led breathing. Most electronic gizmos contain a status LED whose behavior gives away indications of what’s going on inside of the devic

When a VHDL testbench reaches the end of its intended execution, you’ll want the simulator to halt cleanly and, if possible, return control to any calling script. This article reviews the most common and reliable techniques for stopping a simulation across major VHDL simulators, with code examples f

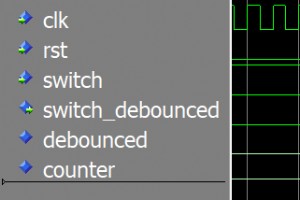

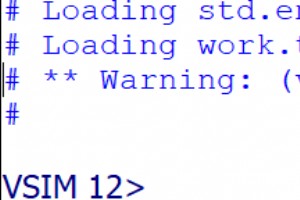

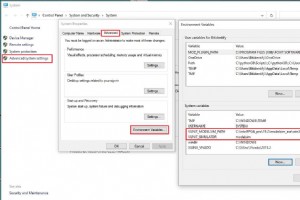

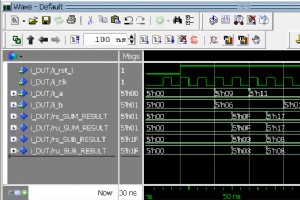

Most VHDL simulators expose the Tool Command Language (Tcl) as their primary scripting interface. When you type a command at the simulator console, you are using Tcl, and you can also write scripts that drive and observe your VHDL design. This article walks you through building a self‑checking testb

Radio‑controlled (RC) servos are the heart of hobbyist aircraft, cars, and boats. They translate a remote radio command into a precise angular position. Because RC systems have been around for decades, the industry‑standard interface is pulse‑width modulation (PWM) rather than a pure digital protoco

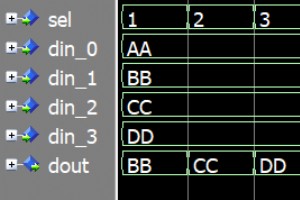

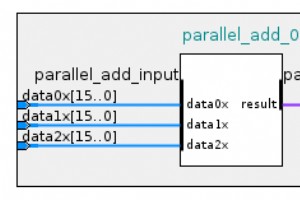

The VHDL generate statement allows designers to automatically replicate a block of code across multiple instances, each wired to distinct signals. Think of it as a compile‑time for loop that can create chained processes or module instances, dramatically reducing boilerplate and improving maintainabi

Text strings in VHDL are generally limited to fixed-length character arrays. That makes sense because VHDL describes hardware, and generic-length strings require dynamic memory. To define an array of strings, you have to allocate space at compile-time for the highest numb

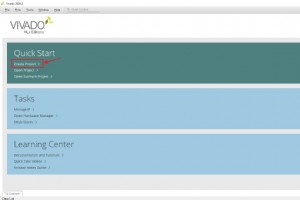

This tutorial walks you through using Xilinx Vivado’s Integrated Logic Analyzer (ILA) and Virtual Input/Output (VIO) cores to debug and monitor VHDL designs on‑chip. By the end you’ll know how to insert probes, configure triggers, and capture precise signal behavior without external equipment. Overv

When designing VHDL for safety‑critical FPGA applications, simply writing testbenches isn’t enough. Engineers must prove that a module behaves exactly as specified, free of hidden side‑effects. Formal verification provides that mathematical assurance. Formal verification bridges the gap between requ

VUnit is a leading open‑source VHDL verification framework that couples a Python test‑suite runner with a dedicated VHDL library. Together they automate testbench compilation, execution, and result reporting, enabling engineers to follow a test‑driven development cycle. In this tutorial, Ahmadmuntha

Have you ever wanted to run a VHDL simulation that includes a Quartus IP core through the VUnit verification framework? That’s what FPGA engineer Konstantinos Paraskevopoulos had in mind, but he couldn’t find a suitable tutorial for it. Fortunately, he used his talent to figure out how and was kind

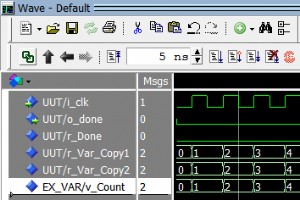

In VHDL, variables behave similarly to C variables: their value is available immediately after an assignment and remains unchanged until the next assignment. This makes them ideal for temporary storage and procedural calculations within a process. Key Rules for Using Variables in VHDL Variables

Digital designers rely on precise arithmetic inside FPGAs and ASICs. A core concept is the distinction between signed and unsigned data types in VHDL. Both types are defined in the numeric_std package from the IEEE library. While many designers still use std_logic_arith, this package is not IEEE‑s

In VHDL, records offer a powerful way to streamline your design, much like structs in C. By grouping related signals into a single type, you can dramatically reduce code duplication, improve readability, and simplify port maps across multiple entities. Records shine when you work with large, recurri

VHDL